MODELO PARA ELABORAÇÃO DE TESTES DE UNIDADES COMPUTACIONAIS

Maria Alice Silveira de Brito Mochel

TESE SUBMETIDA AO CORPO DOCENTE DA COORDENAÇÃO DOS PROGRAMAS DE PÓS-GRADUAÇÃO DE ENGENHARIA DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE MESTRE EM CIÊNCIAS (M.Sc.) EM ENGENHARIA DE SISTEMAS E COMPUTAÇÃO.

Aprovada por:

---

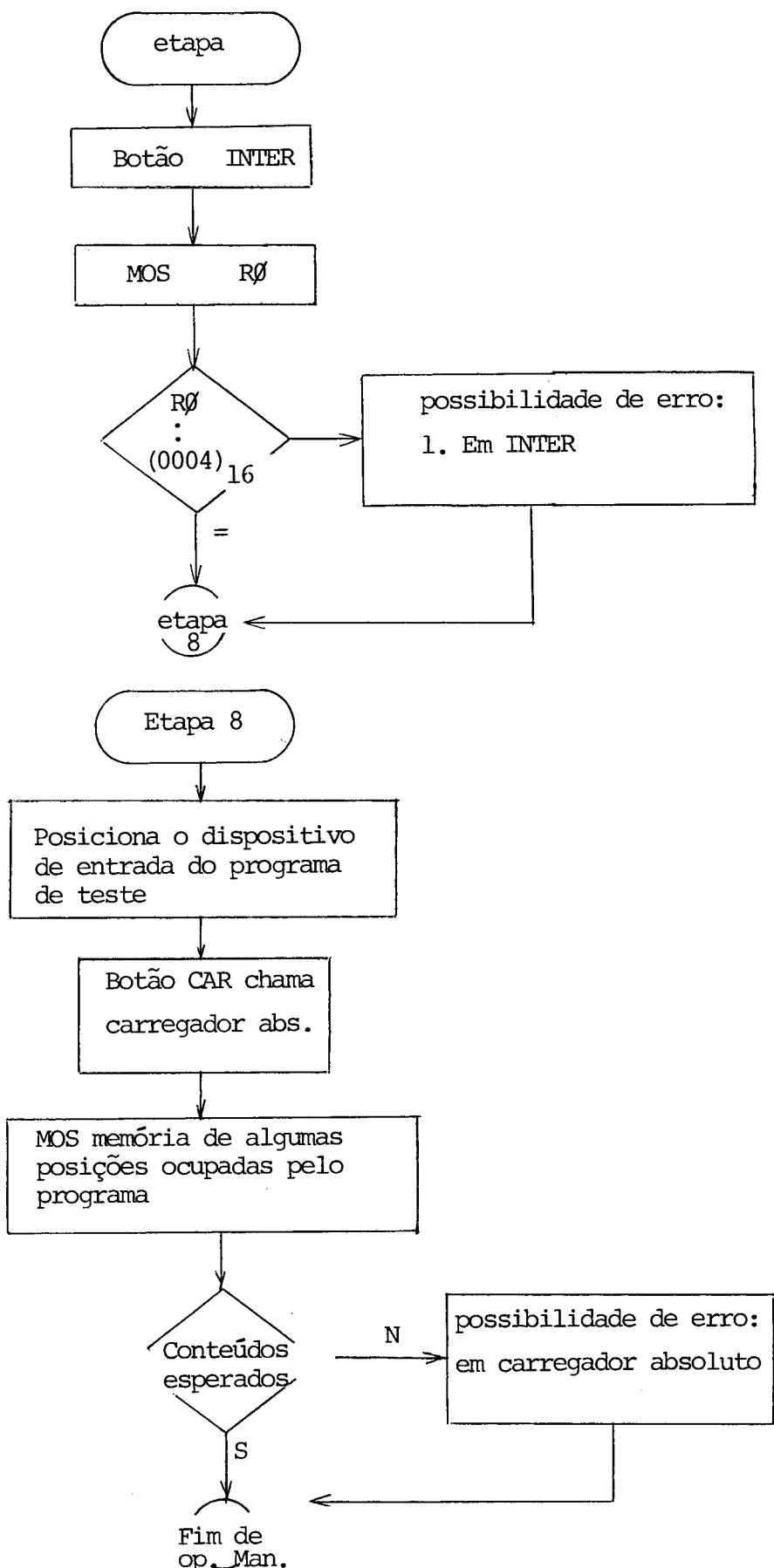

Prof. Estevam Gilberto de Simone

(Presidente)

---

Profa. Sueli Mendes dos Santos

---

Stephan Kovach

---

Manoel Lage Pinheiro da Silva

MOCHEL, MARIA ALICE SILVEIRA DE BRITO

Modelo Para Elaboração de Testes de Unidades Computacionais - Aplicação ao Processador de Instruções do Minicomputador Gll (Rio de Janeiro) 1979.

VI, 171p. 29,7 cm (COPPE-UFRJ, M.Sc., Engenharia de Sistemas e Computação, 1979)

Tese - Univ. Fed. Rio de Janeiro. Fac. Engenharia

i. Testes I. COPPE/UFRJ II. Título

AGRADECIMENTOS

Ao Professor Estevam Gilberto De Simone por sua orientação e incentivo; a Sérgio Leite Terzella e Álvaro Abílio Neves pelo apoio teórico e inestimável, aos integrantes do projeto de desenvolvimento do mini-computador Gll graças aos quais foi possível realizar este trabalho, à COBRA Computadores e Sistemas Brasileiros S.A. pelo acesso ao projeto Gll, referência indispensável na presente tese.

RESUMO

Este trabalho enfatiza o comportamento de tes tes de unidades computacionais sujeitas a falhas através do desenvolvimento de um sistema de detecção e diagnóstico para o processador de instruções do mini-computador G11, distribuído em três etapas a saber: levantamento de pontos, seleção dos testes necessários e avaliação de sua confiabilidade. Analisa a dificuldade de selecionar os pontos e os testes bem como determina a ordem de aplicação dos testes, sugerindo um método que contribua para a resolução destas questões, baseado no modelo descrito por Kime e Russel em 1975.

ABSTRACT

This paper studies the behavior of a test system, as applied to computing devices, which is intended for fault detection and diagnosis. The system has been applied to the Gll C.P.U., three main steps have then been considered, namely; problem identification, test selection, and reliability evaluation.

The model described by Kime and Russel (1975) has been applied as a mean to help solve all the proposed problems.

ÍNDICE

|                                                                                                   | <u>PÁGINAS</u> |

|---------------------------------------------------------------------------------------------------|----------------|

| I. <u>INTRODUÇÃO</u> .....                                                                        | 1              |

| II. <u>LEVANTAMENTO DOS PONTOS DE FALHA</u> .....                                                 | 7              |

| 2.1 - Características Gerais do Mini-Computador G11 ....                                          | 7              |

| 2.2 - Arquitetura da Unidade Central de Processamento ..                                          | 10             |

| 2.3 - Unidade de Controle Microprogramado .....                                                   | 11             |

| 2.4 - Unidade de Movimento de Dados .....                                                         | 26             |

| 2.5 - Micro Instrução .....                                                                       | 36             |

| 2.6 - Micro-Programação das Instruções .....                                                      | 40             |

| 2.7 - Relação dos Pontos de Falha .....                                                           | 49             |

| III. <u>TESTES DOS PONTOS DE FALHAS DO PROCESSADOR DE INSTRUÇÕES DO MINI-COMPUTADOR G11</u> ..... | 53             |

| 3.1 - Relação dos Testes Para Cada Ponto Sujeito a Falha .....                                    | 54             |

| 3.2 - Análise dos Testes Relacionados Quanto a Capacidade de Localização de Falhas .....          | 70             |

| . Segunda Relação de Pontos Baseada nas Características Apontadas Pela Avaliação                  |                |

| 3.3 - Descrição dos Testes .....                                                                  | 80             |

|                                                                                                                                                                                                          |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <u>IV. AVALIAÇÃO DO SISTEMA DE TESTES PROPOSTO .....</u>                                                                                                                                                 | 114 |

| <br>                                                                                                                                                                                                     |     |

| 4.1 - Apresentação do Modelo de Determinação de Detec-<br>bilidade e Diagnosticabilidade com Reparo de um<br>Sistema Digital com t Componentes Sujeito a Falha,<br>Concluído por Kime e Russel [3] ..... | 114 |

| <br>                                                                                                                                                                                                     |     |

| 4.2 - Avaliação do Sistema de Testes do Processador de<br>Instruções do Mini-Computador G11 de Acordo com<br>o Modelo Proposto por Kime e Russel [3] .....                                               | 135 |

| <br>                                                                                                                                                                                                     |     |

| . Relação de Falhas Selecionadas na Última Descri-<br>ção de Testes Apresentados no Capítulo 3                                                                                                           |     |

| <br>                                                                                                                                                                                                     |     |

| . Matrizes Preenchidas de Acordo com o Sistema de<br>Teste Definido Para o Processador de Instru-<br>ções do Mini-Computador G11                                                                         |     |

| <br>                                                                                                                                                                                                     |     |

| . Análise do Comportamento do Sistema Refletido<br>nas Matrizes T e G                                                                                                                                    |     |

| <br>                                                                                                                                                                                                     |     |

| <u>V. CONCLUSÕES .....</u>                                                                                                                                                                               | 155 |

| <br>                                                                                                                                                                                                     |     |

| APÊNDICE 1 - Conjunto de Instruções do Processador do<br>Mini-Computador G11 .....                                                                                                                       | 158 |

| <br>                                                                                                                                                                                                     |     |

| BIBLIOGRAFIA .....                                                                                                                                                                                       | 169 |

## CAPÍTULO I

### INTRODUÇÃO

Com o aumento da complexidade dos sistemas digitais atuais, a confiabilidade tornou-se um aspecto importante. Os sistemas digitais como dispositivos físicos estão sujeitos a falhas. A tecnologia empregada atualmente torna os sistemas digitais mais confiáveis que a tecnologia empregada inicialmente, a nível de cada componente, devido ao crescimento da integração dos circuitos. Uma falha pode ser definida como qualquer mudança não desejada no comportamento de um sistema. O ideal em termos de manutenção de um sistema digital é que a detecção, o diagnóstico e o reparo de uma falha sejam efetuados no tempo mais breve possível.

Nos sistemas digitais envolvendo processamento de tempo real como redes de distribuição telefônica ou controle de vôo aéreo chega a ser necessário o uso de monitores, que exercitam e testam o sistema periodicamente, verificando seu funcionamento, e podendo capacitar a continuação da operação sob certas falhas e até repará-las. Em alguns sistemas este esquema deve estar incorporado para garantir a alta confiabilidade. São os casos extremos de processamento em tempo real, onde a necessidade obriga o sistema a possuir "auto-reparo".

A questão do tempo de desativação de uma máquina está diretamente ligada ao seu esquema de manutenção, que vai desde a infra-estrutura que a fábrica possui em termos de re

cursos humanos e sistemas de manutenção até sua política de manutenção que pode ser por relocação de módulos ou componentes.

Um fator importante na manutenção é o sistema de teste. Sua eficiência é medida pela capacidade de localização da falha, permitindo o reparo que pode ser feito através de reconfiguração, substituição ou correção da parte defeituosa.

Quando se pretende verificar o funcionamento de uma máquina para reparar algum defeito que esteja ocorrendo, na realidade está se tentando verificar é o estado das peças e suas conexões. Esta observação leva a considerar que o teste de uma máquina é um conjunto de testes de peças. Cada peça merecendo atenção e sendo testada em todas as situações possíveis.

As situações examinadas para cada peça, são as situações externas a peça. Por exemplo, se a peça em questão é um componente eletrônico, só interessa analisar as saídas correspondentes as entradas submetidas. Não há interesse em verificar o funcionamento interno do componente. Interessa-nos apenas ter conhecimento se os resultados esperados são obtidos. Isto é, se o componente funciona adequadamente ou não. No entanto, se a política de reparo, determinar o conserto da peça, em vez de sua substituição, após o exame externo quando houver a constatação de que a peça apresenta defeito, será a peça examinada internamente. O que limita então o detalhamento do exame de uma máquina é o nível do reparo.

No caso do processador de instruções, onde as instruções podem ser consideradas como seu revestimento, confundindo, o objeto do teste, no "processador" ou "conjunto de instruções", o detalhamento é um item importante a ser determinado, devido a quantidade de elementos envolvidos em seu interior.

Um dos processadores mais populares o "8080" da INTEL, apresenta uma coleção de 240 (duzentos e quarenta) instruções. Possibilitar esta variedade de funções em uma unidade computacional e garantir o seu desempenho, leva a supor que seu projeto não seja de simples concepção. Para o usuário as instruções se traduzem como funções que recebendo determinados valores como seus parâmetros, geram resultados esperados. Esta imagem contrasta com o comportamento complicado no interior do processador, que sugere uma rede de componentes, onde cada instrução ao ser executada, provoca a ativação de um caminho próprio, i.e., para cada instrução existe uma sequência programada de ativação de componentes.

Para conhecer o comportamento de um processador, o interior de cada instrução, é necessário estudar em detalhes, a arquitetura do processador, sua unidade de controle, sua unidade de comunicação de dados. Ao mesmo tempo, sem perder de vista o objetivo do teste, levantando apenas os elementos necessários ao teste, os elementos que podem ser reparados quando apresentarem defeito.

Desde 1950 que estudos vem sendo realizados na área de testes de sistemas digitais. A bibliografia deste assunto já é extensa e Breuer et al [1] procuraram reuni-la no livro "DIAGNOSE & RELIABLE DESIGN OF DIGITAL SYSTEMS". O peso dado a cada capítulo, bem como as próprias referências bibliográficas a pontam que a maioria das teorias se voltaram para a verificação de funcionamento dos circuitos digitais. Hoje em dia, quando os componentes apresentam uma alta integração, chegando a possuir software armazenado, como a microprogramação, a tentativa razoável seria aproveitar os resultados destes estudos extrapolando-os para um nível superior, tratando os elementos microprogramados como pontos, assim como os circuitos tem seus pontos analisados. É aproximadamente dentro desta perspectiva que se desenvolverá o presente trabalho.

A teoria que ensaia os testes dos componentes com alto índice de integração é descrita por Lippmann et al [2], e indica que os esquemas tradicionais de testes de unidades computacionais são projetados para encontrarem falhas fixas na maioria dos sistemas combinatoriais, onde pirâmides de circuitos são usados para efetuar uma tarefa específica e assim operar em caminhos que podem ser traçados seguindo o circuito específico. Deste modo estes métodos não podem satisfazer aos testes das barras bidirecionais e as falhas de software que caracterizam os sistemas baseados em microprocessadores. Uma possível solução seria então, o uso de novos algoritmos de diagnósticos desenvolvidos para serem testados nos microcomputadores.

Devido ao alto nível de integração dos microprocessadores, seus testes são complicados, pois os novos circuitos de alta integração tanto oferecem solução como ocasionam novos problemas. O artifício a utilizar é o aproveitamento da própria inteligência dos microcomputadores, notadamente sua habilidade de fazer auto-teste. Os "auto-testes" podem reduzir os custos de testes de microcomputadores e pode ter o mesmo efeito que os "testes de placas de microprocessadores".

Escritos nas próprias linguagens de microprocessadores em vez da linguagem do equipamento de teste automático, um programa de teste residente providenciará grandes volumes de dados estimulados e verificações apuradas do funcionamento do sistema. Além destas vantagens, podem ser usados em testes das fases de desenvolvimento, produção, implantação e manutenção.

Para que o sistema de teste proporcione reparo a nível de desenvolvimento, verificando todos os pontos de projeto, seu diagnóstico deve ser minucioso, fornecendo as localizações das falhas. Um exame extenso da arquitetura do processador de instruções do mini-computador G11 deve ser feito com o objetivo de levantar todos os pontos de falhas possivelmente reparáveis por reconfiguração, substituição ou reparo local. Ao mesmo tempo a implementação do teste deve levar em consideração que sua ferramenta básica está em teste e que pode não estar livre de erros exigindo que os testes mais simples sejam feitos antes, que sejam repetidas situações que utilizem o mesmo recurso para que se chegue a conclusão de onde ocorre uma falha, caso

uma situação tenha apresentado defeito. Outro aspecto considerado são os pontos que são ativados sempre para qualquer situação e que não tem possibilidade de serem identificados isoladamente, sendo então por necessidade reunidos em um ponto. É importante que no momento de descrição dos testes os pontos estejam totalmente delineados para que não haja nem redundância nem falta de testes.

Após o levantamento dos pontos e descrição dos testes deve ser feita uma avaliação dos testes no que diz respeito a diagnóstico com reparo. Vários autores [3] a [16] estudaram a questão da avaliação dos testes, e alguns critérios foram estabelecidos para que um sistema de teste tenha capacidade de ser diagnosticável com reparo. O estudo desses autores não evidiu apenas a avaliação, foi acrescentada a teoria de testes alguma formalização.

## CAPÍTULO II

### LEVANTAMENTO DOS PONTOS DE FALHA

A arquitetura do processador de instruções do minicomputador G11 vai ser analisada neste capítulo com o objetivo de serem levantados todos os pontos de falha que deverão permitir reparo.

#### 2.1 - Características Gerais do Mini-Computador G11

- a) Palavras de 16 bits de comprimento, ou 2 "bytes" de 8 bits cada um.

- b) Endereçamento direto de 64 K palavras de memória principal ( $K = 1024$ ).

- c) Processamento de palavras ou "bytes" (facilidades para a manipulação de bits individuais).

- d) Estrutura modular: as funções básicas do sistema são desenhadas por módulos de fácil reposição, que interagem assincronamente por intermédio de uma via comum de alta velocidade.

- e) Possui um sistema de ponteiros dinâmicos que permite a manipulação eficiente de estruturas de dados tais como pilhas, vetores, filas, ou tabelas.

- f) Conjunto de 8 registradores de 16 bits de propósito geral. Um

desses registradores é usado como contador de instruções.

- g) Dois modos de processamento: supervisor e usuário.

- h) Sistema de interrupções com 9 níveis de prioridade.

- i) Interrupções de vários níveis através de um conjunto de posições reservadas de memória.

- j) Memória de semicondutor de acesso rápido.

- k) Endereçamento relativo a uma base, permitindo que as operações de relocação estática e dinâmica sejam feitas em qualquer instante do funcionamento do processador.

- l) Proteção contra acessos de escrita na memória feitos fora de uma área associada a um programa.

- m) Poderoso conjunto de 117 instruções de máquina micro-programadas. Uma instrução pode ter 16 ou 32 bits de comprimento.

- n) Vários modos de endereçamento são disponíveis para os operandos de uma instrução. Entre esses podemos citar:

- Operando contido na própria instrução (imediato);

- Operando em registrador de propósito geral;

- Endereço de operando em registrador de propósito geral, podendo esse ser pré-incrementado, ou pós-decrementado, durante o endereçamento;

- Endereço do operando especificado na própria instrução, com ou sem uso de um registrador de índice, e com ou sem pré-incremento do índice;

- Instrução especifica endereço do endereço do operando, com ou sem pós-indexação, e com pré-incremento opcional do índice.

- o) Até 4 canais de entrada/saída podendo ser ligados a via comum do G-11. Cada canal pode ser do tipo seletor (transfere blocos de palavras com um dispositivo de cada vez), ou do tipo concentrador (transfere "bytes" com vários dispositivos ao mesmo tempo).

- p) As instruções de entrada/saída do G-11 permitem o endereçamento de no máximo 16 dispositivos por canal. Um dispositivo pode ser um periférico, ou uma unidade de controle a qual estão ligados um ou mais periféricos.

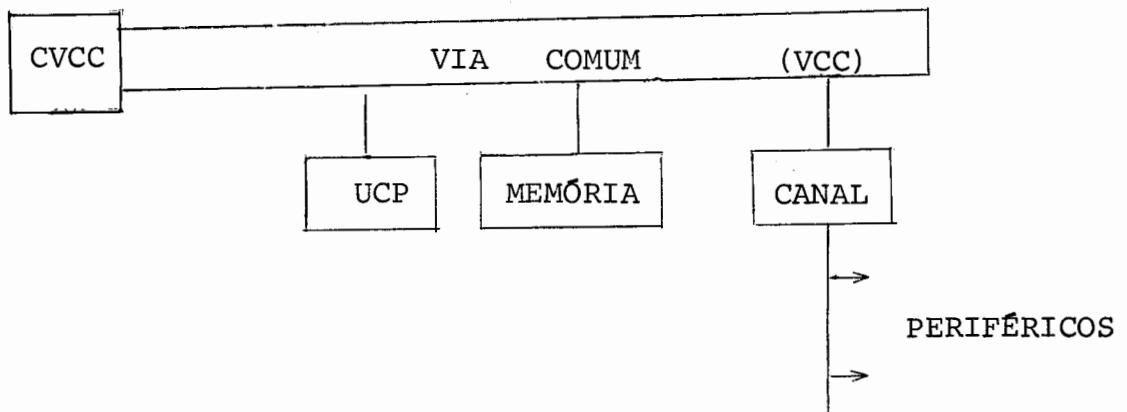

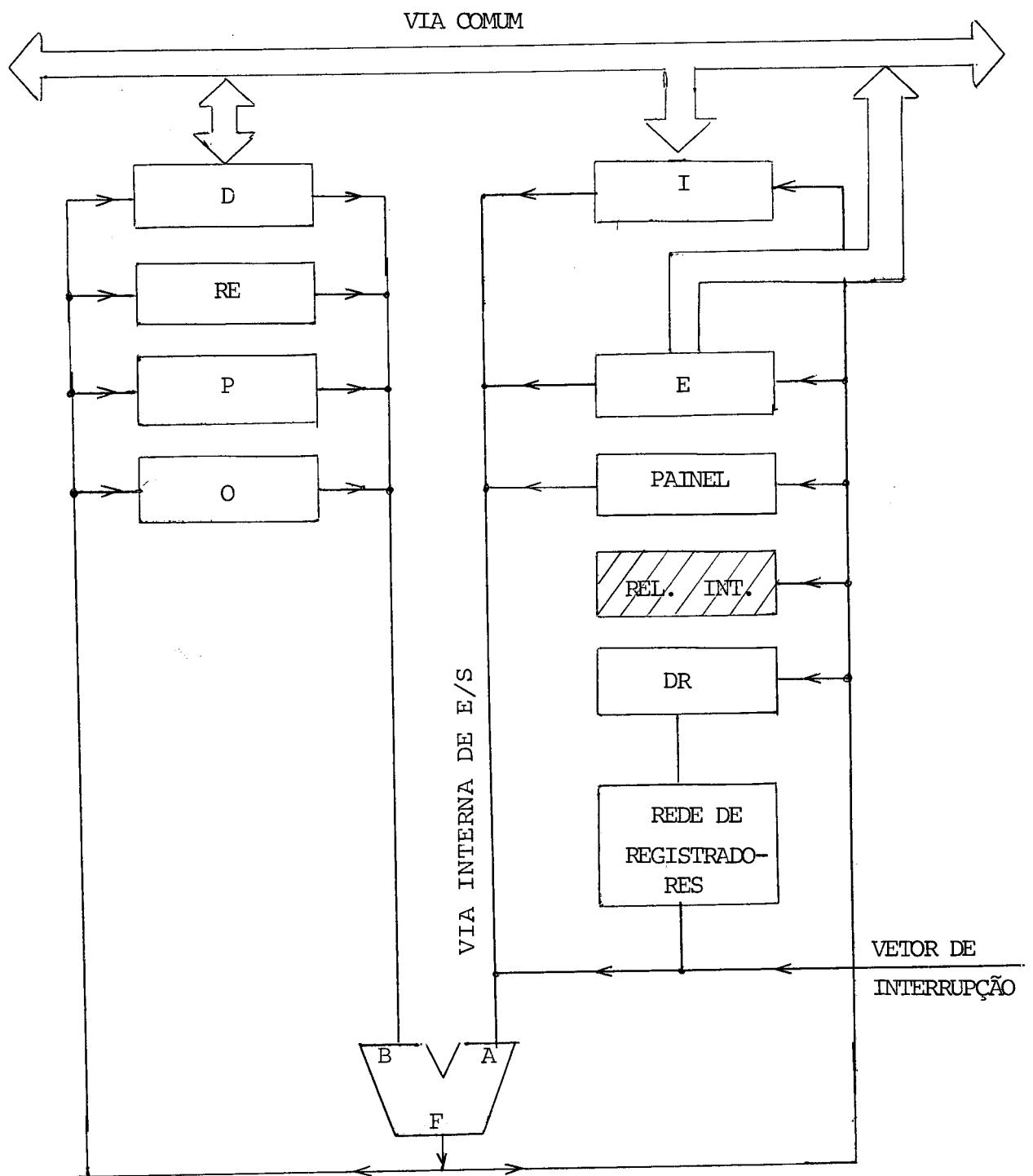

- q) Configuração do sistema: O mini-computador G-11 possui uma estrutura modular, como pode ser visto na figura 2.1. Os módulos se ligam a uma via comum bidirecional, capaz de transmitir 16 bits de dados em paralelo, chamada de Via Comum de Comunicação (VCC). Os módulos do G-11 são:

- Processador Central (UCP)

- Memória Principal

- Canais de Entrada/Saída, do tipo seletor ou concentrador

- Controlador da Via Comum de Comunicação (CVCC), responsável pelo controle de acesso e monitoramento dos diálogos que ocorrem na via.

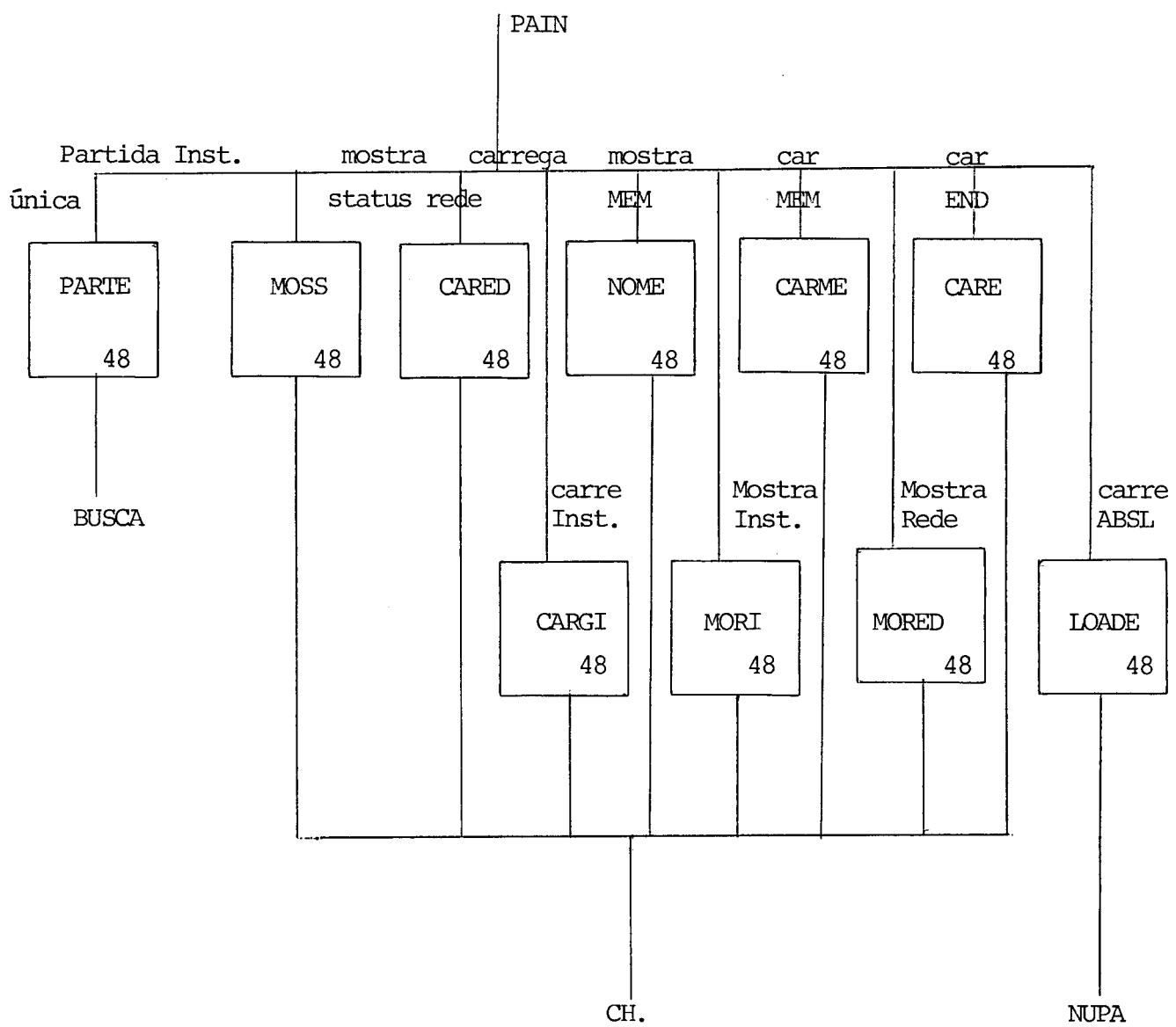

Fig. 2.1 - ESTRUTURA DO GII

## 2.2 - Arquitetura da Unidade Central de Processamento

O GII é um minicomputador de propósitos gerais, implementado com lógica TTL, e composto de vários módulos interconectados por uma Via Comum de Comunicação (VCC).

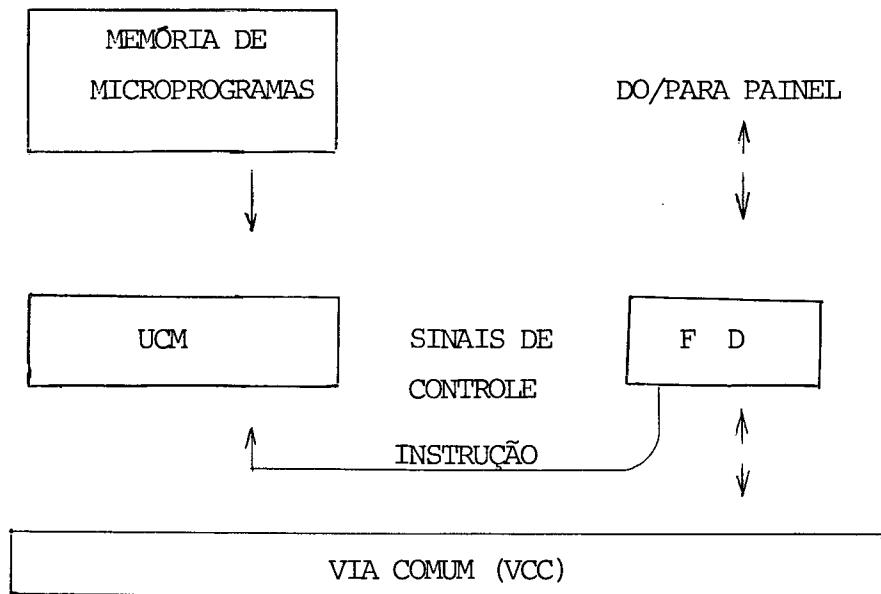

A Unidade Central de Processamento (UCP) do GII é o módulo que interpreta e executa a maioria das instruções do computador. Ela emprega aritmética inteira de complemento a 2, e é capaz de endereçar diretamente 65.536(64K) palavras de 16 bits de memória principal.

A UCP pode ser dividida em dois submódulos: A unidade de movimento de dados (UMD) e a unidade de controle microprogramada (UCM). A figura 2.2 ilustra a composição da UCP.

Fig. 2.2 - O PROCESSADOR CENTRAL

A UMD é composta de registradores de 16 bits e de uma Unidade Lógica e Aritmética (ULA), interligados de modo a realizar as operações necessárias à execução de uma instrução.

A UCM identifica a instrução e controla a sequência de passos necessários para executá-la. Ela utiliza uma memória de semi-condutor de acesso rápido, do tipo "lê-somente" (ROM), onde estão armazenados os microprogramas que, devidamente decodificados na UCM, geram os sinais para executar a instrução.

### 2.3 - Unidade de Controle Micropogramada

Para a descrição posterior do funcionamento da unidade de controle, cabe primeiramente definir alguns termos que são usados.

- Memória de controle: É uma unidade de armazenamento que contém os microprogramas. No caso do G-11 é uma memória do tipo "ler-somente" expandível até 4K palavras de 32 bits por palavra.

- Micro-programa: É um conjunto de micro-instruções que devem ser executados numa determinada sequência.

- Micro-instrução: É o conteúdo de uma palavra de 32 bits da memória de controle, subdividida em vários campos contendo micro-ordens.

- Campo: É cada subdivisão da micro-instrução onde estão especificadas as micro-ordens. A micro-instrução do G11 possui 10 campos.

- Micro-ordem: É um código particular de uma certa função, especificado num dos campos da micro-instrução.

- Palavra de controle: É uma palavra de 32 bits da memória de controle, contendo uma micro-instrução, cujas micro-ordens são executadas no mesmo ciclo de controle. O conceito de palavra de controle e micro-instrução geralmente se confundem.

- Sinais de controle: São todos os sinais elementares que se originam da decodificação de cada micro-ordem. Estes sinais divergem da unidade de controle para partes diferentes da máquina , permitindo ou inibindo a passagem de informação pelos elementos armazenadores da unidade de movimento de dados do Processar

dor Central (UCP) e demais circuitos, além da própria Unidade de controle.

A microprogramação dispõe das seguintes entidades para o processamento das informações:

- Rede de 16 registradores: 4 registradores de rascunho

- 1 registrador de pilha de contexto

- 1 registrador de limite de programa

- 1 registrador de base local

- 1 registrador de programa

- 8 registradores de propósito geral

(R0 a R7), sendo o registrador R0 usado como contador de instruções.

- Registrador de dados (D)

- Registrador de endereços (E)

- Registrador de instruções (I)

- Registradores deslocadores (P e Q)

- Registrador de Estado (RE)

- Unidade lógica e aritmética

- Painel

- Memória principal

- Via comum

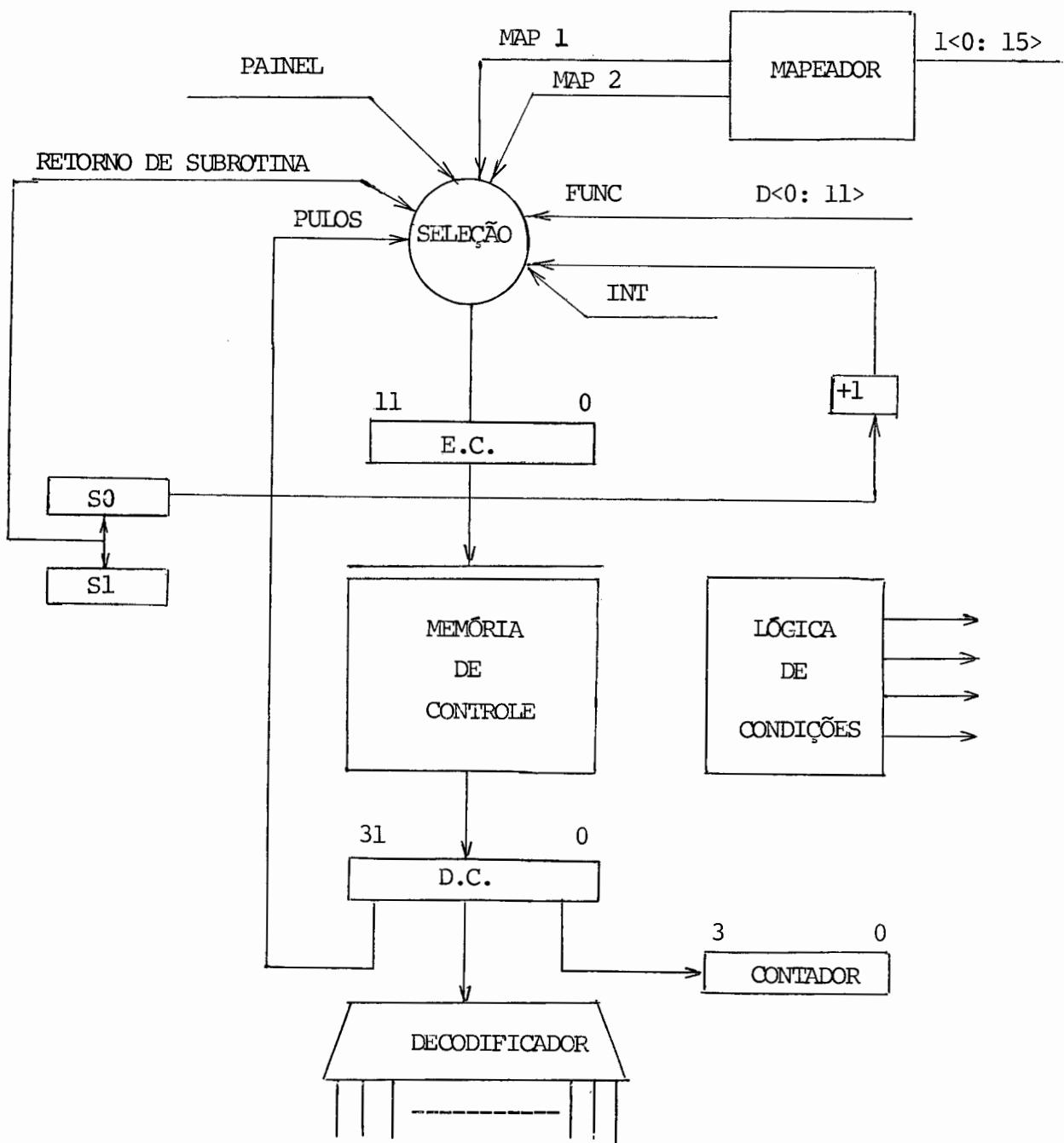

A unidade de controle é composta dos seguintes elementos:

- Mapeador

- Seleção

- Memória de controle

- Registrador de endereços da memória de controle (EC)

- Registrador de dados da memória de controle (DC)

- 2 registradores de endereço de retorno de micro-subroutines (S0 e S1)

- Decodificadores

- Somador de "+1"

- Contador (CNTD)

- Lógica de testes de condições

Fig. 2.3 - FLUXO DE CONTROLE

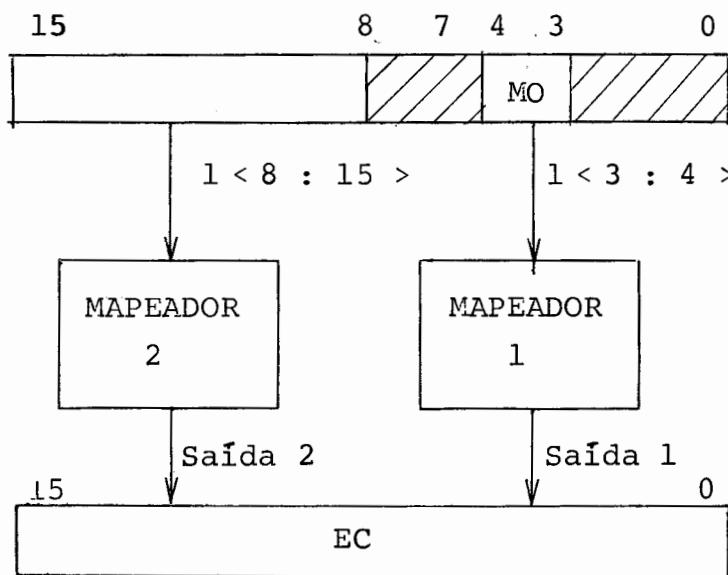

### 2.3.1 - Mapeador

O interfaceamento entre a unidade de movimento de dados do processador e a unidade de controle é feito pelo mapeador, cuja função é endereçar (mapear) na memória de controle um determinado microprograma de acordo com o código de operação da instrução no registrador de instruções I, botão acionado no painel, ou alguma interrupção. O mapeador, portanto, é constituído de 3 partes:

- Mapeador de instruções

- Mapeador de painel

- Mapeador de interrupções

-

- . Mapeador de instruções

Esse mapeador consiste basicamente de duas memórias do tipo "ler-somente", cujas entradas são alimentadas pelo registrador I e cujas saídas podem ser relacionadas por certas micro-ordens para o registrador de endereços da memória de controle (EC), conforme pode ser observado na fig. 2.4.

Fig. 2.4 - MAPEADOR DE INSTRUÇÕES

Ainda observando a fig. 2.4, o mapeador 1 endereça uma micro-rotina na memória de controle correspondente ao cálculo de endereço efetivo ao modo de operação M (bits  $< 3:4 >$ ).

Existe uma micro-rotina para cada modo de operação:

| MO          | MODO DE OPERAÇÃO          |

|-------------|---------------------------|

| $(0 \ 0)_2$ | Direto                    |

| $(0 \ 1)_2$ | Indireto                  |

| $(1 \ 0)_2$ | Indireto pré-incrementado |

| $(1 \ 1)_2$ | Indireto pós-decrementado |

Se não existir o campo MO na instrução, o mapeador 1 endereça a micro-rotina de execução da instrução se es-

ta for curta, ou permite o acionamento do mapeador 2 que endereçará uma micro-rotina de cálculo de endereço efetivo correspondente ao modo de endereçamento ME, se a instrução for longa.

O mapeador 2 tem suas entradas alimentadas pelo byte mais significativo da instrução da seguinte maneira:

- Se a instrução for longa, as entradas do mapeador 2 são: O código de operação (bits < 11:15 >), campo S/D (bit < 10 >) e campo ME (bits < 8:9 >).

- Se a instrução for curta, as entradas do mapeador 2 são: O código de operação (bits < 11:15 >), e sub-código de operação (bits < 8:10 >).

No caso de instruções longas, esse mapeador endereça primeiramente uma micro-rotina de cálculo de endereço efetivo correspondente ao modo de endereçamento ME (bits < 8:9 >).

| ME                | MODO DE ENDEREÇAMENTO          |

|-------------------|--------------------------------|

| (00) <sub>2</sub> | Direto/pré-indexado            |

| (01) <sub>2</sub> | Indireto 1 nível/pré-indexado  |

| (10) <sub>2</sub> | Indireto 2 níveis/pré-indexado |

| (11) <sub>2</sub> | Indireto 1 nível/pós-indexado  |

Após a execução da micro-rotina de endereçamento ME, o mapeamento 2 endereça o micro-programa de execução da instrução.

No caso das instruções curtas, será endereçado o micro-programa de execução propriamente dita da instrução correspondente ao código e sub-código de operação.

Tanto o mapeador 1 como o mapeador 2 tem suas saídas selecionadas para o registrador EC através de micro-instruções especiais que serão descritas mais adiante.

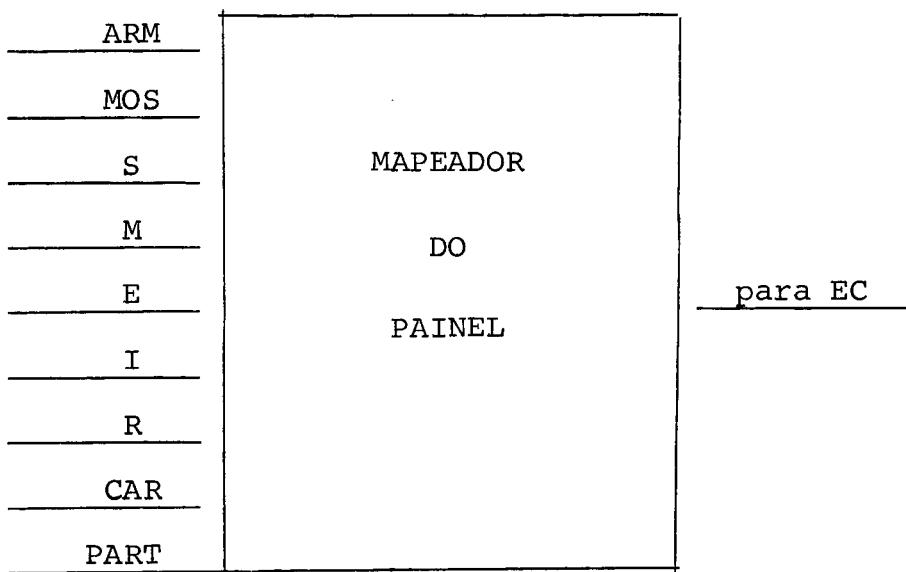

#### . Mapeador do Painel

Esse mapeador tem suas entradas alimentadas por um conjunto de botões do painel frontal do G-11, e sua finalidade é a de endereçar um micro-programa que execute as funções correspondentes a cada botão do painel.

Fig. 2.5 - MAPEADOR DO PAINEL

Esse mapeador tem sua saída selecionada para o registrador EC por meio de uma micro-instrução especial que se rá descrita mais adiante.

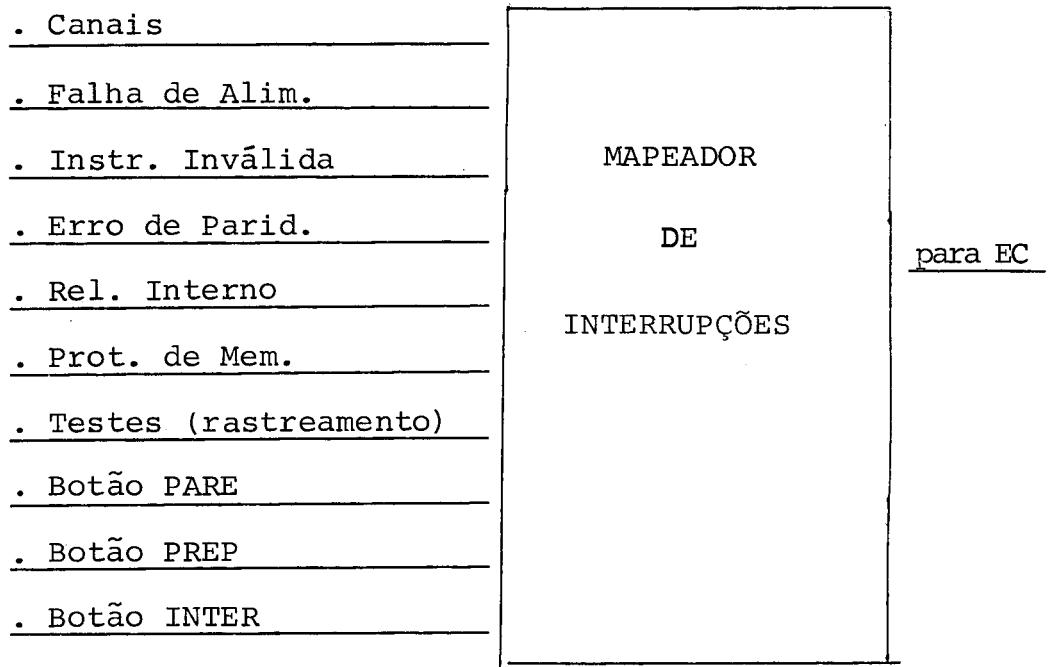

- Mapeador de Interrupções

Esse mapeador tem suas entradas alimentadas pelo circuito de interrupção e no conjunto de botões do painel, e sua finalidade é a de endereçar um micro-programa de tratamento de cada interrupção que possa ocorrer.

Fig. 2.6 - MAPEADOR DE INTERRUPÇÕES

Todas as interrupções na figura acima, exceção por proteção de memória e instruções inválidas são mapeadas e tratadas após o término da execução da instrução sendo executada por ocasião da ocorrência da interrupção. As duas citadas, por

serem internas, podem ocorrer durante a execução de uma instrução.

### 2.3.2 - Seleção

A seleção é ativada por micro-ordens específcas, permitindo a passagem para o registrador de endereços da memória de controle (EC) uma das seguintes entradas:

- As duas saídas do mapeador;

- Endereço de retorno de uma micro-subrotina para o micro-programa principal;

- Endereço contido nos bits de 19 a 30 nas micro-instruções de pulo (pulos dentro dos micro-programas ou para outras micro-rotinas);

- Endereço proveniente do mapeador de interrupção;

- Endereço proveniente do mapeador do painel;

- Endereço da micro-instrução seguinte proveniente do somador de +1;

- Saída da Unidade Lógica e Aritmética.

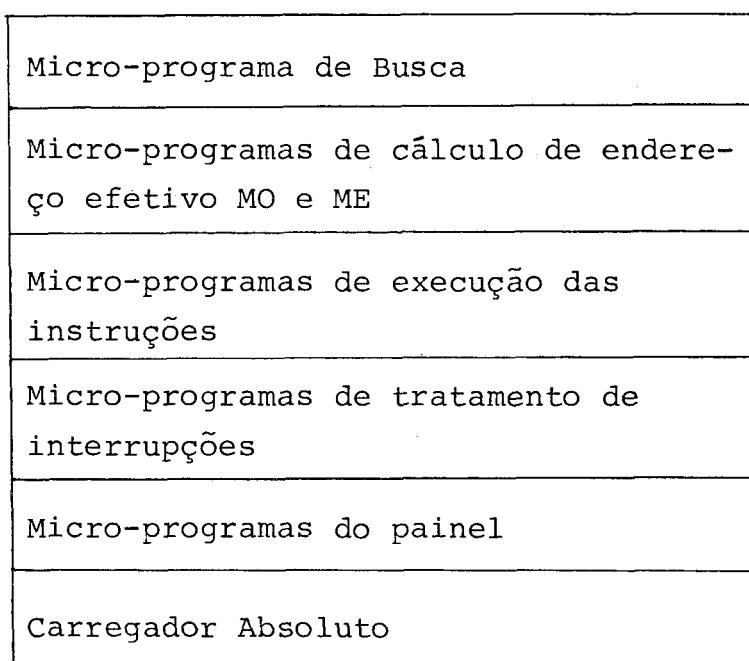

### 2.3.3 - Memória de Controle

A memória de controle é constituída de uma memória "ler-somente", com expansibilidade de até 4K palavras de 32 bits. Aqui estão contidos todos os micro-programas da fase de busca, fase de cálculo de endereço efetivo, e fase de execução

propriamente dita das instruções de máquina, tratamento das interrupções, de botões do painel, e carregador absoluto.

Fig. 2.6 - ORGANIZAÇÃO DA MEMÓRIA

DE CONTROLE

As palavras de 32 bits de cada micro-programa são lidas sequencialmente; esta sequência pode ser descontinuada por uma micro-ordem geral de desvio, que faz com que a execução do micro-programa seja desviada para outro ponto da memória de controle, retornando ou não para o endereço de retorno, conforme o tipo da micro-ordem.

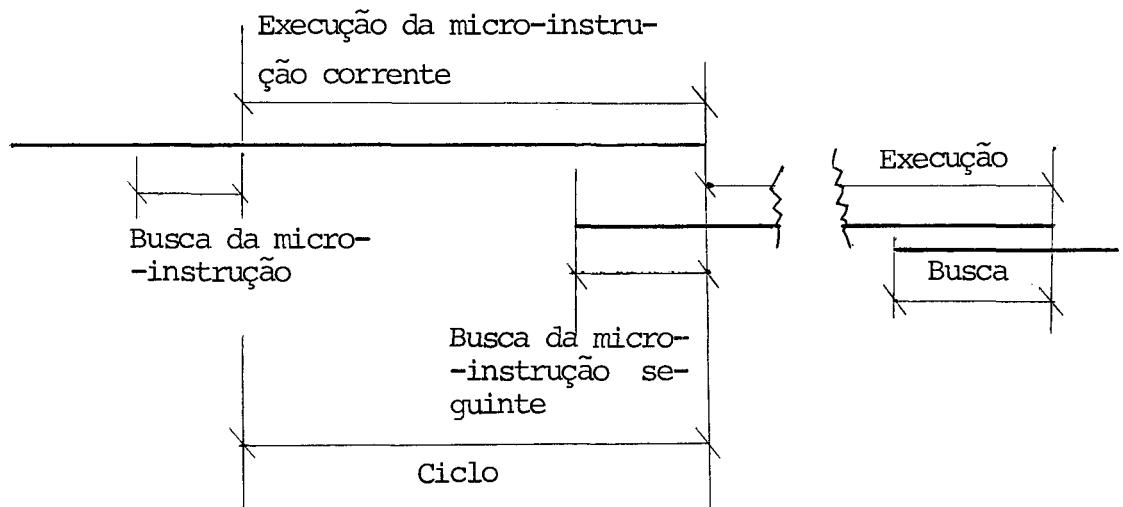

Após a leitura de uma micro-instrução, esta é armazenada no registrador de dados da memória de controle (DC). Durante a sua execução, a memória de controle é novamente acessada, automaticamente, para a leitura da micro-instrução seguinte, que só será armazenada no registrador DC após o término da execução anterior, o que se dá ao fim de um clique de controle.

Fig. 2.7 - CICLO DE CONTROLE

#### 2.3.4 - Registrador de Endereços de Controle (EC)

O registrador de endereços da memória de controle (EC) possui 12 bits, tendo assim a capacidade de acesso até 4K posições. Pode-se dividir esse espaço endereçável em blocos, sendo que uma versão qualquer do G11 não precisa conter todos os blocos possíveis de memória; o tamanho escolhido para os blocos, deverá ser tal que contenha o conjunto básico de instruções do G11. As micro-ordens de pulo possuem a capacidade de endereçar 4K palavras, com um endereçamento direto e absoluto não havendo portanto nenhuma espécie de paginação na memória de controle.

#### 2.3.5 - Registrador de Dados do Controle (DC)

Ao se endereçar uma posição na memória de controle a micro-instrução é lida e transferida para o registrador

de dados (DC) na memória de controle, destruindo o seu conteúdo anterior. A seguir é iniciada a fase de execução que consiste na decodificação geral de micro-ordens.

#### 2.3.6 - Registradores de endereço de retorno de micro-subrotina (S0 e S1)

Os registradores S0 e S1, de 12 bits, guardam o endereço de retorno quando de uma chamada de micro-subrotina. Esses dois registradores, funcionando como uma pilha, permitem até dois níveis de chamada de micro-subrotinas, no final das quais os endereços de retorno são recuperados em EC, prosseguindo-se a execução do micro-programa principal.

#### 2.3.7 - Decodificadores

Após a micro-instrução ter sido armazenada no registrador DC, inicia-se a decodificação das micro-ordens dos campos gerando à sua saída sinais de controle, ativando os circuitos necessários para a execução da operação especificada por cada micro-ordem.

#### 2.3.8 - Somador de "+1"

O somador de +1 é um circuito que incrementa de uma unidade o conteúdo do registrador EC fornecendo na sua saída o endereço seguinte à micro-instrução corrente. Ele é, portanto, responsável pela sequencialização normal do endereçamento

das micro-instruções, sendo inibido, apenas por uma micro-instrução geral de pulo.

#### 2.3.9 - Contador (CNTD)

O contador de controle CNTD possui 4 bits e é carregável por uma micro-ordem especial ou pelos 4 bits menos significativos da saída da ULA.

O contador CNTD é usado em todas as operações que necessitem de uma contagem de até 16 vezes, como acontece por exemplo com as operações de deslocamento. Ele é também usado para endereçar sequencialmente os registradores da rede na Unidade de Movimento de Dados do Processador.

#### 2.3.10 - Lógica de Testes de Condições

Este bloco fornece uma série de sinais de estado decorrentes da execução de uma instrução de máquina. Esses sinais são testáveis por micro-ordens de testes ao longo do micro-programa, gerando condições segundo as quais são executados desvios para pontos diferentes dos micro-programas que não as subsequentes.

O estado em que se encontra uma instrução durante o seu processamento é representado por condições geradas por operações efetuadas na ULA, deslocadores, do próprio código de operação da instrução, modo de endereçamento e de operação,

etc. Estas condições serão especificadas mais adiante, quando da descrição da palavra de controle do G11.

#### 2.4 - Unidade de Movimento de Dados

Essa é a unidade onde vão ser realizadas as operações. Consiste da interconexão dos registradores com a unidade lógica e aritmética Pode ser alimentada pelo painel ou memória e é controlada pela unidade de controle.

Fig. 2.8 - UNIDADE DE MOVIMENTO DE DADOS

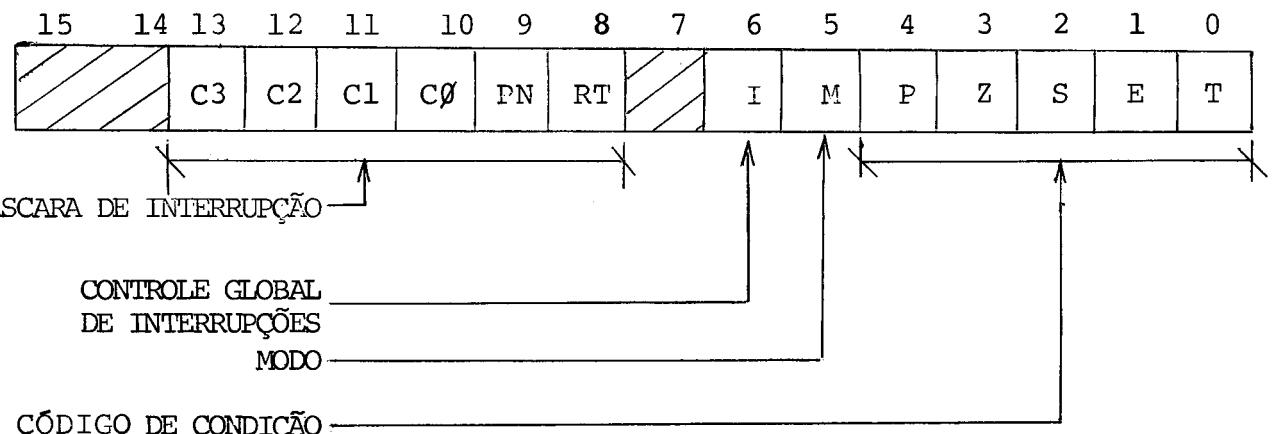

#### 2.4.1 - Registrador de Estado

Fig. 2.9 - REGISTRADOR DE ESTADO

Todas as informações sobre o estado atual da UCP são reunidas numa palavra de 16 bits (palavra de estado), que é mantida num registrador da UMD chamado de Registrador de Estado (RE). Essas informações consistem da máscara de interrupção, um indicador global de ocorrência de interrupções, um indicador do modo de execução (supervisor ou usuário), e os códigos de condição que descrevem o último resultado computado pela UCP.

##### . Máscara de Interrupção

A UCP reconhece 9 níveis de interrupções externas, com prioridades distintas. Desses, os 3 mais prioritários (níveis  $\emptyset$ , 1 e 2) não podem ser inibidos. Os 6 níveis restantes são controlados por uma máscara de interrupção, na qual cada bit corresponde a um dos níveis, conforme mostra a fig. 2.10.

| BIT DE RE | ORIGEM DA INTERRUPÇÃO | NOME | NÍVEL |

|-----------|-----------------------|------|-------|

| 8         | rastreamento          | RT   | 3     |

| 9         | painel                | PN   | 4     |

| 10        | canal 0               | C0   | 5     |

| 11        | canal 1               | C1   | 6     |

| 12        | canal 2               | C2   | 7     |

| 13        | canal 3               | C3   | 8     |

↑

PRIORIDADE

CRESCENTE

Fig. 2.10 - NÍVEIS DE INTERRUPÇÃO INIBÍVEIS

Convencionou-se que se o bit está ligado (=1) as interrupções correspondentes estão inibidas, e em caso contrário (=0) permitidas.

- Controle global de interrupções

A máscara de interrupção possibilita a inibição seletiva de interrupções. Entretanto, o G11 possui um mecanismo que permite a inibição de todas essas interrupções ao mesmo tempo, independente do valor da máscara. O bit I do RE é usado para essa finalidade.

Quando esse bit está ligado ( $I=1$ ) o processador não aceita nenhuma interrupção dos níveis 4 a 8, inclusive esses, mesmo que a máscara de interrupções permita a ocorrência das mesmas. Quando desligado ( $I=0$ ), é a máscara de interrupção que controla quais interrupções podem ocorrer.

O bit I pode ser alterado por programa (através de instruções privilegiadas), ou automaticamente por "hardware". O "hardware" liga esse bit após a ocorrência de qualquer interrupção, ou após uma chamada de supervisor (CSUP), para permitir que o supervisor carregue uma nova máscara de interrupção. O bit é também ligado ao ser apertado o botão PREP (prepara) do painel.

- Modo

O bit de modo (M) indica se a UCP está operando no modo supervisor ( $M=1$ ), ou no modo usuário ( $M=\emptyset$ ). O modo usuário restringe o acesso a máquina, não permitindo que certas instruções (ditas privilegiadas) sejam executadas. Qualquer tentativa de executar uma dessas instruções em modo usuário acarretará numa interrupção de nível 1.

As instruções privilegiadas do G11 são as seguintes, em ordem alfabética de mnemônico:

AA/AFI/CGMI/EBC/EBD/ENT/ESP/LC/LED/LIC/LRE/LVI/MED/MINT/PARA/RINT/SAI/SBC/SBD/.

O bit M é automaticamente ligado pelo "hardware" imediatamente após uma interrupção, ou após uma chamada de supervisor (CSUP). Com isso garante-se que o programa que trata a interrupção, ou a CSUP, tem acesso irrestrito à máquina. Ele é também ligado ao se apertar o botão PREP (prepare) do painel.

- Códigos de condição:

Os códigos de condição contêm informações sobre o último resultado que saiu da ULA, isto é, sobre a última instrução executada que realizou operações lógicas e/ou aritméticas.

Os bits do código de condição são ligados como se segue:

P = 1, se o resultado foi ímpar.

Z = 1, se o resultado foi zero.

S = 1, se o resultado foi negativo.

E = 1, se a operação resultou em "vai-um" do bit mais significativo.

T = 1, se a operação resultou em transbordamento.

NOTA: O transbordamento ("overflow") numa operação indica resultado errado, por não ser o mesmo representável em 16 bits.

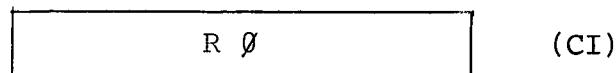

#### 2.4.2 - Registradores de Propósito Geral

O G11 dispõe de 8 registradores de 16 bits que podem ser usados como acumuladores em operações aritméticas, armazenamento temporário, indexadores ou ponteiros. Eles são chamados de registradores de propósito geral, e nas instruções do G11 são endereçados por um número de 0 a 7.

### CONTADOR DE INSTRUÇÕES

Fig. 2.11 - REGISTRADORES DE PROPÓSITO

#### GERAL

O registrador R0 é usado como o contador de instruções (CI) da máquina e contém o endereço relativo a base de programa da última palavra da instrução sendo executada. Normalmente o programador só emprega esse registrador para endereçamento relativo ao contador de instruções.

O registrador R7 possui também um uso especial. A UCP emprega esse registrador para passar informação ao supervisor sobre certas interrupções, ou para passar o número da CSUP numa chamada de supervisor; ele é ainda endereçado implicitamente em várias instruções de E/S. Tal uso de R7 é, entretanto, totalmente transparente aos programas de usuários.

Os registradores R0 e R1 possuem restrições

quanto ao seu emprego em instruções, a saber:

- O registrador R $\emptyset$  não pode ser usado como indexador;

- Não existem instruções curtas nem imediatas que usem R $\emptyset$  e R<sub>1</sub> como operandos;

- Ambos os registradores R $\emptyset$  e R<sub>1</sub> não são salvos nem restaurados pelas instruções SALV e REST, respectivamente;

- Os registradores R $\emptyset$  e R<sub>1</sub> não são usados como operandos implícitos de operações mistas (que envolvem operandos de 32 bits).

#### 2.4.3 - Base Local

O GII possui no seu reportório algumas instruções que usam um deslocamento não negativo de 8 bits, chamados de instruções de deslocamento curto. Esse deslocamento é usado em tempo de execução ao conteúdo do registrador de Base Local (BL), obtendo-se assim um deslocamento efetivo de 16 bits. A finalidade da base local é principalmente permitir o endereçamento de uma área de memória de até 256 palavras de tamanho por instruções curtas de 16 bits, em vez de se usar instruções longas de 32 bits, permitindo assim a economia de considerável área de código.

Um programa pode alterar e ler o valor de BL unicamente através das instruções (não privilegiadas) Restaura Registradores (REST) e Salva Registradores (SALV), respectivamente.

#### 2.4.4 - Base de Programa

À exceção das instruções Carrega Absoluto (CGA) e Armazena Absoluto (AA), todos os endereços gerados pelas instruções do G11 são relativas a um valor fixo, que fica armazenado no registrador de Base de Programa (BP). Usualmente esse valor é igual ao endereço absoluto da primeira palavra do programa em execução.

A menos das exceções já mencionadas, todos os endereços gerados na UCP são adicionados ao conteúdo de BP para a obtenção de um endereço efetivo de 16 bits, que será usado no acesso a memória.

O registrador BP só pode ser alterado como parte das operações de restauração de contexto, ou pela UCP após uma interrupção. Não há instrução para ler o conteúdo desse registrador.

#### 2.4.5 - Limite de Programa

O G11 usa o registrador de limite de programa (LP) em conjunto com BP para implementar um esquema de proteção de memória. O registrador LP contém o endereço relativo da última posição da área de programa (tamanho da área menos um), e a UCP impede qualquer acesso de escrita na memória fora da área limitada pelo par BP e LP.

É importante observar que não há proteção contra leitura de palavras da memória, isto é, dados podem ser lidos, ou instruções executadas, de qualquer lugar da memória. Entretanto, acessos de escrita são impedidos (uma interrupção do processador é gerada) caso o endereço efetivo de acesso a memória seja menor que BP, ou maior que a soma de BP e LP.

O LP só pode ser alterado como parte das operações de restauração de contexto, ou pela UCP após uma interrupção. Não há instrução que permita ler o conteúdo desse registrador.

#### 2.4.6 - Registrador Índice da Pilha de Contexto

O recebimento de uma interrupção pela UCP causa uma mudança de contexto, isto é, os registradores relevantes ao programa em execução são salvos na memória e novos valores são carregados em alguns desses registradores.

A área de memória onde deve ser salvo o contexto do programa interrompido é determinada pela UCP através do conteúdo do registrador índice da pilha de contexto (RIPC), e de uma palavra reservada de memória. A restauração desse contexto nos registradores também é feita por referência a RIPC e a mesma palavra reservada.

O registrador RIPC não pode ser lido por programa via instrução (privilegiada) ele índice da pilha de con-

texto (LIC). Ele não pode ser alterado por programa. A UCP inicia RIPC com o valor 1 (um) ao ser apertado o botão CAR (carrega) do painel.

#### 2.4.7 - Registrador de Dados D

#### 2.4.8 - Registradores Deslocadores P e Q

#### 2.4.9 - Registrador I

#### 2.4.10 - Registrador de Endereços E

#### 2.4.11 - Painel

#### 2.4.12 - Unidade Lógica e Aritmética

#### 2.4.13 - Registradores de Rascunho

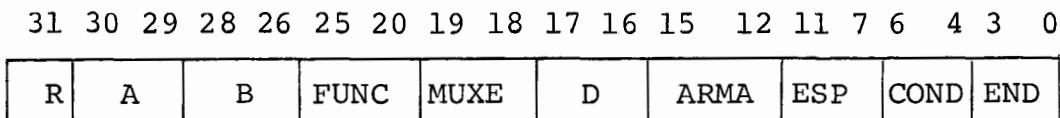

#### 2.5 - Micro Instrução

A micro-instrução no G11 é constituída de 32 bits divididos em 10 campos contendo as várias micro-ordens cuja decodificação gera sinais de controle que acionarão os circuitos convenientemente da Unidade de Movimento de dados e da própria unidade de controle, numa sequência tal que os algoritmos sejam corretamente executados.

O formato da micro-instrução é o seguinte:

Fig. 2.12 - FORMATO DA MICRO-INSTRUÇÃO

Cada campo possui um grupo de bits codificados que determinam a operação a ser efetuada pelo controle. Cada código desses grupos corresponde a uma micro-ordem.

As operações gerais especificadas em cada campo são as seguintes:

Campo R - As micro-ordens desse campo controlam o relógio central no sentido de permitir a geração dos ciclos de controle ou de inibi-los. São usados por ocasião de um acesso à memória principal ou à via comum de comunicação, a fim de parar o processamento de micro-instruções subsequentes até que o dado acessado esteja seguramente correto no registrador de dados da Unidade de Movimento de dados.

Campo A - Este campo contém as micro-ordens que selecionam o registrador de Unidade de Movimento de dados que terá acesso à entrada A da ULA.

Estas micro-ordens funcionam em conjunto com as dos campos MUXE e END.

Campo B - Este campo contém as micro-ordens que selecionam o registrador de Unidade de Movimento de dados que terá acesso à entrada B da ULA.

Campo FUNC - Esse campo contém os códigos das funções lógicas e aritméticas da ULA, ou das operações de deslocamentos efetuados pelos registradores deslocadores P e Q, com ou sem atualização dos bits do registrador de estado S do processador.

Campo MUXE - As micro-ordens desse campo controlam a seleção e endereçamento dos registradores da rede.

Eles funcionam em conjunto com as micro-ordens dos campos A e END.

Campo D - Esse campo contém as micro-ordens que determinam o sentido de deslocamento ou a carga dos registradores deslocadores P e Q.

Estas micro-ordens funcionam em conjunto com as do campo FUNC.

Campo ARMA - As micro-ordens desse campo são responsáveis pela seleção do registrador onde será armazenado o resultado da operação realizada no ciclo de controle corrente. Esse resultado é provindo da saída F de ULA.

Essas micro-ordens eventualmente funcionam em conjunto com as dos campos MUXE e END, quando for selecionado um dos registradores da rede.

Campo ESP - Esse campo contém os códigos das micro-ordens especiais que efetuam pulos para micro-rotinas diferentes, acessos à memória ou à via comum, testes de condições, controle sobre o circuito de seleção para o registrador EC, e carga imediata do contador CNTD.

Estas micro-ordens eventualmente funcionam em conjunto com as do campo COND, e do campo END, quando for determinada a carga do contador CNTD.

Campo COND - Esse campo contém as condições que devem ser testadas pelas micro-ordens condicionais do campo ESP. Essas condições só podem ser testadas por micro-programas e nunca por instruções de máquina. A condição é dita verdadeira se ela for igual a 1.

Campo END - Esse campo contém o código dos registradores da rede, vetor de interrupção e registrador de chaves do painel endereçáveis pelas micro-ordens dos campos A e MUXE.

## 2.6 - Micro-Programação das Instruções

O controle micro-programado permite a implementação mais simples das instruções, visto que as operações executadas seguem a mesma filosofia em todos os casos: os sinais de controle do fluxo são gerados pela decodificação ou mesmo diretamente das palavras de controle (micro-instruções) constituintes do micro-programa.

Essas operações são padronizadas para todas as instruções, permitindo assim uma facilidade na mudança ou ampliação do conjunto de instruções estabelecido, bastando para isso, configurar um micro-programa correspondente à execução da instrução modificada ou acrescentada.

Dessa maneira torna-se possível implementar instruções especiais (no caso do computador ser adaptado a funções específicas) sem a necessidade de modificação de circuitos, desde que estas instruções não difiram dos formatos gerais das instruções do conjunto básico já existente.

### 2.6.1 - Descrição Lógica da Micro-Programação das Instruções do G11

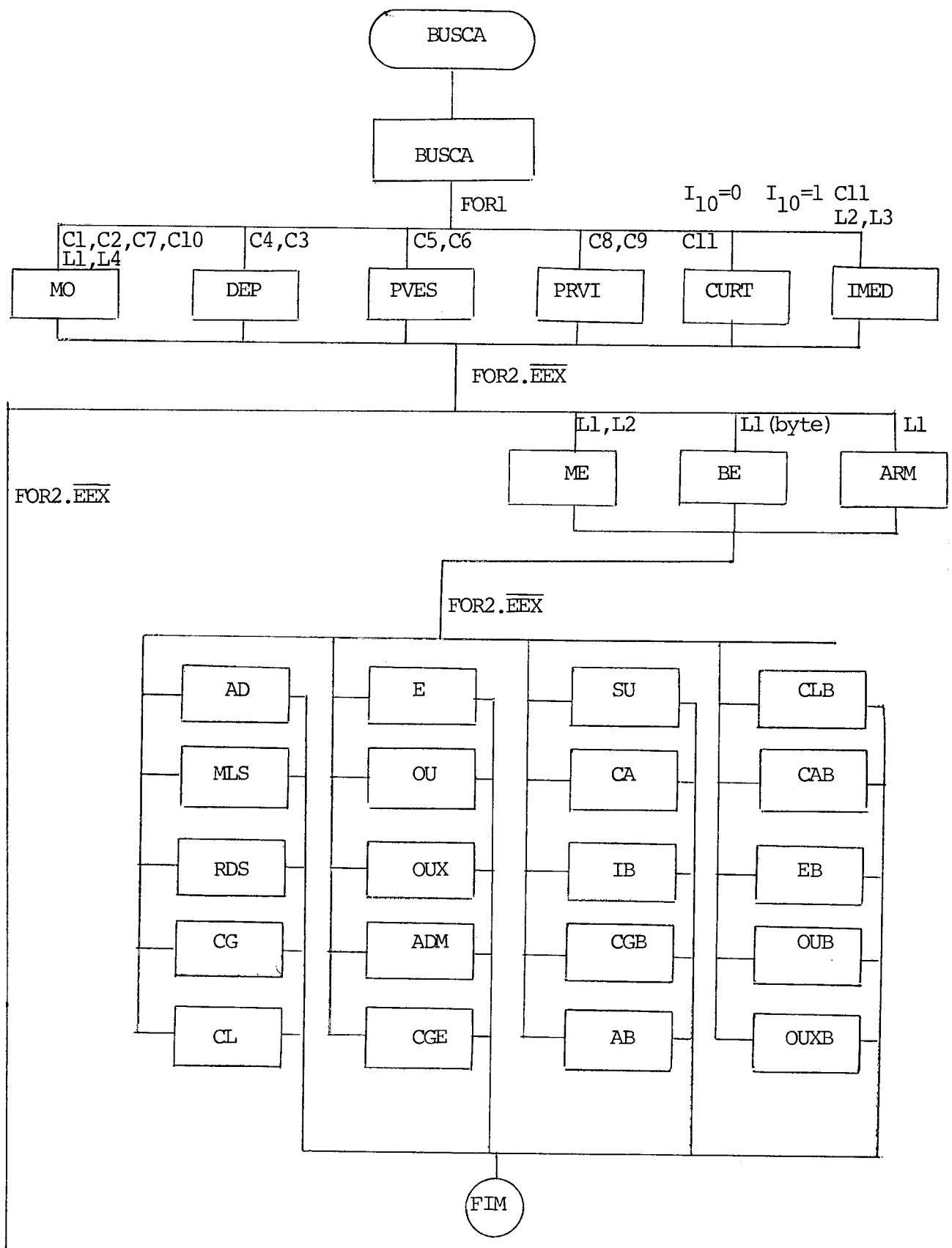

Toda a instrução passa por três fases durante a sua execução: Busca, cálculo de endereço efetivo e execução. O fluxograma seguinte representa a microprogramação das instruções.

**Descrição Lógica das Micro-Subrotinas:**

BUSCA, ME, BE, PEG, INIC, INICD, MGUA, MO, DEP, PVES, PRVI ,

CURT, IMED, GUAB.

**Micro-Rotina BUSCA:**

$R\emptyset \leftarrow$  endereço de próxima instrução

se instrução é curta:  $D \leftarrow I \cap (\emptyset\emptyset FF)_{16}$ ; vai para FOR1.

se instrução é longa: procede leitura da próxima palavra; vai para FOR1.

**Micro-Rotina ME:**

Para ME =  $\emptyset\emptyset | \emptyset 1 | 1\emptyset$

$D \leftarrow$  segundo operando;

$SP1 \leftarrow$  endereço do segundo operando (já indexado se for o caso);

$P \leftarrow Rj$ ;

vai para EEX.FOR2.

**Micro-Rotina BE:**

Para BE =  $00|01|10$

$D \leftarrow$  primeiro operando;

$P \leftarrow SP2 \leftarrow$  segundo byte com sinal expandido;

$SP1 \leftarrow$  endereço da palavra do byte;

vai para EEX.FOR2

Micro-Rotina PEG:

Se não indireto ( $M_0=00$ ):  $D \leftarrow (R_j)$ ; vai para fim.

Se indireto ( $M_0 \neq 00$ ):  $D \leftarrow C((B) + (Q))$ ; vai para fim.

Micro-Rotina INIC:

$SP\emptyset \leftarrow D$ ;

INICD: CALL PEG;

$SP3 \leftarrow Q$ ;

Se curta:  $Q \leftarrow R_i$ ; vai para fim.

Se longa:  $Q \leftarrow D$ ;  $D \leftarrow SP\emptyset$ ; vai para fim.

OBS: A micro-rotina INICD é uma parte da micro-rotina INIC.

Micro-Rotina MGUA:

Se direto:  $P \leftarrow (Q)$ ;  $R_j \leftarrow D$ ; vai para fim.

Se indireto:  $P \leftarrow (Q)$ ; vai para GUAB.

Micro-Rotina M0:

Se formatos C1, C2, C7, C10:

Se M0=00:  $D \leftarrow I \cap (00FF)_{16}$ ; vai para FOR2.

Se M0=01:  $Q \leftarrow$  endereço do 1º operando (conteúdo de  $R_j$ );

$D \leftarrow I \cap (00FF)_{16}$ ; vai para FOR2.

Se M0=10:  $R_j \leftarrow R_j + 1$ ;  $Q \leftarrow$  endereço do 1º operando (conteúdo de  $R_j$ );

$D \leftarrow I \cap (00FF)_{16}$ ; vai para FOR2.

Se M0=11:  $Q \leftarrow$  endereço do 1º operando (conteúdo de  $R_j$ );

$R_j \leftarrow (R_j) - 1$ ;  $D \leftarrow I \cap (00FF)_{16}$ ; vai para FOR2.

Se formato Ll, L4:

Se M0=00:  $D \leftarrow$  segunda palavra da inst;

Se M0=01:  $Q \leftarrow$  endereço do primeiro operando (conteúdo de  $R_j$ );

$D \leftarrow$  segunda palavra da inst;

Se M0=10:  $R_j \leftarrow R_j + 1$ ;

$Q \leftarrow$  endereço do primeiro operando;

$D \leftarrow$  segunda palavra da instrução;

Se M0=11:  $Q \leftarrow$  endereço do primeiro operando;

$R_j \leftarrow R_j - 1$ ;

$D \leftarrow$  segunda palavra da instrução;

vai para FOR2.

Micro-Rotina DEP:

Se formato C4 (PULA) :

```

SPØ ← RE;

D ← IN(00FF)16;

```

vai para FOR2.

Se formato L4 (DESVIO) :

```

SPØ ← RE;

D ← segunda palavra da instrução;

vai para FOR2.

```

Micro-Rotina PVES:

Se modo supervisor:

```

D ← IN(00FF)16;

Q ← D com bit 7 expandido;

vai para FOR2.

```

Se modo Usuário:

vai para PRIV.

Micro-Rotina PRVI:

```

P ← 001F;

```

se instrução não é CSUP ou PIT: se usuário: vai para PRIV.

```

Se modo supervisor ou I = (CSUP ou PIT): Q ← D com bit 7 expandido;

vai para FOR2.

```

Micro-Rotina CURT:

(C11 com  $I_{10} = 0$ )

P  $\leftarrow$  (BL) + (D);

E  $\leftarrow$  (P) + (B);

Lê,

D  $\leftarrow$  operando;

vai para FOR2.

Micro-Rotina IMED:

Se C11 com  $I_{10} = 1$  ou C3: D  $\leftarrow I_0(00FF)_{16}$ ;

vai para FOR2.

Se L2: D  $\leftarrow$  segunda palavra da instrução

vai para FOR2.

Micro-Rotina GUAB:

Se P > LD  $\rightarrow$  Proteção;

E  $\leftarrow$  B + P;

ESC;

vai para fim.

## 2.7 - Relação dos Pontos de Falha

1 - Unidade de Controle:

1.1 - Mapeador:

1.1.1 - Mapeador de Instruções:

1.1.1.1 - Mapeador 1:

1.1.1.1.1 - Quando instrução curta sem M0

1.1.1.1.2 - Quando instrução curta com M0

1.1.1.1.3 - Quanto instrução longa sem M0

1.1.1.2 - Mapeador 2

As suas duas alternativas já foram ativadas nos testes do mapeador 1, apenas não se combinou o cálculo de M0 e ME.

1.1.1.2.1 - Ativa o mapeador 2 para calcular ME após ter calculado M0

1.1.2 - Mapeador de painel:

1.1.2.1 - Função ARM

1.1.2.2 - Função MOS

1.1.2.3 - Função S

1.1.2.4 - Função M

1.1.2.5 - Função E

1.1.2.6 - Função R

1.1.2.8 - Função CAR

1.1.2.9 - Função PART

1.1.3 - Mapeador de interrupções:

1.1.3.1 - Canais

1.1.3.2 - Falha de alimentação

1.1.3.3 - Erro de paridade

1.1.3.4 - Proteção de memória

1.1.3.5 - Testes

1.1.3.6 - Botão PARE

1.1.3.7 - Botão PREP

1.1.3.8 - Botão INTER

1.2 - Seleção para (EC)

1.2.1 - Seleção das duas saídas do mapeador para (EC)

1.2.2 - Seleção do endereço de retorno de uma micro-subrotina pa

ra o micro-programa principal;

1.2.3 - Endereço contido nos bits de 19 a 30 nas micro-instruções

de pulo (pulos dentro dos micro-programas ou para outras

micro-rotinas).

1.2.4 - Endereço proveniente do mapeador de interrupção

1.2.5 - Endereço proveniente do mapeador do painel

1.2.6 - Endereço da micro-instrução seguinte proveniente do soma

dor de + 1;

1.2.7 - Saída da Unidade Lógica e Aritmética

1.3 - Memória de Controle

- 1.3.1 - Micro-programa de Busca

- 1.3.2 - Micro-subrotinas de cálculo de endereço efetivo M0

- 1.3.3 - Micro-subrotinas de cálculo de endereço efetivo ME

- 1.3.4 - Micro-subrotinas de preparação de operando DEP

- 1.3.5 - Micro-subrotinas de preparação de operando PVES

- 1.3.6 - Micro-subrotinas de preparação de operando CURT

- 1.3.7 - Micro-subrotinas de preparação de operando IMED

- 1.3.8 - Micro-subrotinas de cálculo de endereço efetivo BE

- 1.3.9 - Micro-subrotina de preparação de operando PRVI

- 1.3.10 - Micro-subrotina auxiliar PEG

- 1.3.11 - Micro-subrotina auxiliar INIC

- 1.3.12 - Micro-subrotina auxiliar GUAB

- 1.3.13 - Micro-subrotina auxiliar MGUA

- 1.3.14 - Micro-programas de funções das instruções (68 módulos)

- 1.3.15 - Micro-programas de tratamento de interrupções

- 1.3.16 - Micro-programas do painel

- 1.3.17 - Carregador absoluto

- 1.4 - Registrador de endereços de controle (EC)

- 1.5 - Registrador de dados do controle (DC)

- 1.6 - Registradores de endereço de retorno de micro-subrotinas

(S0 e S1)

- 1.7 - Decodificadores

- 1.8 - Somador de "+1"

1.9 - Contador (CNTD)

1.10 - Lógica de testes de condições

2 - Unidade de Movimento de Dados:

2.1 - Registrador de Estado

2.2 - Registradores de propósito geral

2.3 - Base local

2.4 - Base de programa

2.5 - Limite de programa

2.6 - Registrador índice de pilha de contexto

2.7 - Registradores de rascunho (4)

2.8 - Registrador de dados D

2.9 - Registradores deslocadores P e Q

2.10 - Registrador I

2.11 - Registrador de endereços E

2.12 - Painel

2.13 - Unidade lógica e aritmética

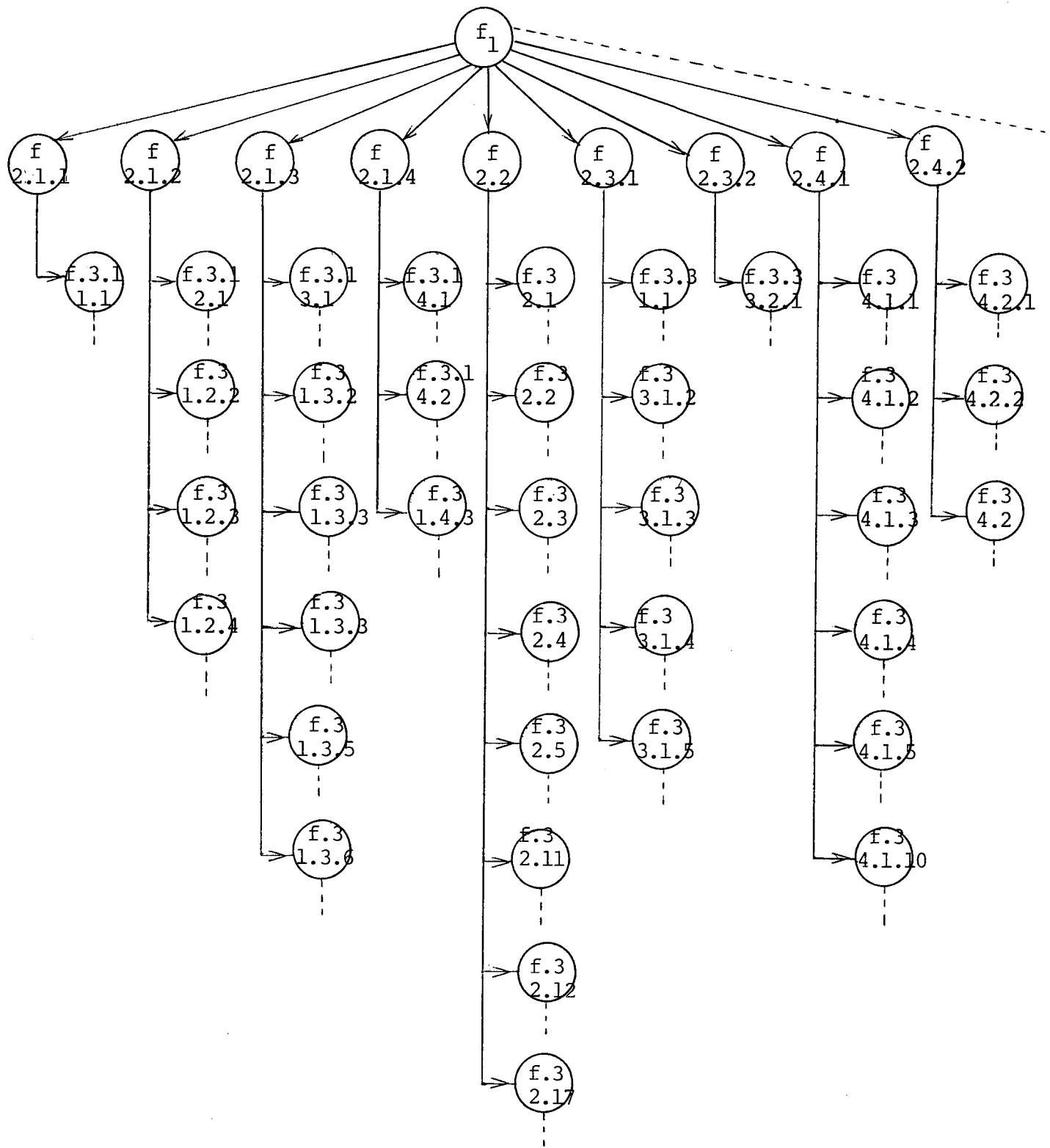

3 - Conjunto de Instruções do Processador G11

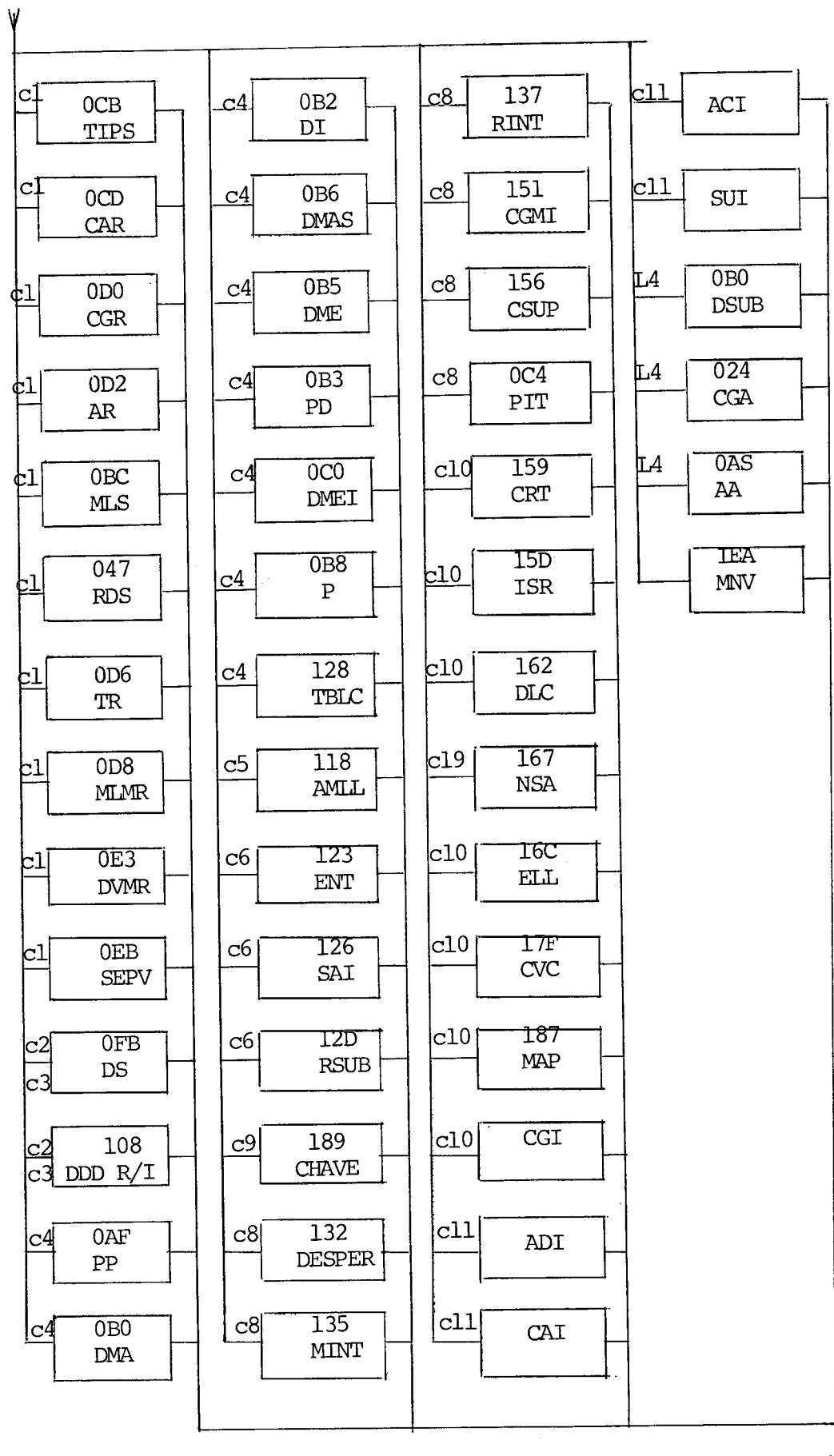

## CAPÍTULO III

TESTES DOS PONTOS DE FALHAS DO PROCESSADOR DE

INSTRUÇÕES DO MINI-COMPUTADOR G11

Os testes tem dois objetivos principais: detecção e diagnóstico com reparo da falha. Ao mesmo tempo seu uso deve ser facilitado de forma a auxiliar o operador de teste particularmente na fase de manutenção quando é necessário devolver a máquina funcionando no tempo mais rápido. Quanto maior for a substituição de operações manuais por operações automáticas mais rápido se processa a manutenção. A implementação do teste é desenvolvida levando em conta este aspecto.

Geralmente o teste de manutenção diagnostica a placa com defeito, no caso do G11 seria indicado o defeito na Unidade de Controle ou Unidade de Movimento de Dados. No entanto este teste está sendo projetado para as fases de desenvolvimento, produção, implementação e manutenção, o que exige uma indicação mais minuciosa do defeito. O ponto defeituoso pode ser um daqueles relacionados na seção 2.7 do capítulo anterior. Alguns pontos são estendidos no caso de haver necessidade e recursos disponíveis enquanto que outros são reunidos por falta de recursos de teste. O instrumento básico de teste é um programa formado por instruções do próprio conjunto de instruções do processador do mini-computador G11. O uso deste instrumento tomado como básico, exige cuidado especial para que o teste tenha capacidade de identificar pelo menos uma falha quando várias falhas ocorrem

simultaneamente. Esse ponto defeituoso pode ser então substituído ou reparado e o teste prosseguir com a finalidade de identificar as restantes da mesma forma que a primeira falha, conforme sugere Breuer et al [1]. Seguindo esta filosofia, se n falhas ocorrem simultaneamente, no máximo n iterações são necessárias para reparar as n falhas. O objetivo do projeto é obter um sistema que tenha a capacidade de ser diagnosticável com reparo das n falhas relacionadas na seção 2.7. Como foi observado anteriormente, esse número pode crescer ou decrescer de acordo com os obstáculos existentes. Na próxima seção, serão relacionados os testes necessários para cada ponto e os recursos que cada teste de cada ponto exige, recursos estes que precisam estar livres de erro.

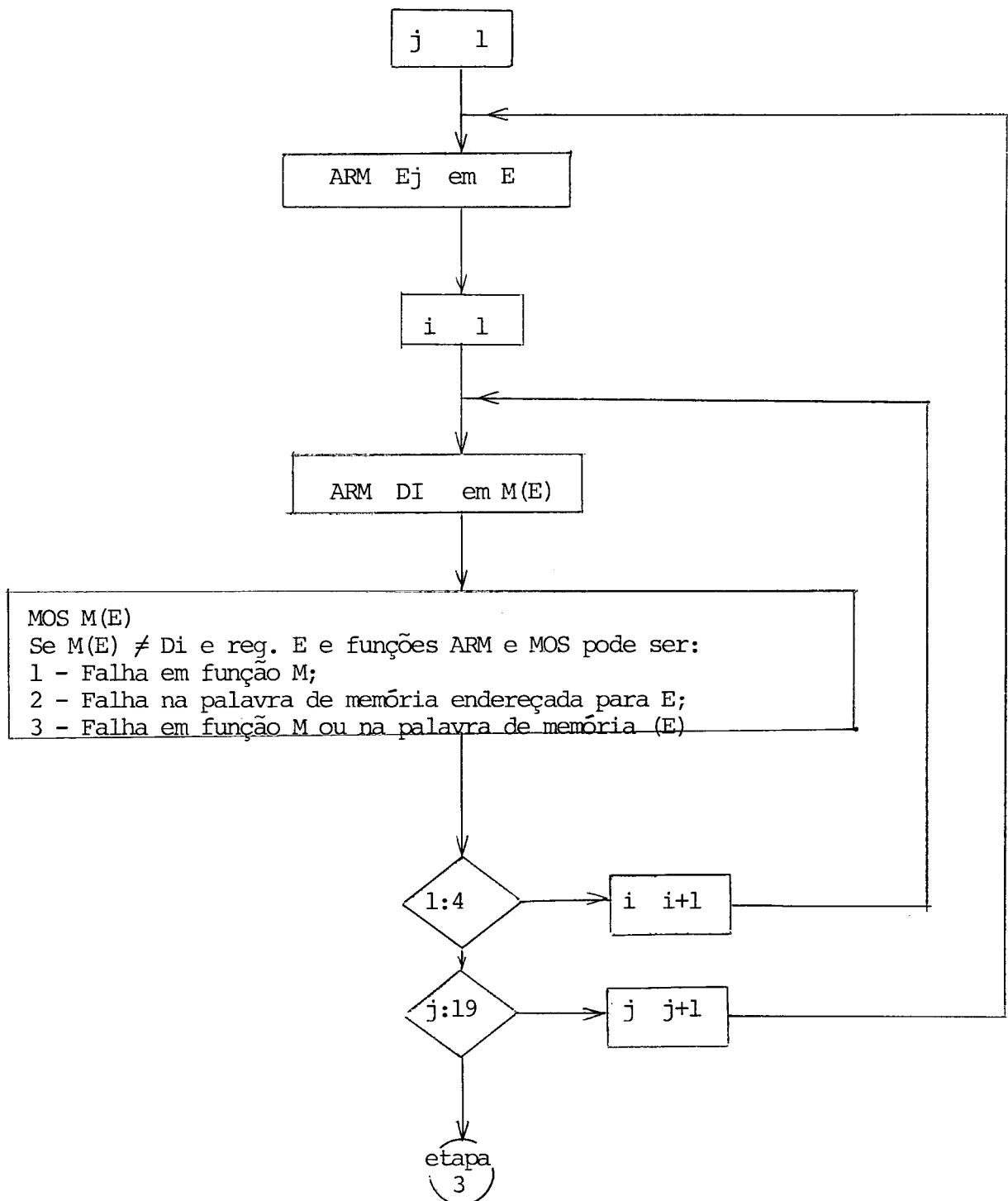

### 3.1 - Relação dos Testes para cada Ponto Sujeito a Falha

Para cada ponto deve ser feito um teste completo\*. Cada teste utiliza como recursos outros pontos que devem estar livres de erro para que o ponto em questão seja diagnosticado. Algumas medidas de precaução podem reduzir a frequência de fracassos nos testes que dependem de recursos que ainda não foram verificados. Uma das medidas é a ordem de realização dos testes de acordo com a quantidade de pontos envolvidos. Outra medida é a seleção de dois testes para cada ponto que tenham como característica o mínimo de coincidência entre os pontos utilizados.

---

\* ver definição de teste completo no capítulo 4.

Relação dos testes na ordem em que os pontos aparecem na seção 2.7.

## 1 - Testes da Unidade de Controle

### 1.1 - Testes do mapeador

#### 1.1.1 - Testes do mapeador de instruções

##### 1.1.1.1 - Testes do mapeador 1

###### 1.1.1.1.1 - Quando instrução curta sem M0

Testes do ponto 1.1.1.1.1:

1 - Execução de uma instrução curta pertencente ao formato C11 com bit 10 de I = 0.

Instrução "AC R, E"

Pontos ativados quando a instrução AC é executada:

- Micro-subrotinas da memória de controle: BUSCA; CURT; funções;

- Unidade de Controle;

- UMD;

2 - Execução de uma instrução curta pertencente ao formato C11 com bit 10 de I = 1

Instrução "CGI R, I"

Pontos ativados quando a instrução CGI é executada:

- Micro-subrotinas de memória de controle: BUSCA, IMED; funções;

- Unidade de Controle

- UMD

Pontos distintos entre os dois testes selecionados para o ponto 1.1.1.1.1.

1 - Função: O primeiro teste usa função AC

O segundo teste usa função CGI

2 - Micro-subrotinas de preparação de operando:

O primeiro teste usa CURT e o segundo usa IMED.

1.1.1.1.2 - Quando instrução curta com M0

1 - Execução de uma instrução curta pertencente ao formato C1 variando o campo M0 da instrução com todos os valores de  $(00)_2$  a  $(11)_2$ .

Instrução "AR R, RR"

Pontos ativados quando a instrução AR é executada: Micro-subrotinas da memória de controle: BUSCA, M0; funções:

- Unidade de Controle

- UMD

2 - Execução de uma instrução curta pertencente ao formato C10 variando o campo M0 da instrução com todos os valores de  $(00)_2$  a  $(11)_2$ .

Instrução CGMU RR

Pontos ativados quando a instrução CGMU é executada: Micro-subrotinas da memória de controle: BUSCA; M0; funções:

- Unidade de Controle

- UMD

Pontos distintos entre os dois testes selecionados para o ponto 1.1.1.1.2:

- 1 - Funções: O primeiro teste usa função AR

O segundo teste usa função CRT

1.1.1.1.3: Quando instrução longa sem M0

1 - Execução de uma instrução longa pertencente ao formato L2 variando o campo ME da instrução com todos os valores de  $(00)_2$  a  $(11)_2$ .

Instrução "AI I, RM"

Pontos ativados quando a instrução "AI I, RM" é executada:

Micro-subrotinas da memória de controle: BUSCA; ME; função de arm

- Unidade de Controle

- UMD

2 - Execução de uma instrução longa pertencente ao formato L3.

Instrução "DI RM"

Pontos ativados quando a instrução DI é executada: Micro-subrotinas da memória de controle: BUSCA; DEP; função DI

- Unidade de Controle

- UMD

Pontos distintis entre os dois testes selecionados para o ponto 1.1.1.1.3:

1 - Função: O primeiro teste ativa função de armazenamento

O segundo teste ativa função DI

2 - Micro-subrotinas de preparação de operando:

O primeiro teste ativa ME e o segundo ativa DEP.

1.1.1.2 - Teste do mapeador 2 (combinação de M0 e ME)

1 - Execuçao de uma instruçao longa pertencente ao formato Ll combinando todas as variações dos campos M0 e ME da instruçao.

Instruçao "A RR, RM"

Pontos ativados quando a instruçao A é executada: Micro-subrotinas da memória de controle: BUSCA; M0; ME; função:

- Unidade de controle

- UMD

2 - Execuçao de uma instruçao longa pertencente ao formato Ll combinando todas as variações dos campos M0 e ME da instruçao.

Instruçao "CG RR, RM"

Pontos ativados quando a instrução CG é executada:

- Micro-subrotinas de memória de controle: BUSCA; M0; ME ; Função.

- Unidade de Controle

- UMD

Pontos distintos entre os dois testes relacionados para o ponto 1.1.1.2:

1 - Funções: O primeiro teste ativa função de armazenamento

O segundo teste ativa função de carregamento

1.1.2 - Testes do mapeador de painel

1.1.2.1 - Testes da função ARM, realizados através de operação manual da função ARM.

Pontos ativados quando a operação manual ARM é realizada:

- Micro-subrotinas de memória de controle: PAIN

- Unidade de Controle

- UMD

1.1.2.2 - Testes da função MOS, realizados através de operação manual da função MOS.

Pontos ativados quando a operação manual MOS é realizada:

- Micro-subrotina de memória de controle: PAIN

- Unidade de Controle

- UMD

1.1.2.3 - Testes da função S (mostra reg. de estado), realizados através de operações manuais de ARM, MOS, EX (de instrução Armazenada em reg. I).

Pontos ativados quando a operação manual da função S é realizada:

- Micro-subrotina de memória de controle: PAIN

- Unidade de controle

- UMD

1.1.2.4 - Testes da função M, realizados através de operações manuais de ARM, MOS

Pontos ativados quando a operação manual da função S é realizada:

- Micro-subrotina de memória de controle: PAIN

- Unidade de controle

- UMD

1.1.3 - Testes do mapeador de interrupção

1.1.3.1 - Testes de interrupção por canal de E/S; não são realizados no sistema de testes do processador.

1.1.3.2 - Teste de interrupção por falha de alimentação.

1.1.3.3 - Testes de interrupção por erro de paridade; são realizados no sistema de testes de memória.

1.1.3.4 - Testes de interrupção por proteção de memória, realizados através de execução de instruções de desvio para endereços fora dos limites do programa.

Pontos ativados quando interrupção por falha de alimentação ou por proteção de memória ocorre:

- Micro-subrotinas da memória de controle

- Unidade de Controle

- UMD

1.1.3.5 - Testes de interrupção por rastreamento, realizado através de operação manual de rastreamento quando máquina está processando.

Pontos ativados quando interrupção por rastreamento é realizada: levando em conta que o rastreamento depende de um programa em execução, a ativação deste ponto depende da maioria dos recursos da máquina e é aconselhável sua verificação, sómente depois do programa de teste ter passado um número razoável de vezes.

1.1.3.6 - Teste do botão PARE, coincide com teste da função de painel PARE. É realizado através de operação manual.

Pontos ativados quando a operação manual da função PARE é realizada:

- Botão PARE; função de painel PARE

- Unidade de Controle

- UMD

1.1.3.7 - Teste do botão PREP, coincide com teste da função de painel PREP. É realizado através de operação manual.

Pontos ativados quando a operação manual da função PREP é realizada:

- Botão PREP; função de painel PREP

- Unidade de Controle

- UMD

1.1.3.8 - Teste do botão INTER, coincide com teste da função de painel INTER. É realizado através de operação manual.

Pontos ativados quando a operação manual da função INTER é realizada:

- Botão INTER; Função de painel INTER

- Unidade de Controle

- UMD

## 1.2 - Testes de seleção para (EC)

1.2.1 - Testes de seleção das duas saídas do mapeador de instruções através da aplicação dos testes selecionados para o mapeador de instruções.

1.2.2 - Teste da seleção do endereço de retorno de uma micro-subrotina para o micro-programa principal;

A observação da estrutura da micro-programação mostra que o uso de micro-subrotinas é intenso, a execução de cada instrução vai ativar no mínimo três micro-subrotinas principais (BUSCA, prepara operandos, execução da função) , portanto este ponto fica confundido com o restante dos outros pontos, utilizados por todas as instruções e quase todas as funções, pertencentes a unidade de controle.

1.2.3 - Testes da seleção do endereço contido nos bits de 19 a 30 nas micro-instruções de pulo (pulos dentro dos micro-programas ou para outras micro-subrotinas).

Este ponto apresenta o mesmo problema apontado no teste do ponto 1.2.2; fica impossível identificar através da instrução a origem do defeito, pois todas as instruções vão precisar ativar micro-instruções de pulo nas suas execuções.

1.2.4 - Teste da seleção do endereço proveniente do mapeador de interrupção.

Este ponto deve estar agregado aos pontos de interrupção do mapeador: canais, falha de alimentação, instrução inválida, etc ...

É impossível distinguir a falha na seleção e nas demais.

1.2.5 - Teste da seleção do endereço proveniente do mapeador do painel.

Este ponto deve estar agregado aos pontos de teste do mapeador do painel, pela mesma razão apontada no teste 1.2.4.

1.2.6 - Teste da seleção do endereço da micro-instrução seguinte proveniente do somador de +1;

Este ponto vai ser comum a todas as instruções ele é um recurso básico, se por acaso nenhuma instrução funcionar, um dos pontos com defeito é este. Não há meio de cercar este ponto.

1.2.7 - Teste da seleção da saída da unidade lógica e aritmética, através da ativação de todas as funções lógicas e aritméticas.

1.3 - Teste da memória de controle que é ativado, i.e., das micro-subrotinas armazenados;

1.3.1 - Testes da micro-subrotina de BUSCA;

1.3.1.1 - Testes do micro-programa de BUSCA de instrução curta;

- Execução de uma instrução curta pertencente ao formato C1 ;

instrução "AR R, RR"

Pontos ativados quando a instrução AR é executada:

- Micro-subrotinas da memória de controle: BUSCA, M0; função de ARM

- Unidade de Controle

- UMD

2 - Execução de uma instrução curta pertencente ao formato C11 ;

Instrução "CGI R, I"

Pontos ativados da memória de controle: BUSCA; IMED; função carrega

- Unidade de Controle

- UMD

#### 1.3.1.2 - Teste do micro-programa de Busca de instrução longa;

1 - Execução de uma instrução longa pertencente ao formato Ll ;

Instrução "A RR, RM"

Pontos ativados da memória de controle: BUSCA, M0; ME, função de ARM

- Unidade de Controle

- UMD

2 - Execução de uma instrução longa pertencente ao formato Ll;

Instrução "CG RR, RM"

Pontos ativados da memória de controle: BUSCA; M0; ME; função de CG

- Unidade de Controle

- UMD

#### 1.3.2 - Testes das micro-subrotinas de cálculo de endereço efetivo M0.

Execução de duas instruções curtas pertencentes aos formatos C1 e C10, variando o campo M0 de  $(00)_2$  a  $(11)_2$ .

1 - Instrução "AR R, RR"

2 - Instrução "CGMU RR"

Pontos ativados quando as instruções AR e CGMU são executadas:

- Micro-subrotinas da memória de controle: BUSCA, MO; funções

- Unidade de Controle

- UMD

Execução de duas instruções longas pertencentes aos formatos L1 e L4 fazendo variar os campos M0 e ME de  $(00)_2$  a  $(11)_2$ .

1 - Instrução "A RR, RM" pertencente ao formato L1.

2 - Instrução "CGA RR, RM" pertencente ao formato L4

Pontos ativados quanto as instruções são executadas:

- Micro-subrotinas da memória de controle: BUSCA, MO, ME, funções

- Unidade de Controle

- UMD

1.3.3 - Testes das micro-subrotinas de cálculo de endereço efetivo ME;

Execução de duas instruções longas pertencentes aos formatos L1 e L4 fazendo variar os campos M0 e ME de  $(00)_2$  a  $(11)_2$ ;

1 - Instrução "A RR, RM" pertencente ao formato L1

2 - Instrução "AI RR, RM" pertencente ao formato L2

Pontos ativados quando as instruções são executadas:

- micro-subrotinas da memória de controle: BUSCA; M0; ME ; função

- Unidade de Controle

- UMD

1.3.4 - Testes da micro-subrotina de preparação de operando DEP;

Execução de duas instruções pertencentes aos formatos C4 e L4;

1 - Instrução "PI" pertencente ao formato C4

2 - Instrução "DI" pertencente ao formato L4

1.3.5 - Testes de micro-subrotina de preparação de operando PVES; este ponto não é testado neste sistema, é agregado ao sistema de testes de periféricos;

1.3.6 - Testes de micro-subrotina de preparação de operando CURT;

Execução de duas instruções pertencentes ao formato C11 (curto, quando I10 = Ø).

1 - Instrução "AC"

2 - Instrução "CGC"

1.3.7 - Testes de micro-subrotinas de preparação de operando IMED:

Execução de uma instrução pertencente ao formato C11 e outra instrução pertencente ao formato L2.

1 - Instrução "CGI"

2 - Instrução "AI"

1.3.8 - Teste de micro-subrotina de cálculo de endereço efetivo BE:

Execução de duas instruções pertencentes ao formato longo L1 variando o campo BE de  $(00)_2$  e  $(11)_2$ .

1 - Instrução "AB"

2 - Instrução "CGB"

1.3.9 - Testes da micro-subrotina de preparação de operando PRVI.

OBS: Apenas as instruções PARE e CSUP serão testadas neste sistema.

1 - Instrução "PARE"

2 - Instrução "CSUP"

Os pontos relacionados anteriormente na seção 2.7 de 1.3.10 a 1.3.13 não merecem teste especial devido as instruções não possuirem capacidade de ativar estas micro-rotinas de forma aparente.

1.3.14 - Testes dos micro-programas de funções das instruções:

Cada função lógica e aritmética será testada esgotando todas as situações.

1.3.15 - Testes dos micro-programas de tratamento de interrupções.

Estes pontos estão sendo testados juntamente com o mapeador de interrupções e seleção. É impossível identificar cada etapa separadamente.

1.3.16 - Testes dos micro-programas do painel estes pontos estão sendo testados juntamente com funções do painel, mapeador, seleção, pelo mesmo motivo apontado em 1.3.15.

1.3.17 - Testes do carregador absoluto; após seu carregamento ,

alguns endereços selecionados com planejamento devem

ser mostrados via painel.

#### 1.4 - Registrador de endereços de controle (EC)

Este ponto é comum a todas as operações, seu mau funcionamento vai prejudicar toda a operação. Sua identificação automática é impossível.

Os pontos (1.5), (1.6), (1.7), (1.8), (1.9) e (1.10) apresentam as mesmas dificuldades apontadas para o ponto (1.4).

#### 2 - Teste da Unidade de Movimento de dados;

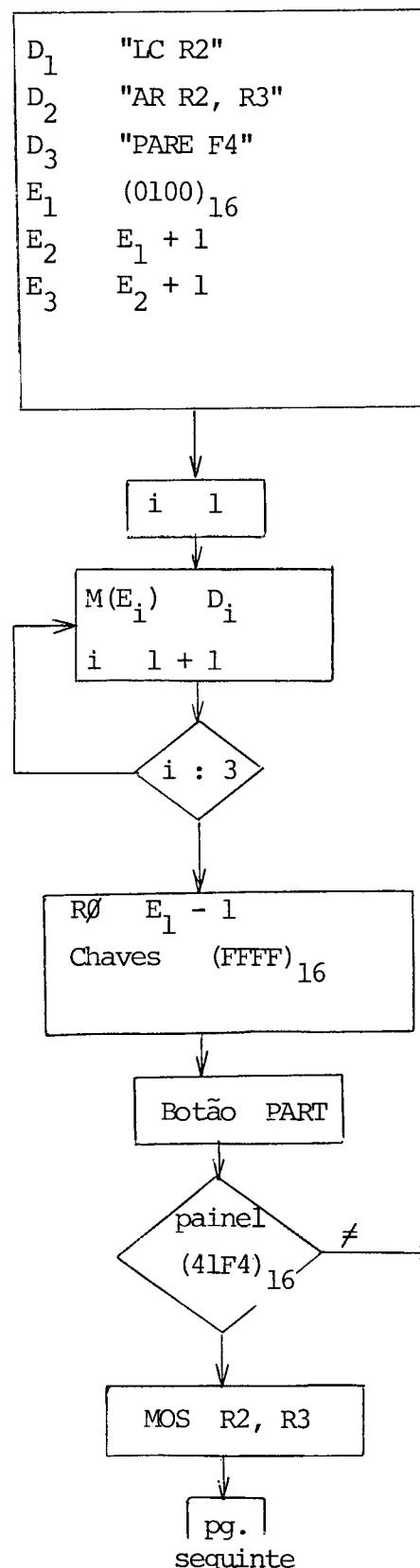

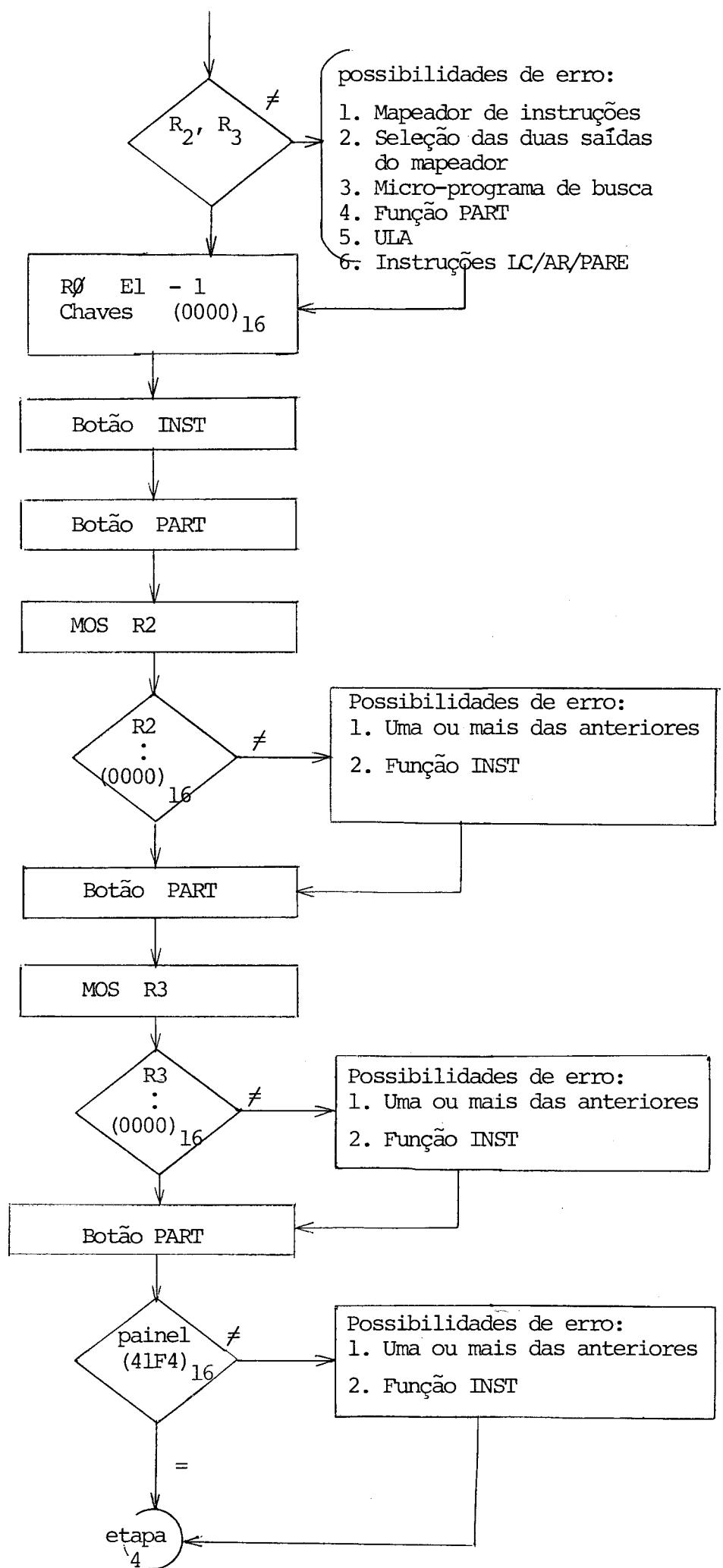

Os testes dos pontos da unidade de movimento de dados serão realizados por um conjunto de operações manuais permitidas através do painel.

#### 3 - Teste do conjunto de instruções

Os testes das instruções é realizado em duas partes. A primeira é a verificação intensiva das funções e a segunda a ativação de todas as instruções por uma situação apenas.

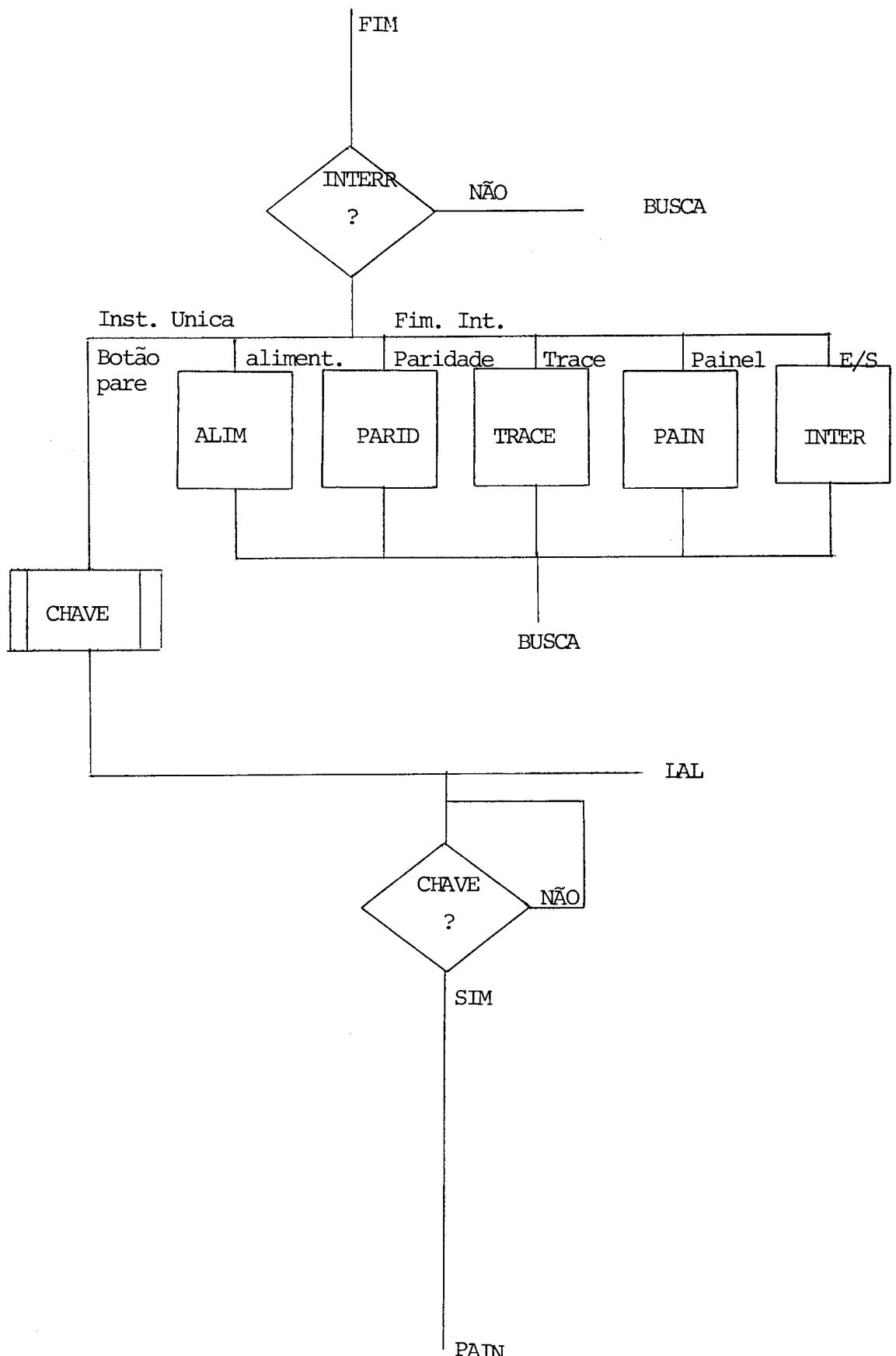

### 3.2 - Análise dos Testes Relacionados Quanto a Capacidade de Localização de Falhas

A observação dos testes do conjunto de pontos relacionados pertencentes a UCP e sujeitos a reparo quando apresentarem defeito, mostra que certos pontos tem características que merecem atenção especial.

Na análise foram encontradas quatro classes de pontos cujas características são relacionadas abaixo:

- 1 - Pontos que são ativados por qualquer operação manual ou automática. O mau funcionamento destes pontos compromete o funcionamento inteiro da UCP.

- 2 - Pontos que são ativados por qualquer operação automática. O mau funcionamento destes pontos compromete todas as execução das instruções.

- 3 - Pontos que são ativados pela mesma situação externa. Se um ou mais pontos desses apresenta mau funcionamento, é impossível localizar qual ou quais estão apresentando defeito.

- 4 - As instruções, cada instrução ativa uma série de pontos ao ser executada, podem ser consideradas como caminho de pontos, esses caminhos precisam ser testados, além disso os micro-programas de funções são particulares a uma pequena parcela de instruções.

Estas características sugerem uma nova relação de pontos e portanto uma nova organização do teste.

Nova Relação dos pontos baseada nas características apontadas:

Primeira classe de pontos: aqueles que são ativados por qualquer operação manual ou automática:

- 1 - Registradores de endereço de retorno de micro-subrotinas (S $\emptyset$  e S1).

- 2 - Seleção do endereço de retorno de uma micro-subrotina para o micro-programa principal.

- 3 - Seleção do endereço contido nos bits de 19 a 30 nas micro-instruções de pulo (pulos dentro dos micro-programas ou para outras micro-subrotinas).

- 4 - Seleção do endereço da micro-instrução seguinte proveniente do somador de +1.

- 5 - Somador de +1

- 6 - Parte comum da seleção

- 7 - Registrador de endereço de Controle (EC)

- 8 - Registrador de dados de controle (DC)

- 9 - Decodificadores

- 10 - Contador (CNTD)

- 11 - Lógica de testes de condições

- 12 - Seleção da saída de ULA e parte da ULA para operação manual

Segunda classe de pontos: aqueles que são ativados por qualquer operação automática. O mau funcionamento destes pontos compromete a execução das instruções. Não estão incluídos aqui os pontos relacionados no item anterior.

- 1 - Mapeador de instruções (parte comum a todas as instruções)

- 2 - Seleção das duas saídas do mapeador de instruções para (EC)

- 3 - Micro-programa de Busca

- 4 - Unidade de movimento de dados, parte da ULA para operação automática.

Terceira classe de pontos: aqueles que são ativados pela mesma situação externa. Situação provocada pelo programador (manual ou através de instrução). Se um ou mais pontos desses apresenta mau funcionamento, é impossível localizar a falha particular, apenas apontar o conjunto de possíveis pontos com falha.

- 1 - Situação externa: instrução curta sem M0

Pontos que são ativados apenas por esta situação externa

1. Parte do mapeador 1

2. Micro-subrotinas de preparação de operando CURT/IMED/PVES/PRVI/DEP (apenas pulos).

- 2 - Situação externa: instrução curta com M0

Pontos que são ativados apenas por esta situação externa

1. Parte do mapeador 1

2. Micro-subrotinas de cálculo de endereço efetivo M0

3 - Situação externa: instrução longa sem M0

Pontos que são ativados apenas por esta situação externa

1. Parte do mapeador 1

2. Micro-subrotinas de cálculo de endereço efetivo ME/DEP

(desvios)/IMED.

4 - Situação externa: instrução longa com M0 e ME/BE

Pontos que são ativados apenas por esta situação externa

1. Parte do mapeador 2

2. Micro-subrotinas de cálculo de endereço efetivo M0

3. Micro-subrotinas de cálculo de endereço efetivo ME/BE

5 - Situação externa: pressão do botão ARM no painel

Pontos que são ativados apenas por esta situação

1. Mapeador de painel da função ARM

2. Micro-programa do painel que trata função ARM

6 - Situação externa: pressão do botão MOS no painel

Pontos que são ativados apenas por esta situação

1. Mapeador de painel da função MOS

2. Micro-programa do painel que trata função MOS

7 - Situação externa: pressão do botão S no painel

Pontos que são ativados apenas por esta situação

1. Mapeador de painel para S

2. Micro-programa do painel que trata S

8 - Situação externa: pressão do botão M no painel

Pontos que são ativados apenas por esta situação

1. Mapeador de painel para M

2. Micro-programa do painel que trata M

9 - Situação externa: pressão do botão E no painel

Pontos que são ativados apenas por esta situação

1. Mapeador de painel para E

2. Micro-programa de painel que trata E

10 - Situação externa: pressão do botão I no painel

Pontos que são ativados apenas por esta situação

1. Mapeador de painel para I

2. Micro-programa de painel que trata I

11 - Situação externa: pressão do botão R no painel

Pontos que são ativados apenas por esta situação

1. Mapeador do painel para R

2. Micro-programas do painel que trata R

12 - Situação externa: pressão do botão CAR

Pontos que são ativados apenas por esta situação

1. Mapeador de painel para CAR

2. Micro-programa de painel que trata CAR

13 - Situação externa: pressão do botão PART

Pontos que são ativados apenas por esta situação

1. Mapeador de painel para PART

2. Micro-programa de painel para PART

14 - Situação externa: qualquer operação com o painel

Pontos que são ativados

1. Mapeador de painel (parte comum ativada por todas as situações que ativam as partes anteriores).

2. Seleção do endereço proveniente do mapeador de painel.

3. Parte comum dos micro-programas de tratamento das funções de painel

4. Registrador de painel da U.M.D.

15 - Situação externa: ocorrência de E/S

Pontos ativados apenas por esta situação

1. Mapeador de interrupção por CANAIS

2. Micro-programa que trata de interrupção por CANAIS

16 - Situação externa: ocorrência de falha de alimentação

Pontos ativados apenas por esta situação

1. Mapeador de interrupção por falha de alimentação

2. Micro-programa que trata de interrupção por falha de alimentação.

17 - Situação externa: ocorrência de erro de paridade

Pontos ativados apenas por esta situação

1. Mapeador de interrupção por erro de paridade

2. Micro-programa que trata de interrupção por erro de paridade.

18 - Situação externa: tentativa de acesso a endereço fora dos limites permitidos.

1. Mapeador de interrupção por proteção de memória.

2. Micro-programa que trata de interrupção por proteção de memória.

19 - Situação externa: interrupção de rastreamento

Pontos ativados apenas por esta situação

1. Mapeador de interrupção por rastreamento

2. Micro-programa que trata de interrupção por rastreamento

20 - Situação externa: pressão do botão PARE no painel

Pontos ativados apenas por esta situação

1. Mapeador de interrupção por PARE

2. Micro-programa que trata de interrupção por PARE

21 - Situação externa: pressão do botão PREP no painel

Pontos ativados apenas por esta situação

1. Mapeador de interrupção por PREP