PROJETO DE UMA UNIDADE DE CONTROLE

MICROPROGRAMADA PARA UMA UCP DE MÉDIO PORTE

Adriano Joaquim de Oliveira Cruz

TESE SUBMETIDA AO CORPO DOCENTE DA COORDENAÇÃO DOS PROGRAMAS DE PÓS-GRADUAÇÃO DE ENGENHARIA DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE MESTRE EM CIÊNCIAS (M.Sc.).

Aprovada por:

Ysmar Viana e Silva Filho

YSMAR VIANNA E SILVA FILHO

Presidente

Nelson Maculan Lb

NELSON MACULAN FILHO

Ivan da Costa Marques

IVAN DA COSTA MARQUES

RIO DE JANEIRO - RJ - BRASIL

NOVEMBRO DE 1979

CRUZ, ADRIANO JOAQUIM DE OLIVEIRA

Projeto de uma Unidade de Controle Microprogramada para uma

UCP de Médio Porte ( RIO DE JANEIRO ) 1979.

VII, 85 p., 29,7 cm (COPPE - UFRJ, M.Sc, Engenharia de Sistemas,

1975)

Tese - Universidade Federal do Rio de Janeiro - COPPE - UFRJ.

1. Microprogramação I. COPPE/UFRJ II Título (série).

A G R A D E C I M E N T O

Aos colegas ADALBERTO AFONSO BARBOSA, AGEU CAVALCANTI PACHEÇO JÚNIOR, ARMANDO DRUMMOND, JULIO SALEK AUDÉ, MARIO FERREIRA MARTINS, PAULO HENRIQUE DE AGUIAR RODRIGUES e ROGÉRIO ANTONIO SAMPAIO PARENTE VIANNA pelo auxílio técnico e apoio que deram durante o desenvolvimento do projeto.

A JAYME LUIZ SZWARCFITER e YSMAR VIANNA E SILVA FILHO pelo apoio dado ao projeto.

E finalmente aos estagiários ANTONIO CEZAR PEREIRA DE MENDONÇA UCHÔA, CARLO EMMANUEL TOLLA DE OLIVEIRA, CYBELE LUZANA REIS e JOSÉ RICARDO PEREIRA RIBEIRO pelo trabalho desenvolvido na fase de montagem de projeto.

R E S U M O

Este trabalho descreve uma Unidade de Controle projetada para um processador de médio porte atualmente em desenvolvimento no NCE/UFRJ.

Trata-se de uma Unidade de Controle microprogramada, com microprogramação fixa armazenada em memórias de leitura exclusiva, sendo a palavra de controle do tipo horizontal.

Inicialmente é apresentada uma visão geral do processador, seguida de uma descrição da Unidade Aritmética com o objetivo de mostrar os recursos que o microprogramador dispõe para desenvolver as micro-rotinas das instruções inteiras e de ponto flutuante.

O restante do trabalho é dedicado a apresentação e discussão dos circuitos da Unidade de Controle e dos microprogramas das instruções inteiras.

A B S T R A C T

This work presents a Control Unit design for a medium size processor under development at NCE/UFRJ.

Fixed microprogramming approach has been selected, using horizontal type control words.

A general survey about the processor is initially presented, followed by an Arithmetic Unit description in order to show the programmer's available features for integer and floating-point micro-routines implementation.

The last part presents and discusses Control Unit hardware and integer instructions microprograms.

I N D I C E

|                                                                   | Págs. |

|-------------------------------------------------------------------|-------|

| I - INTRODUÇÃO .....                                              | 1     |

| II - MICROPROGRAMAÇÃO .....                                       | 3     |

| 1 - Introdução .....                                              | 3     |

| 2 - Estrutura Básica dos Computadores .....                       | 4     |

| 3 - Unidade Aritmética .....                                      | 5     |

| 4 - Unidade de Controle .....                                     | 7     |

| III - DESCRIÇÃO GERAL DO SISTEMA .....                            | 11    |

| 1 - Introdução .....                                              | 11    |

| 2 - Características Gerais do Processador .....                   | 12    |

| 2.1 - Barras de Comunicação .....                                 | 12    |

| 2.2 - Modos de Operação .....                                     | 12    |

| 2.3 - Registros Referenciáveis por Instrução .....                | 12    |

| 2.4 - Modos de Endereçamento .....                                | 14    |

| 2.5 - Formato dos Operandos .....                                 | 16    |

| 2.6 - Conjunto de Instruções .....                                | 17    |

| 2.6.1 - Instruções de Um Operando .....                           | 18    |

| 2.6.2 - Instruções de Dois Operandos .....                        | 19    |

| 2.6.3 - Instruções de Desvio .....                                | 20    |

| 2.6.4 - Instruções de Execução Imediata .....                     | 20    |

| 2.7 - Unidade de Entrada e Saída .....                            | 20    |

| 2.7.1 - Introdução .....                                          | 20    |

| 2.7.2 - Sistema de Relocação de Endereços do<br>Processador ..... | 21    |

| 2.7.3 - Espaço de Endereçamento .....                             | 22    |

| 2.7.4 - Detecção de Erros .....                                   | 22    |

| 2.7.5 - Interrupções .....                                        | 23    |

| 2.8 - Sistema de Memória .....                                    | 23    |

| IV - ORGANIZAÇÃO DA UNIDADE ARITMÉTICA .....                      | 26    |

| 1 - Introdução .....                                              | 26    |

| 2 - Unidade Aritmética .....                                      | 27    |

| 3 - Memória Rascunho .....                                        | 27    |

| 4 - Registros EA e EB .....                                       | 29    |

| 5 - Registros A, B e AX .....                                     | 30    |

|                                                                   | Págs.  |

|-------------------------------------------------------------------|--------|

| 6 - Registros EV (Endereço Virtual) e RB (Registro de Barra ..... | 33     |

| 7 - Registro FPS .....                                            | 34     |

| 8 - Registro FEAT .....                                           | 34     |

| 9 - Constantes .....                                              | 36     |

| 10 - Macroinstruções .....                                        | 37     |

| 11 - Registro CP (Contador de Programa) .....                     | 38     |

| <br>V - ORGANIZAÇÃO DA UNIDADE DE CONTROLE .....                  | <br>39 |

| 1 - Introdução .....                                              | 39     |

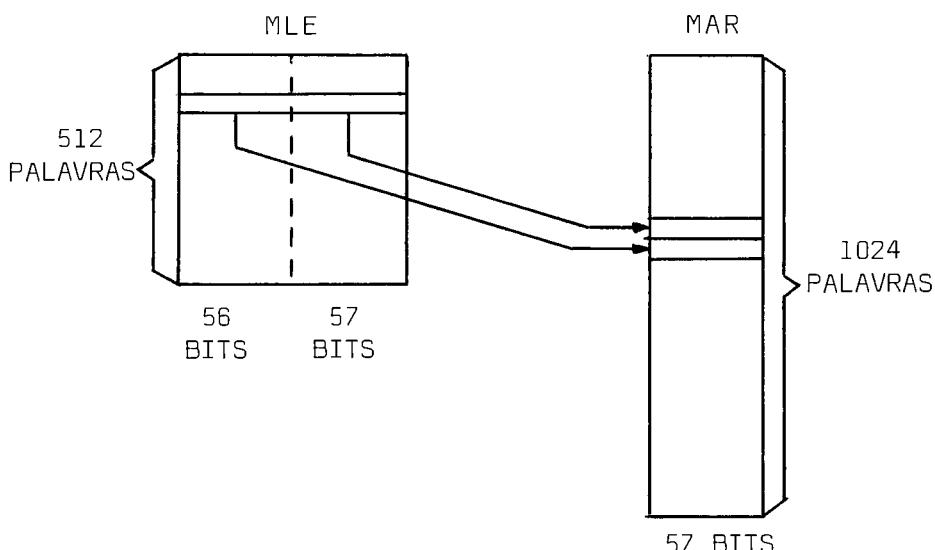

| 2 - Memória de Controle .....                                     | 39     |

| 3 - Palavra de Controle .....                                     | 41     |

| 4 - Sequenciamento da Memória de Controle .....                   | 46     |

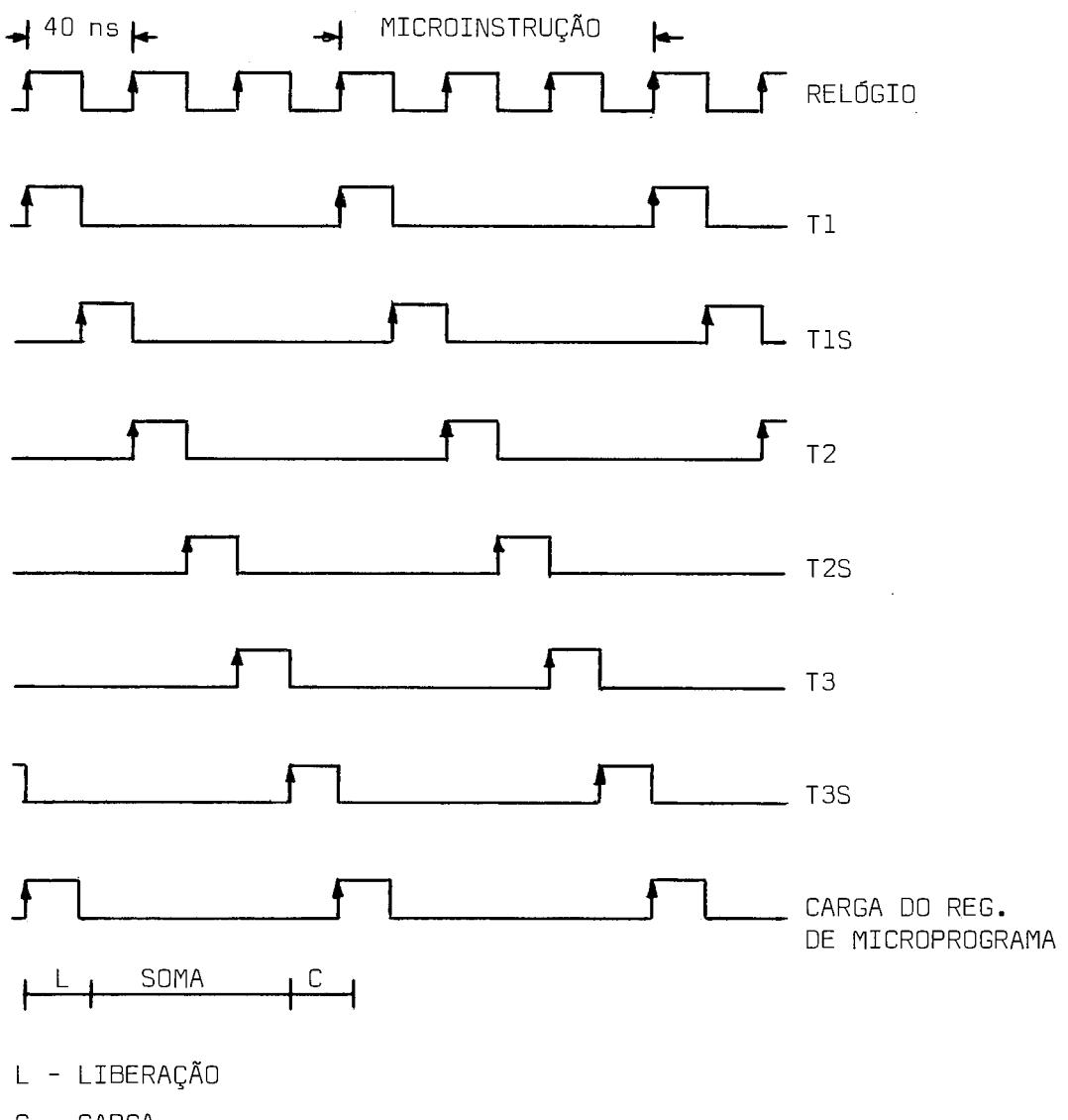

| 4.1 - Sincronização da Busca da Microinstrução .....              | 46     |

| 4.2 - Formação do Endereço .....                                  | 49     |

| 4.2.1 - Lógica de Desvios .....                                   | 49     |

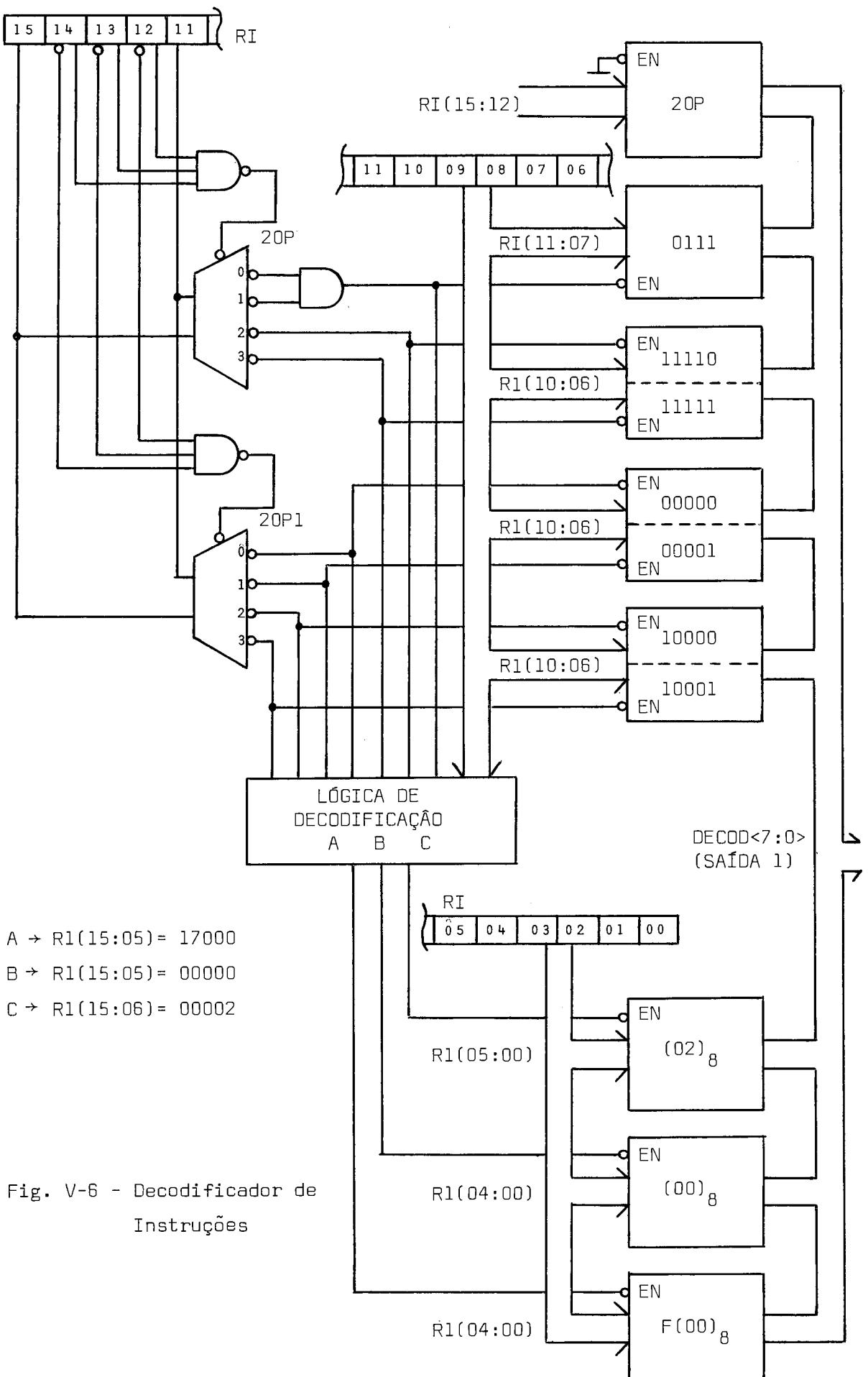

| 4.2.2 - Decodificador de Instruções .....                         | 52     |

| 5 - Registro de Endereço da Memória de Controle .....             | 56     |

| 6 - Circuito de Sincronização .....                               | 56     |

| <br>VI - MICROPROGRAMAÇÃO DA UNIDADE DE CONTROLE .....            | <br>61 |

| 1 - Introdução .....                                              | 61     |

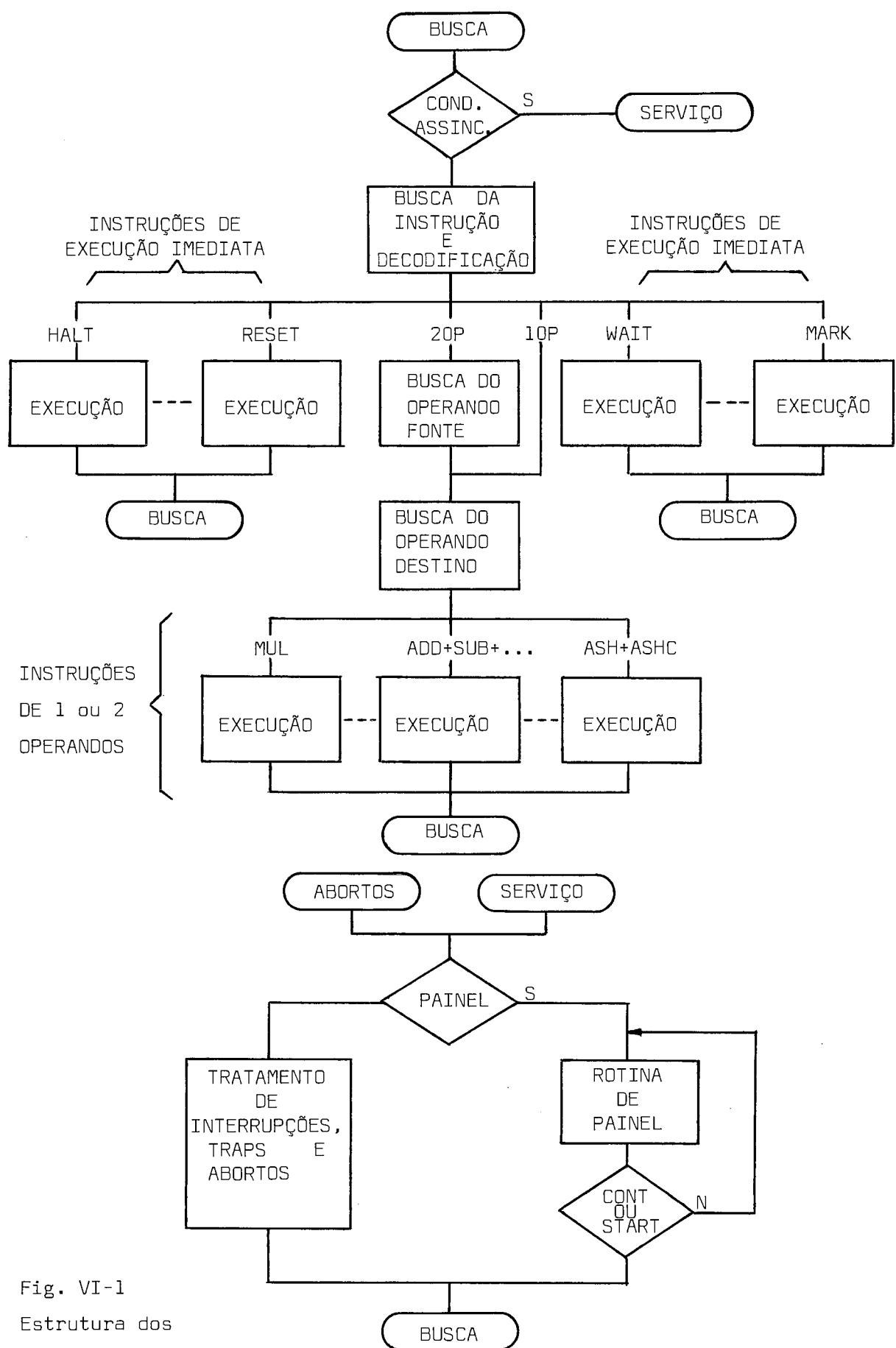

| 2 - Micro-Rotina de Busca e Decodificação das Instruções .....    | 62     |

| 3 - Micro-Rotina de Busca do Operando Fonte .....                 | 63     |

| 4 - Micro-Rotinas de Busca do Operando Destino .....              | 64     |

| 5 - Micro-Rotina de Serviço .....                                 | 64     |

| 6 - Micro-Rotina de Painel .....                                  | 66     |

| 7 - Micro-Rotina de Execução .....                                | 66     |

| <br>VII - CONSIDERAÇÕES SOBRE A IMPLEMENTAÇÃO DO PROJETO .....    | <br>68 |

## I - Introdução

Este trabalho apresenta o projeto de uma Unidade de Controle para uma Unidade Central de Processamento (UCP) de médio porte, compatível em "software" com o computador PDP 11/70 da Digital Equipment Corporation (D.E.C.), que vem sendo desenvolvida no Núcleo de Computação Eletrônica da U.F.R.J. (NCE).

A idéia de se construir uma UCP de médio porte surgiu da necessidade que o NCE sentia de contribuir para o esforço que algumas Universidades e instituições faziam e continuam a fazer para criar no país tanto a tecnologia necessária para o projeto e construção de equipamentos digitais como pessoal qualificado a manter e ampliar este esforço.

A escolha de um computador de médio porte era justificada pelo estágio em que se encontrava na época o conhecimento sobre projetos digitais no Brasil. A experiência acumulada pelas Universidades havia resultado no mini-computador G-10, projeto conjunto da USP e PUC-RJ, que estava concluído e pronto para ser industrializado. Deste modo uma UCP de médio porte seria um passo à frente natural dado pelos técnicos objetivando ampliar a fronteira dos conhecimentos até uma faixa superior de computadores.

As iniciativas para a industrialização do G-10 resultaram infrutíferas por diversos motivos. No plano técnico havia o argumento de que devido ao fato do computador ter um "software" novo, era pouco conhecido dos usuários e insuficientemente testado. Este argumento que em parte era verdadeiro estabelece um círculo vicioso; não se usa o computador porque seu "software" não foi testado, não são feitos testes definitivos porque não é nem será usado, daí não se constrói nada. Para romper este esquema é necessário o estabelecimento de uma política de desenvolvimento que esteja voltada para interesses nacionais dando apoio a tecnologia produzida no país. Entretanto estas iniciativas não foram de todo frustradas, pois uma das consequências das discussões iniciadas com a industrialização do G-10 foi a resolução da CAPRE que reservava para a indústria nacional a faixa dos mini-computadores.

Deste argumento usado contra o G-10, ressalvando como já mostramos que é possível contorná-lo, tiramos um dos motivos que nos levaram a projetar um computador compatível em

"software" com outro já testado e de amplo conhecimento dos usuários. Assim sua industrialização poderá ser feita sem os supostos inconvenientes que um "software" totalmente novo traz.

O segundo motivo que nos levou a fazer a opção por uma CPU compatível, está relacionado com uma limitação do próprio NCE. Não havia na instituição pessoal suficiente para desenvolver e testar em curto prazo um "software" integralmente original.

A necessidade de terminar o projeto em curto prazo tem a sua justificativa na experiência adquirida durante a luta pela implantação de uma indústria nacional de mini-computadores, na qual o G-10 teve grande importância. A natural ampliação desta luta para outras faixas de computadores objetivando abrir espaço para o crescimento das indústrias nacionais, pode ter seu caminho facilitado pela existência de projetos nacionais em funcionamento.

Deste modo a opção de fazer uma UCP "software" compatível pode ser discutida em virtude dos prejuizos evidentes que traz ao desenvolvimento do "software" básico no Brasil. Entretanto, devido as condições de recursos do NCE e aos fatores externos, esta nos pareceu a maneira mais eficiente que dispúnhamos para contribuir ao esforço de criação de uma indústria nacional de computadores. Neste nacional incluímos os pressupostos que a palavra exige: desenvolvimento de programas e circuitos no país; satisfação de necessidades reais da sociedade brasileira, discutidas em debates abertos e amplos.

## II - MICROPROGRAMAÇÃO

### 1- Introdução

Um considerável avanço nas técnicas de projeto de unidades de controle para computadores digitais, ocorreu quando da idealização da microprogramação. A ideia, que consiste basicamente em substituir os circuitos convencionais anteriormente usados na unidade de controle por uma memória onde é armazenada a lógica de controle do computador (a microprogramação), é normalmente atribuída a Wilkes<sup>1,2</sup>. O principal interesse de Wilkes e sua equipe era organizar os métodos de projeto até então utilizados, antevendo as vantagens que um método ordenado e sistemático traria tanto ao próprio projeto como a sua posterior manutenção. Em artigo publicado em 1958 por Wilkes, Renwick e Wheeler<sup>3</sup>, há este comentário sobre o problema: "Em muitas máquinas o projeto da unidade de controle tem sido feito por meio de métodos semi-empíricos, e os circuitos resultantes, embora possam ser eficientes, são complexos e não sistemáticos, e poderiam requerer alterações consideráveis se qualquer mudança apreciável tivesse de ser feita no conjunto de instruções da máquina".

Apesar das vantagens técnicas que a microprogramação possui, somente na década de 60 este método de projeto começou a ser aplicado por grandes fabricantes em computadores comerciais. Este crescimento de interesse ocorreu a medida que a microprogramação passou a ser economicamente superior aos projetos com lógica convencional. Esta superioridade econômica se tornou possível entre outras razões pelo aparecimento de memórias de leitura exclusiva (MLE), rápidas e confiáveis para aplicação na indústria.

A microprogramação possibilitou implementar economicamente, por exemplo, um mesmo conjunto de instruções (códigos de operações) para toda uma linha de computadores, mesmo os menores. Desta maneira podemos ter computadores com organizações internas e tecnologias completamente diferentes e que são arquiteturalmente compatíveis. Aqui o termo arquitetura é usado para significar os aspectos do computador que são visíveis ao programador, incluindo então, registros, modos de endereçamento e instruções. Organização, por outro lado se refere a um nível abaixo deste e está significando os registros de trabalho, unidade arit-

mética, barras de comunicação de dados, etc, que são usualmente transparentes ao programador.

A microprogramação também tornou possível computadores rodarem com pequenas ou nenhuma alteração, programas de máquinas de linhas anteriores eliminando a necessidade de reprogramação. Estes tipos de compatibilidades, com linhas anteriores e acima e abaixo em uma mesma linha, receberam farta publicidade dos fabricantes junto aos usuários pelas inúmeras vantagens que traziam, demonstrando a importância da microprogramação. Finalmente, também foram conseguidas compatibilidades entre computadores de diferentes fabricantes.

Até aqui fizemos referência a microprogramação somente como uma ferramenta do projetista de computadores. Realmente as primeiras máquinas foram projetadas com o objetivo principal de implementar uma arquitetura particular, não havendo interesse em generalizar o uso da microprogramação levando-a até os usuários. As modificações introduzidas nos microprogramas com a finalidade de emular outras máquinas eram implementadas em MLEs e feitas pelos próprios fabricantes. Entretanto, a introdução de memórias de controle possíveis de serem alteradas, fez com que a microprogramação evoluísse de campo de trabalho dos projetistas de computadores para uma área de interesse de toda comunidade de usuários. Recentemente, começaram a aparecer máquinas que são completamente microprogramáveis e cujas arquiteturas são projetadas para permitir microprogramas de uso geral, podendo então o microprogramador escolher o conjunto de instruções mais apropriado para a sua aplicação.

Como vimos a microprogramação, para surpresa de muitos que a julgavam uma idéia nova está presente de um modo ou de outro, há quase três décadas na área de computação. Há grande quantidade de textos publicados, cobrindo todas as áreas de aplicação da microprogramação e descrevendo as principais idéias e conceitos. Entretanto com o objetivo de estabelecer uma perspectiva comum, este capítulo apresenta os conceitos básicos da microprogramação e algumas definições que serão usadas no restante do trabalho.

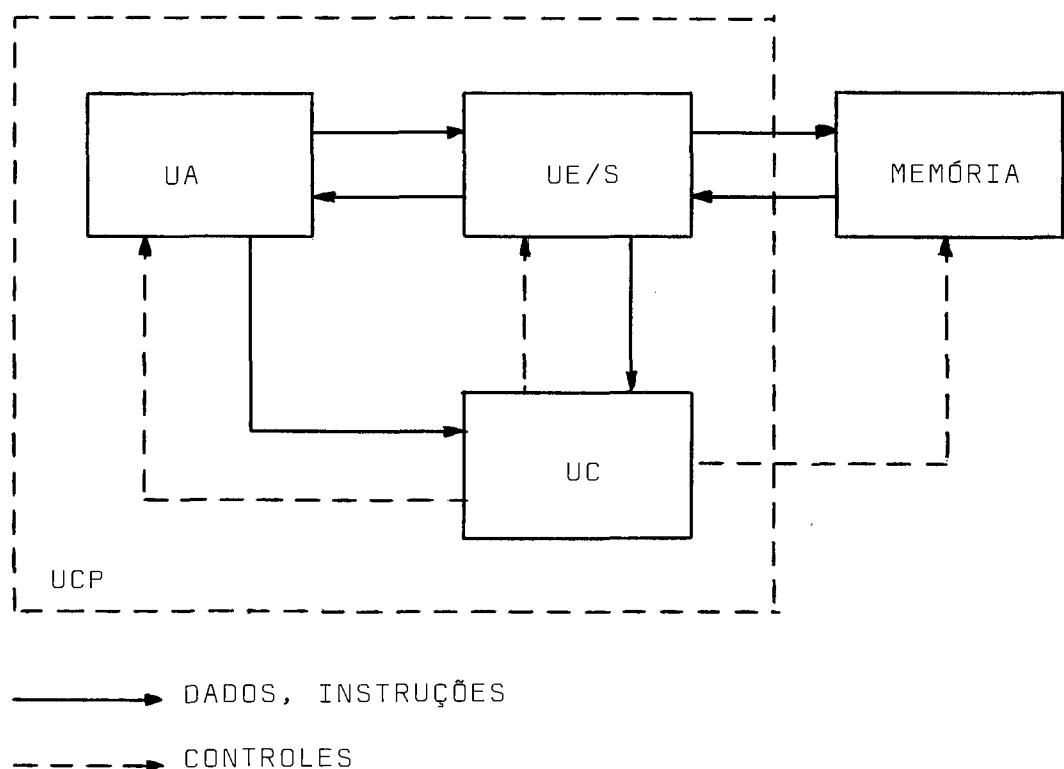

Um computador digital moderno e em geral qual quer sistema que trate informação, pode ser dividido em quatro unidades com atividades distintas: Unidade Aritmética (UA), Unidade de Entrada e Saída (UE/S), Unidade de Controle (UC) e Memória. Estas unidades comunicam-se entre si, trocando dados, instruções e controles como está representado na figura II-1. Os dois primeiros tipos de informação fazem parte da rotina de trabalho de todos que usam computadores, enquanto que os sinais de controle são quase sempre familiares somente aos técnicos que trabalham ao nível dos circuitos da máquina.

fig.II-1 - Elementos de um Computador Digital.

O que é normalmente chamado de Unidade Central de Processamento (UCP) do computador é composto da UA, UE/S e UC. As duas primeiras unidades estão relacionadas às transformações e movimentações de dados que ocorrem durante o processamento e a última com o controle da UCP.

A Unidade Aritmética é constituída na maioria das máquinas de elementos armazenadores, circuitos que realizam operações e caminhos de dados. Os elementos armazenadores incluem registros para operandos e endereços, memórias e elementos que armazenam condições para testes (ocorrência de transbordo, pedidos de interrupção, etc). Dos circuitos que realizam operações o mais importante é o coração da UA, é a chamada Unidade Aritmética e Lógica (UAL). Na UAL são executadas as operações básicas, que correspondem ao repertório de funções da UCP ao nível de circuitos. Este repertório consiste de operações como, SOMA, SUBTRAÇÃO, E, OU, COMPLEMENTAÇÃO, etc, e a partir destas podem ser sintetizadas operações mais complexas. Normalmente também há circuitos que realizam operações especializadas como contagem, comparações de endereços e dados. O restante da UA é constituido de multiplexadores, caminhos de dados e portas lógicas, que servem para interconectar os circuitos armazenadores e os que realizam as operações.

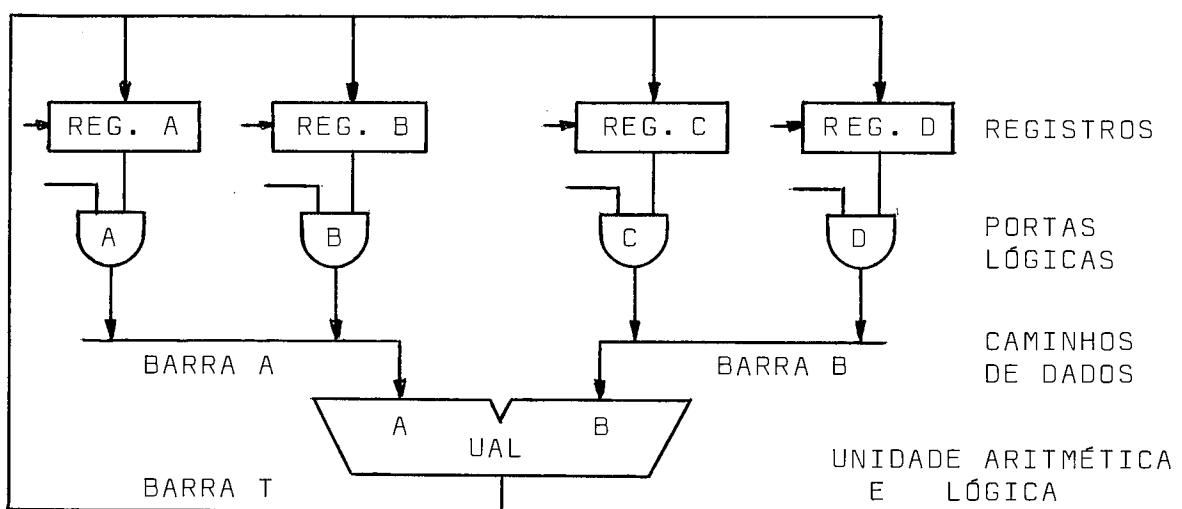

A figura II-2 mostra uma UA simples. Neste exemplo, a entrada A da UAL pode receber os registros A ou B através do caminho A; a entrada B, os registros C ou D através do caminho B; a saída UAL pode ser carregada em qualquer dos registros através do caminho T; e assumiremos que a UAL pode executar diversas funções básicas. É evidente que para a UA realizar uma

fig. II-2 - Unidade Aritmética

operação qualquer, por exemplo somar os conteúdos dos registros A e C, sinais de controle devem ser aplicados as portas lógicas A e C de modo que os dados sejam liberados nos caminhos apropriados e programar a UAL para realizar a operação selecionada. Como é necessário esperar um espaço de tempo para que os dados atravessem as portas, caminhos e que a operação seja realizada, os sinais devem permanecer ativos este tempo. Geralmente é escolhido o tempo que é gasto na operação mais demorada através da UA como o ciclo da máquina. Operações mais complexas são realizadas com um número inteiro destes ciclos. O estado em que está o conjunto dos sinais de controle durante um ciclo, definem o que se costuma chamar de estado da máquina.

#### 4- Unidade de Controle

Todos os sinais que controlam a operação da UA e de toda UCP, provem da Unidade de Controle. Para emitir estes sinais, a UC recebe informações da Memória que especificam que operação deve ser realizada e a localização dos dados que serão operados. De posse destas informações a UC determina (decodifica) exatamente qual é a instrução, comanda as movimentações e transformações com os endereços e operandos e ao final da execução dá inicio ao processo de busca de uma nova instrução. Cada instrução é então um pedido a UC para ativar os circuitos do sistema que realizam as operações lógicas ou aritméticas e abrir e fechar certas portas lógicas que permitem os dados caminharem pelas diversas unidades, isto durante um número pré determinado de ciclos. Podemos afirmar que as tarefas da UC são de dois tipos: definir os sinais que serão ativados durante um ciclo da máquina e determinar qual será o próximo estado.

Em uma UC de controle convencional estas tarefas são realizadas por um conjunto de circuitos lógicos combinacionais e sequenciais, espalhados pelo processador, que funcionam como uma máquina de número finito de estados. Como vimos este tipo de UC tem um método de projeto não sistemático, que traz problemas durante a própria fase de projeto e depois na manutenção. Wilkes<sup>1</sup> propôs então uma alternativa que visava eliminar estas dificuldades.

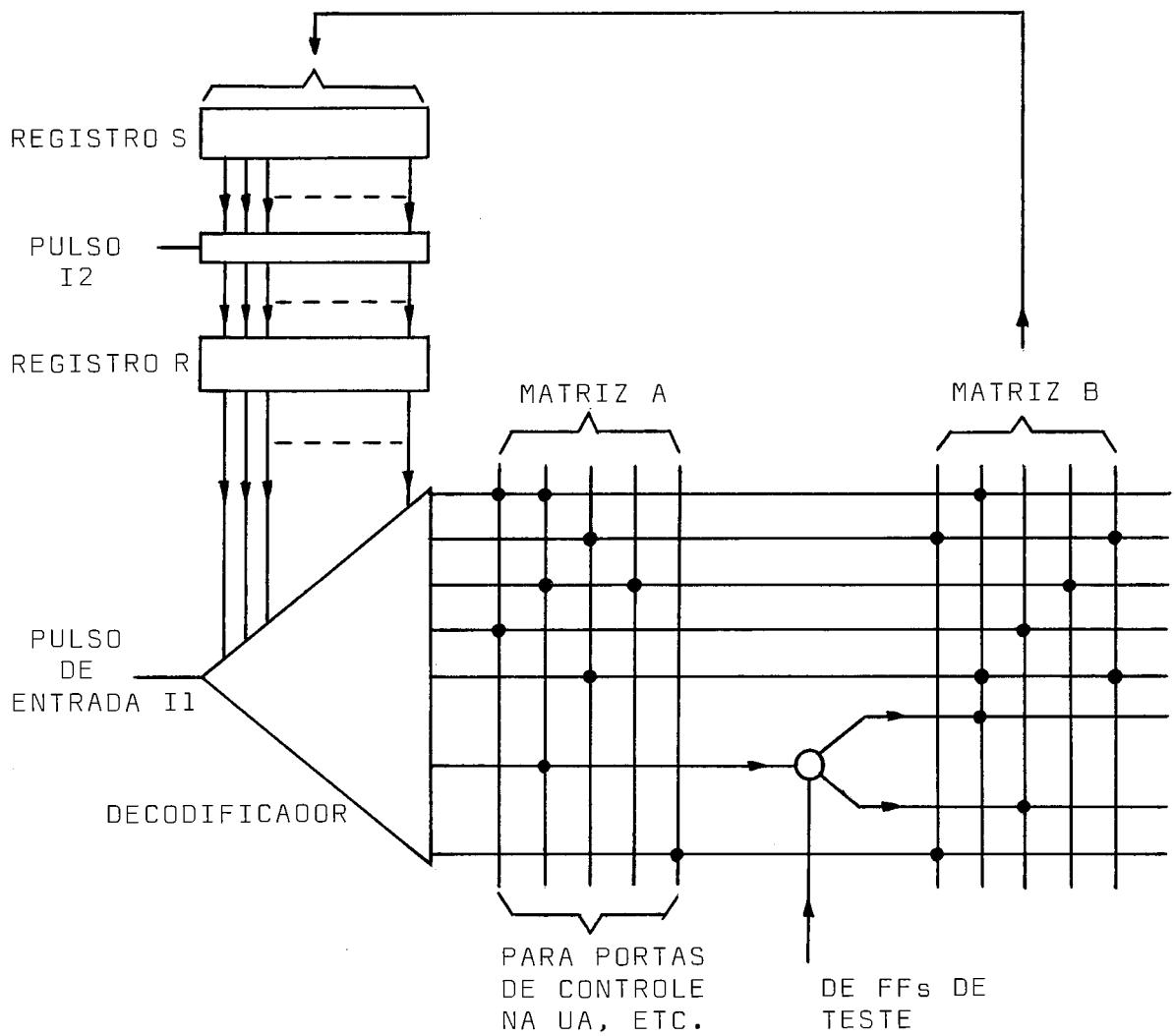

Como já observamos, a execução de uma instrução é dividida em uma série de ciclos, onde são realizadas operações básicas (chamadas micro-ordens), comandadas por sinais oriundos da UC. Tais micro-ordens podem por exemplo comandar uma transferência entre registros, ordenar uma soma, etc, por meio da abertura e fechamento de certas portas lógicas. A idéia básica de Wilkes era controlar estas portas, registros, etc. através de linhas de controle, cujo estado podendo ser representado por zero ou um, seria armazenado em uma matriz. O esquema original de Wilkes está mostrado na figura II-3. Ele consiste de uma matriz

fig.II-3 - Unidade de Controle no Modelo de Wilkes

de controle A, outra de sequenciamento B, circuitos de sincroniso

mo e um decodificador (foram originalmente sugeridas matrizes de diodos, embora Wilkes tenha apontado outras soluções<sup>3</sup>). Na matriz A as linhas verticais são conectadas a uma única porta de controle no sistema, podendo então estas portas serem abertas ou fechadas simplesmente ativando-se a linha de controle correspondente na matriz A. O circuito decodificador recebe a saída do registro R, decodifica seus n bits e seleciona uma entre  $2^n$  linhas horizontais para ser ativada, isto é, em cada ciclo o decodificador permite que seja ativada somente uma linha. A linha é ativada por meio de um pulso de sincronismo (Il) vindo do decodificador. Ela por sua vez, de acordo com a disposição dos diodos na matriz, ativa um conjunto de portas lógicas no sistema, fazendo com que sejam realizadas as operações elementares apropriadas. A linha horizontal pode ser entendida como uma instrução da Unidade de Controle ou uma microinstrução.

O pulso de sincronismo passa também através da matriz B, e a sua saída é armazenada no registro S. No começo de um novo ciclo o conteúdo de S é transferido para o registro R, que apontará então a nova microinstrução a ser executada.

Há uma certa analogia na maneira como a máquina executa os diversos passos requeridos para implementar uma instrução e a maneira com que são executadas as diversas instruções que constituem um programa. Isto sugeriu o termo microprogramação como definição do processo de desenvolver um conjunto de microinstruções (o conteúdo da matriz de controle), utilizadas para controlar as operações dos diversos elementos dentro da UCP, de modo que seja executado o conjunto de instruções da máquina.

Uma outra idéia sugerida por Wilkes e Stringer<sup>4</sup> refere-se a necessidade de haver desvios condicionais nos microprogramas. A sugestão era fazer com que o endereço da próxima microinstrução a ser executada, fosse função de um flip-flop que armazenaria a condição a ser testada. Dependendo do estado deste flip-flop, um de dois endereços é selecionado (ver fig II-3), podendo-se deste modo testar por exemplo, bits de um multiplicador durante a microprogramação de uma instrução de multiplicação. Ainda de Wilkes, foi a sugestão de fazer com que o conteúdo do registro S, pudesse ser carregado, ou com a saída da matriz B ou a partir outra fonte, que poderia ser o próprio código de operação da instrução. Deste modo seria eliminada a necessidade de um cir-

cuito decodificador de instruções. Também foi especulado que poderia haver módulos de matrizes intercambiáveis, cada um com microprogramação para conjuntos de instruções diferentes. Deste modo cada usuário poderia escolher o conjunto de instruções mais apropriado para sua aplicação. Além dessas modificações, outros esquemas foram sugeridos por Wilkes e sua equipe.

Existem vários parâmetros que são utilizados para descrever as microinstruções. Apesar de não haver definições precisas sobre os seus significados eles contém informações significativas sobre as microinstruções. Geralmente são usados para descrever as microinstruções o seu comprimento, a quantidade de informação contida na palavra e o seu grau de codificação, a organização da informação dentro da microinstrução e a sincronização da execução. Todos esses parâmetros serão apresentados mais adiante durante a descrição do projeto da Unidade de Controle, junto com o seu enquadramento dentro destes parâmetros.

### III - DESCRIÇÃO GERAL DO SISTEMA

#### 1 - Introdução

Com a finalidade de apresentar uma visão geral da arquitetura do sistema e da organização interna da UCP, este capítulo faz uma breve apresentação do projeto como um todo, mostrando suas características mais importantes e destacando os aspectos principais existentes nos projetos da Unidade Aritmética, Unidade de Entrada e Saída, Sistema de Memória e Painel.

O fato de se ter como proposta a realização do projeto de uma UCP compatível em "software" com o PDP-11/70 da D.E.C. não implicou, de forma alguma, na adoção de uma filosofia de trabalho que não considerasse importante a busca de soluções novas e criativas para a execução do projeto. Apenas no plano de definição da máquina, do ponto de vista do programador é que poucas alterações puderam ser feitas. No entanto sua organização interna, isto é, os circuitos da Unidade de Controle, Unidade Aritmética, Unidade de Entrada e Saída e Sistema de Memória são completamente diferentes, resultado de um novo projeto.

A exigência de compatibilidade em "software" com o PDP 11/70 determinou duas diretrizes para o projeto. A primeira delas é que a UCP a ser projetada fosse capaz de executar todo o conjunto de instruções do PDP-11/70 e que a execução de qualquer instrução do conjunto provocasse, do ponto de vista do programador, efeitos idênticos nesta UCP e no PDP 11/70. A segunda obriga que a UCP opere com os registros internos, indicadores de erro, "status" e condições de operação do sistema, de forma idêntica ao PDP-11/70.

Uma terceira diretriz para o projeto foi definida pelo fato de que seria mais econômico e prático permitir que a esta UCP pudessem ser conectados todos os periféricos da D.E.C., sem a necessidade de utilização de circuitos especiais. A adoção desta idéia traz como consequência a utilização de um protocolo de troca de sinais com periféricos idêntico ao empregado no PDP-11/70.

A obediência a estas diretrizes durante o projeto, permitirá a utilização da UCP sob controle de Sistemas Operacionais desenvolvidos pela D.E.C para computadores da linha PDP-11/70, bem como o acoplamento a ela de uma grande variedade de

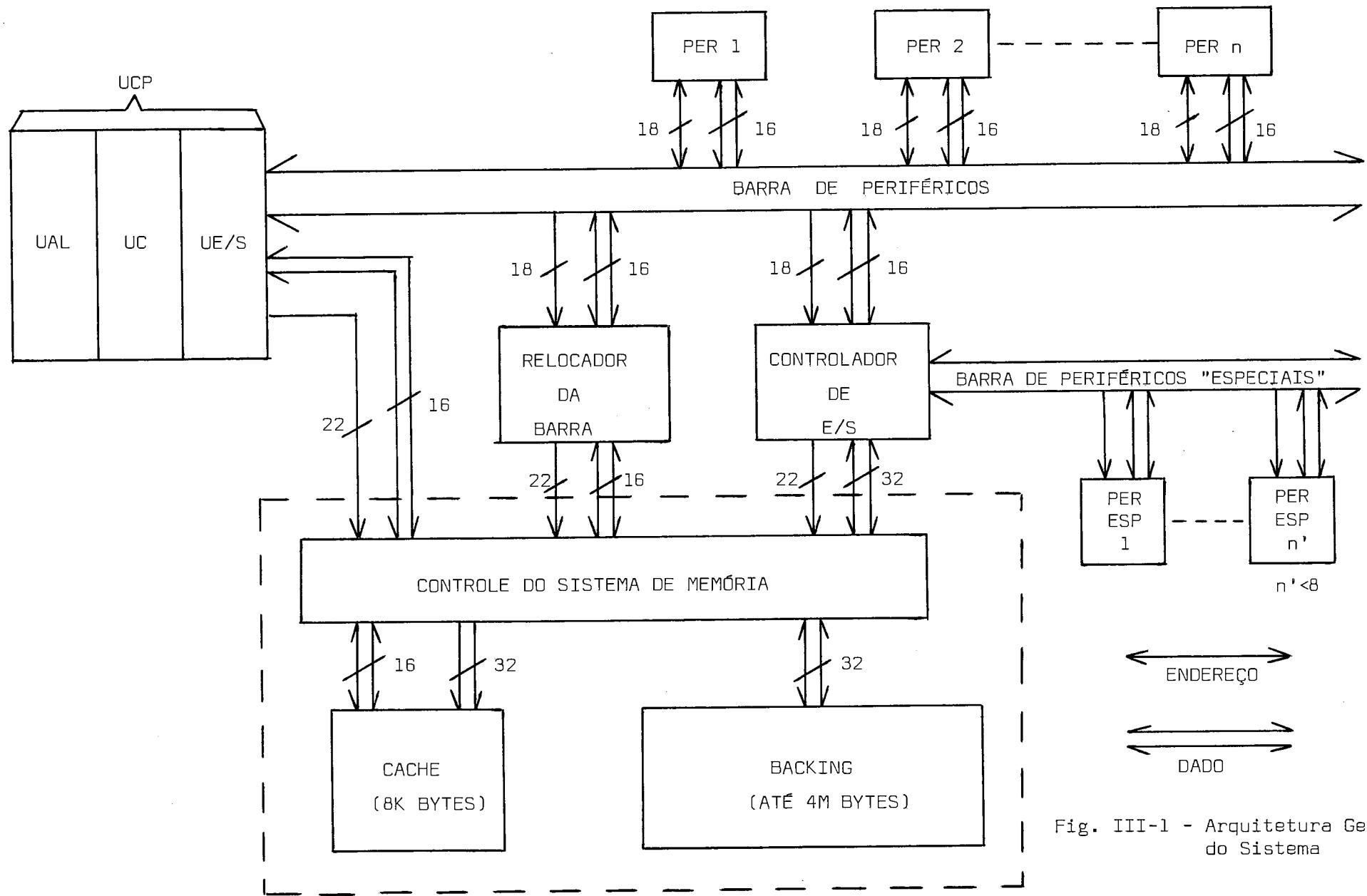

Fig. III-1 - Arquitetura Geral do Sistema

periféricos.

## 2- Características Gerais do Processador

### 2.1- Barras de Comunicação

A arquitetura geral do sistema é mostrada de forma simplificada na fig.III-1.0 processador constituído pela Unidade Aritmética, Unidade de Controle e Sistema de Entrada e Saída, se comunica com os periféricos e com o Sistema de Memória através de barras de comunicação que operam independentemente. O Sistema de Memória pode ainda ser acessado por periféricos ligados a Barra de Periféricos através de um Sistema de Relocação de Endereços, dispositivo que transforma os endereços de 18 bits gerados pelos periféricos em endereços de memória que são de 22 bits. Finalmente temos os Controladores de E/S, que comandam periféricos de alta velocidade (discos e fitas magnéticas de grande capacidade) em operações de acesso direto a memória.

### 2.2- Modos de Operação

O processador possui três modos de operação: Kernel, Supervisor e Usuário, sendo o modo Kernel o mais privilegiado. Neste modo, um programa tem controle completo da máquina, podendo ser executada qualquer instrução. Quando a máquina está operando em um dos outros modos, certas instruções não são executadas, podendo também ser negado acesso direto a periféricos do sistema. O Sistema Operacional executa em modo Kernel as rotinas de tratamento de erro, rotinas de entrada e saída, gerência de memória, etc. No modo Supervisor são executados programas que tratam arquivos do sistema e os compiladores, editores, montadores. A indicação do modo corrente de operação do processador é dada por dois bits da Palavra de Estado do Processador, que possui ainda outros dois bits indicadores do modo anterior do processador.

### 2.3- Registros Referenciáveis por Instrução

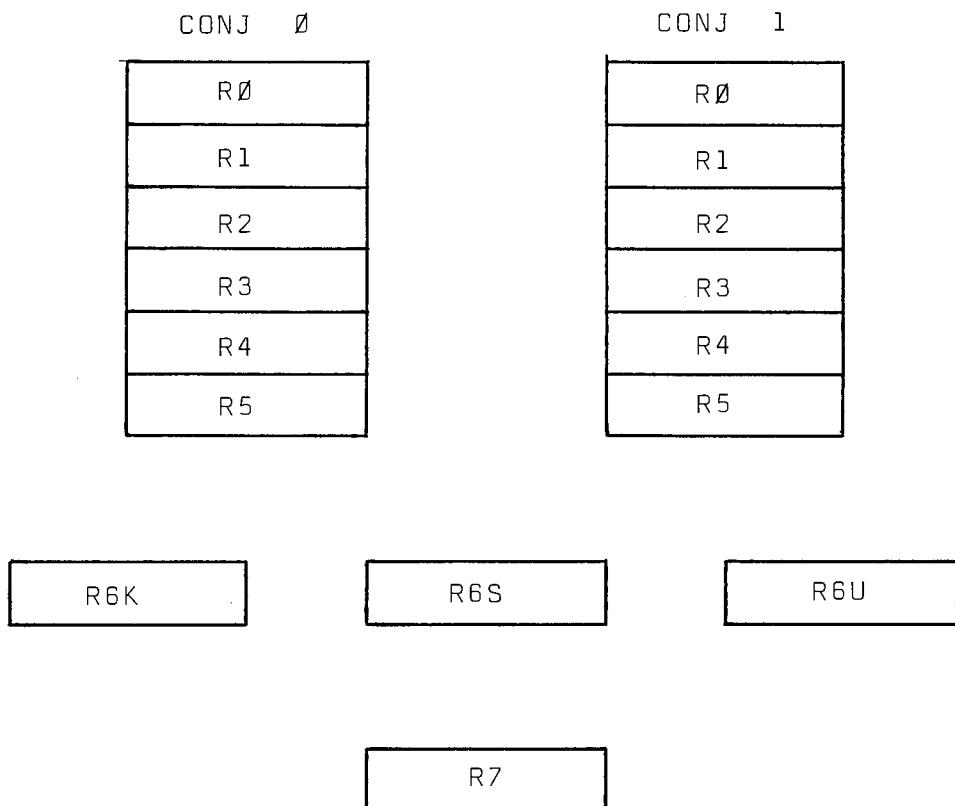

No conjunto de registros referenciáveis por ins

trução temos os chamados registros gerais, mostrados na figura III-2, que são 16 ao todo: R0 a R5 (conjuntos  $\emptyset$  e 1), R6 (Kernel, Supervisor e Usuário) e o R7. Estes registros podem ser usados como acumuladores, apontadores indexadores e apontadores incrementados ou decrementados automaticamente a cada acesso à memória.

Figura III-2 - Registros Gerais

A existência de dois conjuntos de registros gerais R0 a R5, tem por objetivo tornar mais rápido o procedimento de tratamento de interrupções pela UCP. Normalmente um dado programa utiliza-se de um dos conjuntos de registros gerais, sendo o outro utilizado pelas rotinas de tratamento de interrupção. Desse modo a troca de rotinas durante as interrupções é mais rápida, já que não é necessário salvar o conteúdo dos registros gerais. A definição de qual dos conjuntos está sendo utilizado pelo programa em execução, é feita por um bit da Palavra de Estado do Processador (PEP).

Embora qualquer dos registros gerais possa ser usado como apontador de pilha ("stack pointer") sob controle do programa, algumas instruções, associadas com tratamento de inter-

rupções, usam automaticamente o registro R6 como apontador. Há um registro R6 para cada modo de operação do processador.

O registro R7 é usado pelo processador como Contador de Programa. Cada vez que uma instrução ou índice é lido da memória, o conteúdo de R7 é automaticamente incrementado, passando a apontar a próxima palavras da memória.

Além dos registros gerais existem seis acumuladores de ponto flutuante com 64 bits, AC0 a AC5, referenciáveis por instrução. Nas instruções de ponto flutuante um dos operandos encontra-se em um desses acumuladores e outro geralmente na memória.

#### 2.4 - Modos de Endereçamento

Os dados armazenados na memória são acessados e operados por instruções da máquina que geralmente especificam:

- a) A função a ser executada através do código de operação.

- b) Um registro geral para ser usado na busca do operando fonte e/ou um registro geral para busca do operando destino.

- c) Um modo de endereçamento para ser usado na busca do operando fonte e/ou um modo de endereçamento para busca do operando destino.

Os acessos aos operandos na memória podem ser feitos por byte(8 bits) ou palavra que na UCP tem 16 bits. A palavra de memória consiste de um byte alto e um byte baixo. Os bytes baixos são armazenados nos endereços pares da memória e os altos nos endereços ímpares. Palavras começam sempre em endereços pares. Quando são feitos acessos em palavras consecutivas de memória o registro apontador é sempre incrementado por dois.

Os operandos são lidos da memória com auxílio dos registros gerais de forma direta ou indireta, utilizando um dos oito modos de endereçamento seguintes:

##### Endereçamento Direto

- a) Modo 0 (Registro) - Neste modo qualquer dos registros gerais pode ser usado como simples acumulador e o ope

rando está contido no próprio registro. Como são registros internos ao processador as operações são feitas com maior rapidez.

- b) Modo 2 (Auto-incrementado) - Este modo é usado para acessos sequenciais em tabelas de operandos. O conteúdo do registro selecionado é usado para apontar o operando e ao terminar a busca é incrementado por um para instruções que operam com "byte", por dois para instruções de palavra e sempre por dois quando são usados R6 e R7.

- c) Modo 4 (Auto - decrementado) - Este modo é usado para acessos na direção oposta a do modo 2. O conteúdo do registro especificado, primeiro é decrementado (por um em instruções de byte e por dois em instruções da palavra ou que usem R6 ou R7), e a seguir usado para buscar o operando. Estes dois modos de endereçamento, auto-decrementado e auto-incrementado, facilitam operações no modo pilha.

- d) Modo 6 (Indexado) - O conteúdo do registro geral especificado é somado ao conteúdo da palavra seguinte a instrução (palavra de índice) para apontar o operando. Neste modo o conteúdo do registro geral pode ser usado como base para calcular uma série de endereços, permitindo acessos randômicos em uma tabela.

#### Endereçamento Indireto

- a) Modo 1 (Registro Indireto) - O conteúdo do registro é usado para apontar o operando.

- b) Modo 3 (Auto - incrementado indireto) - Neste modo o contúdo do registro é usado como ponteiro para buscar a palavra na memória que contém o endereço do operando. A seguir o registro é incrementado por dois. Este modo e o seguinte são usados para acessos sequenciais em tabelas constituidas de endereços ao invés de operandos.

- c) Modo 5 (Auto - decrementado indireto) - Neste modo o registro é primeiro decrementado por dois e a seguir usado para buscar a palavra que contém o endereço do operando.

- d) Modo 7 (Indexado Indireto) - O conteúdo do registro geral é somado a palavra seguinte a instrução (índice) e então o resultado é usado para buscar o endereço do operando. Nem o registro nem o índice são alterados.

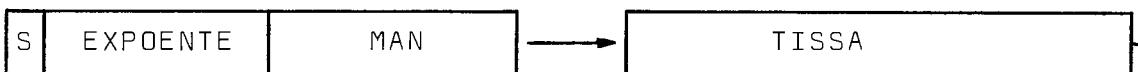

## 2.5- Formato dos Operandos

A Unidade Aritmética opera com dois tipos de números: inteiro e ponto flutuante. Os números inteiros podem ter 16 bits, formato curto, ou 32 bits, formato longo. Exceto nos casos das instruções de multiplicação e divisão, o formato curto é o adotado pelas instruções que operam com números inteiros. Os números são representados em complemento a  $2^n$ . Como uma palavra de memória é composta de 16 bits, um número inteiro ocupa uma ou duas palavras para sua representação, conforme o formato seja curto ou longo respectivamente (fig III-3).

Os números em ponto flutuante tem a forma  $M \cdot 2^E$ , sendo E o expoente e M a mantissa. O expoente é representado em 8 bits podendo assumir valores entre -128 e + 127, entretanto como é sempre armazenado com polarização (soma-se 128 ao valor do expoente), sua representação binária varia entre 0 e 255. Este procedimento, embora compleique a execução das instruções de multiplicação e divisão flutuantes, simplifica no caso das instruções de soma e subtração que são mais frequentes.

A mantissa é representada em sinal e magnitude e conforme a precisão seja simples ou dupla, possui 24 ou 56 bits respectivamente. Como a mantissa é sempre normalizada, ou seja,  $0,5 \leq M < 1$ , o bit imediatamente à direita do ponto é sempre um, exceto quando o expoente é zero, aí o número é considerado zero. Esse bit mais significativo não é armazenado na memória, sendo inserido durante a execução da instrução. Um número em ponto flutuante é armazenado na memória em duas ou quatro palavras de 16 bits como está ilustrado na figura III-3. A primeira palavra pos

sui 1 bit para o sinal, 8 para o expoente e os bits restantes armazenam a parte mais significativa da mantissa. A parte restante da mantissa é armazenada nas palavras que se seguem.

a) Precisão Simples

b) Precisão Dupla

c) Inteiro Formato Longo

d) Inteiro Formato Curto

figura III-3 - Formato dos Operandos

#### 2.6- Conjunto de Instruções

A CPU é capaz de executar 86 instruções de diversos tipos. Para facilitar a microprogramação, estas instruções foram divididas em grupos segundo o número e tipo de operandos e a maneira de execução. Os dois grupos básicos são as instruções que operam dados inteiros e as instruções de operandos em ponto flutuante. Com a finalidade de dar uma idéia do conjunto de instruções inteiras e facilitar o entendimento da estrutura dos microprogramas, que será apresentada mais adiante, é mostrada a seguir a classificação adotada e exemplos de algumas instruções. Uma descrição das instruções de ponto flutuante e de seus microprogramas, pode ser encontrada no trabalho de Mário Ferreira Martins<sup>7</sup>.

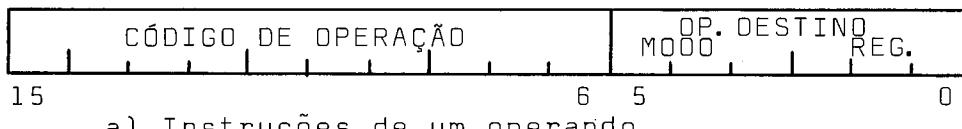

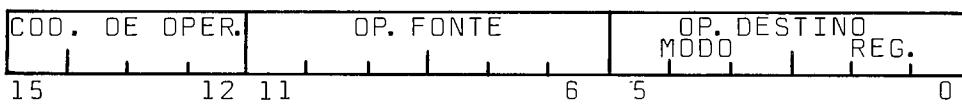

### 2.6.1- Instruções de Um Operando

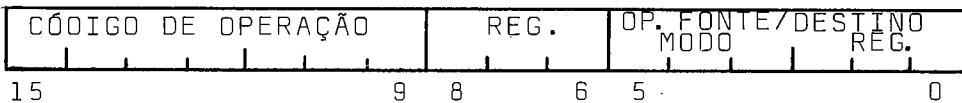

Os bits 15 a 6 especificam o código de operação da instrução e os bits 5 a 0 formam um campo de 6 bits, chamado campo de endereçamento destino (fig. III-4a). Ele consiste de duas partes:

- Os bits 2 a 0 especificam um dos oito registros de uso geral para ser usado no cálculo do endereço do operando.

- Os bits 5 a 3 indicam como o registro selecionado será usado para o cálculo do endereço (modo de endereçamento).

a) Instruções de um operando

b) Instruções de dois operandos

c) Instruções de registro e op. fonte ou destino

d) Instruções de desvio

e) Instruções de posicionamento de código de condição

f) Instruções de execução imediata

fig.III-4 - Formato das instruções inteiras

As instruções de um operando foram divididas, para efeito da microprogramação de sua fase de execução, nos seguintes grupos:

a) Instruções Gerais - São as instruções aritméticas ou de teste do tipo:

CLR - Zera o operando especificado no campo destino.

DEC - Decrementa o operando destino.

TST - Posiciona os códigos de condição segundo o valor do operando destino.

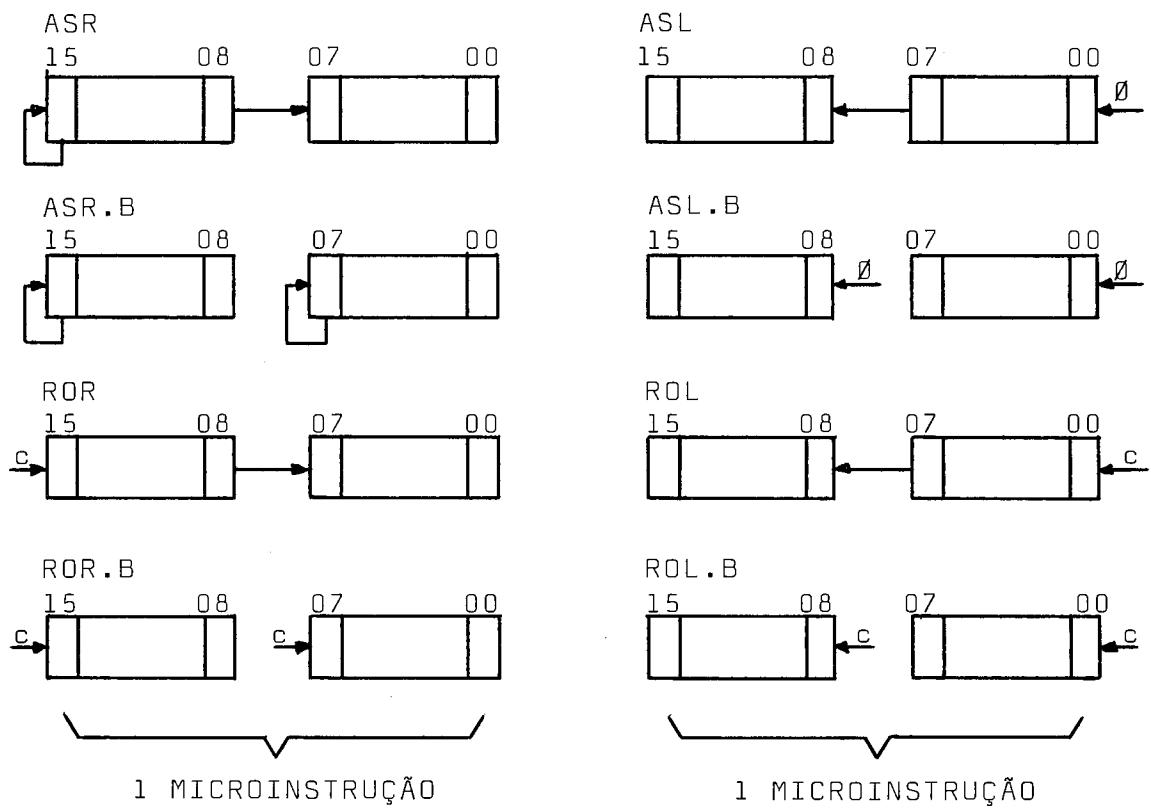

b) Instruções de Deslocamento - Realizam operações de deslocamento aritmético (uma posição ou n posições), ou deslocamentos simples uma posição.

ASR - Desloca o operando destino aritmeticamente uma posição à direita.

ASC - Desloca o operando destino à direita ou à esquerda n posições.

#### 2.6.2- Instruções de Dois Operandos

Operações que implicam no uso de mais de um operando são na sua maioria tratadas por este tipo de instruções. (fig. III-4b). O primeiro operando é chamado operando fonte e o segundo operando é chamado operando destino. O resultado da operação é armazenado na localização apontada pelo campo destino. São instruções que realizam operações aritméticas, lógicas, movimentação e testes, como por exemplo:

MOV - Move o operando fonte para a posição apontada pelo campo destino.

ADD - Soma os operandos fonte e destino e guarda o resultado na posição apontada pelo campo destino.

As instruções de Multiplicação (MUL). Divisão (DIV) e ou-exclusivo (XOR), também são de dois operandos, sendo que um dos operandos está sempre em um dos registros gerais (Fig. III-4.c).

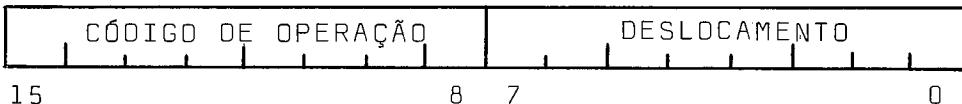

### 2.6.3- Instruções de Desvio

Estas instruções (fig.III-4d) causam um desvio para uma localização definida pela soma do valor de um deslocamento dado pela instrução multiplicado por 2 mais o conteúdo atual do Contador de Programa. O desvio é feito quando a instrução é incondicional ou é condicional e a condição para o desvio é satisfeita. Os testes para o desvio são realizados sobre o estado dos códigos de condição (Vai um, Transbordo, Número Negativo e Resultado Zero) em instruções do tipo:

BR - Desvio incondicional.

BEQ - Desvia se o bit Z (Zero) é igual a um.

BMI - Desvia se o bit N (Negativo) é igual a um.

### 2.6.4- Instruções de Execução Imediata

Estas instruções (fig. III-4 e,f) na verdade não formam um grupo em que a fase de execução possui um microprograma comum. Ao contrário, tem cada uma microprogramas independentes, devido ao caráter específico de sua função. São exemplos de instruções deste tipo, as seguintes:

HALT - Para o processador.

WAIT - Dá ao programador uma maneira de liberar a barra de periféricos, enquanto espera uma interrupção.

RESET - Zera todos os registros de comando para periféricos.

## 2.7- Unidade de Entrada e Saída

### 2.7.1- Introdução

A função básica da Unidade de Entrada e Saída é realizar a comunicação do processador com os periféricos, sistema de memória e registros internos da UCP. Do ponto de vista do programador, tanto os registros internos da UCP como os registros existentes nos periféricos constituem posições de memória, isto

é, o programador não dispõe de instruções especiais para acessar estes registros, utilizando-se para isso, de instruções idênticas aquelas usadas para acessar à memória.

A comunicação do processador com os registros internos é feita através de vias existentes no interior da própria UCP. Já as operações de E/S referentes a registros de periféricos e posições de memória são realizadas através de duas barras de comunicação externas à UCP.

Uma operação de E/S é iniciada sempre através de uma requisição feita pela Unidade de Controle, que coloca à dis posição da Unidade de E/S um endereço em 16 bits, chamado ENDEREÇO VIRTUAL e informações que especificam o tipo de E/S que se de seja fazer (escrita, escrita de byte, leitura de operando, leitura de instrução, etc.). A partir deste instante a operação de E/S é conduzida exclusivamente pela Unidade de E/S, que a executa em quatro etapas.

- a) Relocação do endereço virtual de 16 bits gerado pelo processador, para obtenção do endereço real em 18 bits para comunicação com registros de periféricos, ou em 22 bits para comunicação com registros internos ou com o sistema de memória.

- b) Decodificação do endereço real gerado, o que permite à Unidade de E/S determinar se a operação iniciada se refere a uma posição de memória, a um registro de periférico ou a um registro interno da UCP.

- c) Deteção de erros no processo de formação do endereço real.

- d) Realização da operação de leitura ou escrita requisitada.

#### 2.7.2- Sistema de Relocação de Endereços do Processador

Um programa qualquer na memória se encontra dividido em páginas e a cada página está associado um endereço base de relocação. Cada página pode possuir no máximo 128 blocos de

64 bytes e seu endereço inicial na memória pode ser qualquer múltiplo de 64. A cada programa estão associadas oito páginas no espaço de Instruções e oito páginas no espaço de Dados, totalizando 64 kbytes de endereçamento por programa na memória. Para cada modo de operação do processador (Kernel, Supervisor ou Usuário), existem duas tabelas de relocação: uma para o espaço de Instrução outra para o espaço de Dado. Cada tabela é constituída por 8 pares de registros, cada par corresponde a uma determinada página. Este par é constituído por um registro que define o endereço inicial da página e outro que descreve a página, definindo o seu tamanho e os tipos de acessos permitidos. É através deste registro que se consegue fazer proteção de páginas na memória, definindo-as como não residentes ou de leitura exclusiva.

#### 2.7.3- Espaço de Endereçamento

O espaço de endereçamento colocado à disposição do processador compreende 4 M bytes. Os 8 K bytes de endereço mais alto referem-se a registros de periféricos ou registros internos da UCP. Os 264 k bytes seguintes são utilizados tanto pelos periféricos como pelo processador para acessar a memória através do Sistema de Relocação de Endereço da Barra de Periféricos. Os endereços restantes referem-se a posições físicas de memória e são usadas pelo processador para acessar diretamente o Sistema de Memória.

#### 2.7.4- Detecção de Erros

Os erros detetados pelo Sistema de E/S, em função de sua natureza, podem provocar ou não a suspensão imediata da execução da instrução em curso. No primeiro caso, os erros serão causadores de sinalização de ABORTO e no segundo caso sinalização de "TRAP". Ao ser gerada uma sinalização de ABORTO, a execução da instrução é suspensa e inicia-se a execução de uma rotina para tratamento do erro. Quando há sinalização de "TRAP", a instrução é terminada e aí então inicia-se uma rotina de tratamento da ocorrência. Os erros que causam sinalização de aborto

podem ser de três tipos: erros de endereçamento, erros no uso da pilha do processador no modo Kernel e erros de paridade. A sinalização de "TRAP" acontece quando há erro de paridade na palavra seguinte a posição requisitada, ameaça de violação da pilha, falha no sistema de alimentação e erros em operações de ponto flu tuante. Também são geradas sinalizações de "TRAP", para permitir ao Sistema Operacional efetuar controle estatístico da frequênc ia e tipos de acessos às páginas residentes na memória, para permitir execução de programas instrução a instrução, facilitan do depurações ou para permitir operações de painel.

#### 2.7.5- Interrupções

O sistema possui quatro níveis de interrupção por circuito para realização de operações de E/S com periféricos e sete níveis de interrupção por programa. Uma interrupção é atendida ao final da execução uma instrução, caso não haja ocorrido "TRAP" e caso seu nível de prioridade seja mais alto que o nível de prioridade do processador, definido pela Palavra de Estado do Processador. O nível de prioridade do processador pode variar de 0 a 7. As interrupções por circuito podem estar relacionadas aos níveis 4,5,6 ou 7 de prioridade e as interrupções por programas podem possuir níveis de prioridade de 1 a 7.

Uma descrição detalhada da Unidade de Entrada e Saída, pode ser encontrada no trabalho de tese de Júlio Salek Aude<sup>8</sup>.

#### 2.8- Sistema de Memória

O Sistema de Memória em projeto para esta UCP é do tipo "CACHE-BACKING", visando solucionar o problema de uma memória de alta capacidade e alta velocidade. A capacidade do Sistema de Memória é a capacidade da memória "backing", enquanto que a velocidade do sistema se aproxima da velocidade do "cache", que é muito mais rápido que o "backing".

O "backing" utiliza circuitos de memórias dinâmicas da família MOS, sendo o tempo de ciclo da memória em torno

de 500 ns. A capacidade do "backing" pode ser extendida até 4 M bytes.

O "cache" é composto de pastilhas de memória estática da família TTL Schottky. Sua capacidade de armazenamento total é de 8 K bytes e o tempo de acesso se situa em torno de 80 ns. O "cache" é opcional podendo ser desconectado, permanecendo apenas o "backing" como elemento armazenador.

As operações de leitura ou escrita no "cache" só podem ser realizadas pela UCP ou através do Sistema de Relocação de Endereços da Barra de Periféricos (SRBP). As operações de leitura sempre se referem a uma palavra e as de escrita podem ser relativas a palavra ou byte. A escrita no "cache" é feita em dupla palavra quando se transfere o conteúdo de um bloco do "backing" para o "cache". Esta operação é provocada por uma operação de leitura com falha, ou seja quando há requisição de leitura de uma posição de memória que não está no "cache".

No "backing" os ciclos de leitura são sempre realizados em dupla palavra, ou seja o backing libera duas palavras. Estas duas palavras são carregadas no "cache" e caso a requisição tenha partido da UCP ou do Sistema de Relocação de Endereços da Barra de Periféricos somente a palavra requisitada é enviada. Se o pedido veio do controlador de E/S as duas palavras são enviadas.

As operações de escrita podem ser feitas em bytes ou palavras quando requisitadas pela UCP ou pelo SRBP, e em dupla palavra quando requisitadas pelos controladores de E/S.

O circuito de controle do Sistema de Memória além de comandar as operações de leitura ou escrita e os "interfaces" com os três dispositivos que requisitam ciclos de memória, tem ainda as seguintes funções:

- a) Estabelecimento de uma escala de prioridades para os atendimentos de pedidos de ciclos.

- b) Lógica de determinação da ocorrência de falha ou acerto.

- c) Lógica de inicialização do "cache".

- d) Detecção e indicação de erros e ocorrências internas

no sistema de memória.

A indicação de erros é feita por meio do acionamento de bits em um conjunto de 6 registros do sistema de memória, que servem de meio de comunicação entre este e o resto da máquina.

Maiores detalhes do Sistema de Memória são apresentados no trabalho de tese de Ageu Cavalcanti Pacheco Junior<sup>9</sup>.

#### IV - ORGANIZAÇÃO DA UNIDADE ARITMÉTICA

##### 1- Introdução

O processador visto da Unidade de Controle é composto de uma série de registros, memórias, caminhos de dados (baras de comunicação), deslocadores e unidades que realizam operações lógicas e aritméticas. A alocação e definição de como serão usados estes recursos de modo a executar a função especificada pela instrução, é o problema do microprogramador ao implementar um determinado conjunto de instruções.

Fazendo-se uma analogia com a programação, o trabalho do microprogramador corresponde a escrever uma rotina, na qual uma função lógica ou aritmética é descrita passo a passo, através de funções elementares (microordens). Na programação, através das instruções, a rotina informa ao processador o que fazer, enquanto que a microprogramação, através das microinstruções, diz como deve ser feito, controlando os recursos da máquina. A microprogramação é análoga a programação convencional, os conceitos de subrotinas, desvios condicionais e incondicionais e laços ("loops"), tem as mesmas conotações em ambos os casos. Entretanto, em microprogramação, aparecem problemas adicionais àquele que pretende preparar microprogramas eficientes.

O microprogramador deve ter conhecimento de todos os recursos que estão a sua disposição, cada registro, caminho de dado, memórias locais e as funções que os deslocadores e unidades lógicas e aritméticas executam. Deve conhecer o grau de paralelismo existente no sistema e obter o máximo rendimento desta facilidade. Se preocupar com o sincronismo entre as diversas tarefas, conhecendo os pulsos gerados pelo relógio central e os circuitos afetados por estes pulsos. É importante também saber a relação entre os tempos de acesso a memória principal e o ciclo de execução das microinstruções, procurando tirar proveito da maior velocidade de execução das microinstruções. Portanto o microprogramador deve ter razoável conhecimento tanto de detalhes do circuito e recursos da máquina, bem como da sua filosofia de implementação. Frequentemente, quando os microprogramas são desenvolvidos em paralelo com o projeto dos circuitos, alterações na organização interna visando maior eficiência são sugeridas pe-

los microprogramadores.

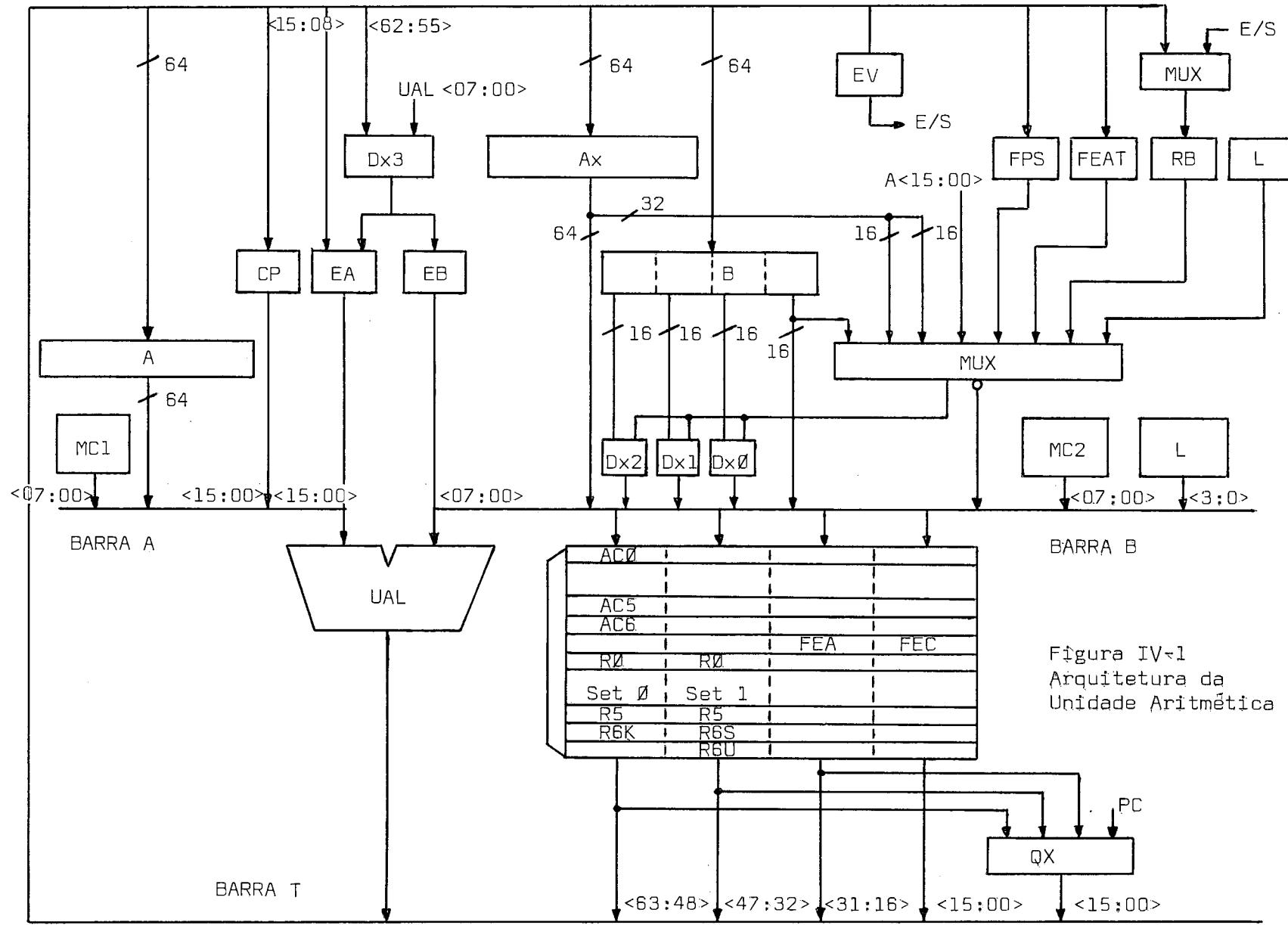

Este capítulo tem a finalidade de apresentar os recursos da Unidade Aritmética (UA) que estão disponíveis ao microprogramador. A organização interna da UA é mostrada na fig. IV-1.

## 2- Unidade Aritmética e Lógica

O principal recurso da UA é a Unidade Aritmética e Lógica (UAL). Capaz de operar dados em 8,16 e 64 bits, a UAL realiza operações de adição, subtração, transferência de dados, complementação e operações lógicas do tipo E, OU, OU-EXCLUSIVO, etc. Sob controle do microprograma, é possível nas instruções interas que operam com byte alto do operando, usar somente a parte da UAL que vai dos bits 8 à 15. Isto é conseguido controlando o vai uma que sai do bit sete.

A UAL exige 6 linhas de controle: quatro ( $S_3, S_2, S_1$  e  $S_0$ ) escolhem a função que será executada, uma define se a UAL usará o modo de operação lógico ou aritmético e a última posiciona o vai um. O controle da UAL pode vir de duas fontes: o campo do microprograma CTL UAL que especifica diretamente a operação a ser realizada, ou uma memória de leitura exclusiva (MLE). Esta memória tem por função tornar o controle da UAL dependente do código de operação da instrução. Para isso ela recebe como endereço alguns bits do Registro de Instruções e fornece na saída sinais que são utilizados para comandar a UAL. Desta maneira foi possível reunir em uma mesma microinstrução a fase de execução de diversas instruções. Nesta microinstrução os registros que contém os operando são liberados nas barras A e B e a UAL é controlada pelos sinais que vêm da memória.

## 3- Memória Rascunho

A Memória Rascunho (MR) possui 16 palavras de 64 bits, sendo dividida em 4 módulos de largura 16 bits (fig.IV-1). A divisão em módulos permite utilizar esta memória tanto para armazenar acumuladores flutuantes de 64 bits como os registros ge

Figura IV-1

Arquitetura da

Unidade Aritmética

rais de 16 bits.

As seis primeiras palavras da MR são utilizadas como acumuladores de ponto flutuante (AC0 a AC5). A sétima palavra é usada como acumulador temporário de 64 bits. Neste acumulador o microprograma carrega da esquerda para direita, cada uma das quatro palavras de 16 bits que compõem o dado de ponto flutuante, quando este é lido da memória. Na oitava palavra são guardados os conteúdos dos registros FEC e FEA, usados durante tratamento de excessões de ponto flutuante. O registro FEC armazena o código da excessão e FEA o endereço da instrução onde ocorreu a excessão.

Na outra metade da memória estão os dois conjuntos de registros gerais e os três apontadores de pilha. O Contador de Programa não é armazenado nesta memória para permitir maior flexibilidade em operações com o seu conteúdo. Da esquerda para direita (figura IV-1), temos no primeiro módulo da memória o conjunto 0 de registros (R0 a R5) e o apontador de pilha (R6) do modo Kernel. No segundo módulo estão o conjunto 1 (R0 a R5) mais os registros R6 dos modos Supervisor e Usuário.

A escrita dos operandos nos acumuladores flutuantes é feita através da barra B <63:00>, enquanto que a leitura de operandos é feita através da barra T <63:00>. Em operações de leitura ou escrita nos registros gerais e execução das instruções de ponto flutuante do tipo "LOAD" e "STORE", que fazem movimentação de operandos entre os acumuladores e memória, os dados passam através de multiplexadores antes de serem lidos ou escritos na MR. Estes multiplexadores (DX2,DX1,DX0,QX, figura - IV-1) permitem que os operandos que estão alinhados na parte baixa das barras (bits <15:00>) possam ser escritos em qualquer dos módulos da MR que estão nas partes altas das barras.

O endereço da MR é composto de 4 bits. O mais significativo que permite escolher entre a metade superior, onde estão os acumuladores flutuantes, e a metade inferior, onde estão os registros gerais, provém diretamente da palavra de controle. Os três seguintes são obtidos através de um multiplexador que, sob controle do microprograma, seleciona uma das quatro fontes abaixo:

- a) Bits <02:00> do Registro de Instruções (RI) - São usados para apontar um dos registros gerais. Em instruções inteiras o registro geral lido é usado para cálculo.

cúlo do endereço do operando destino, e nas instruções flutuantes no cálculo do endereço do operando fonte ou destino.

- b) Bits <08:06> do RI - São usados nas instruções inteiras para apontar o registro geral que será usado no cálculo do endereço do operando fonte. Em instruções de ponto flutuante o bit 8 é forçado para zero, e os três bits apontam um dos acumuladores flutuantes.

- c) Registro de Instruções <08:07> # 1 (instruções inteiras) ou 0 # RI<07> # 1 (instruções de ponto flutuante) - Esta entrada do multiplexador é usada para apontar o registro fonte V 1, ou acumulador flutuante V 1 (V=função lógica ou) nas instruções que utilizam dois registros, um par outro ímpar, para armazenar os operandos. (Obs.: # símbolo usado para significar concatenação).

- d) 1 # END MR <1:0> (Instruções inteiras) ou 0 # END MR <1:0> (Instruções flutuantes) - Entrada do multiplexador usada pelo microprograma para apontar regis gerais ou acumuladores flutuantes em operações de leitura ou escrita. END MR <1:0> é o campo do microprograma usado nestas operações.

#### 4- Registros EA e EB

Os registros EA e EB são usados nas instruções de ponto flutuante para armazenar os expoentes dos operandos e nas instruções inteiras armazenam informações sobre os endereços dos operandos.

O registro EB tem oito bits e é do tipo contador. EA tem 16 bits, mas só os 12 bits menos significativos, usados durante as instruções de ponto flutuante, são do tipo contador. Normalmente, durante a execução destas instruções os expoentes são armazenados nos oito bits menos significativos dos registros. Os bits adicionais do registro EA são usados para detetar

transbordo ou "underflow" do expoente durante as operações de normalização de resultados ou correção de transbordo de mantissa.

Nas instruções inteiras o registro EA é utilizado no cálculo do endereço do operando fonte, permanecendo com o endereço durante toda a fase de execução da instrução. No registro EB é armazenado o bit menos significativo do endereço do operando destino. Com as informações sobre os endereços dos operandos inteiros armazenadas em EA e EB, mais a indicação de que a instrução é de palavra ou não, é possível determinar em qual dos bytes menos significativos da UAL, será realizada a operação requerida pela instrução.

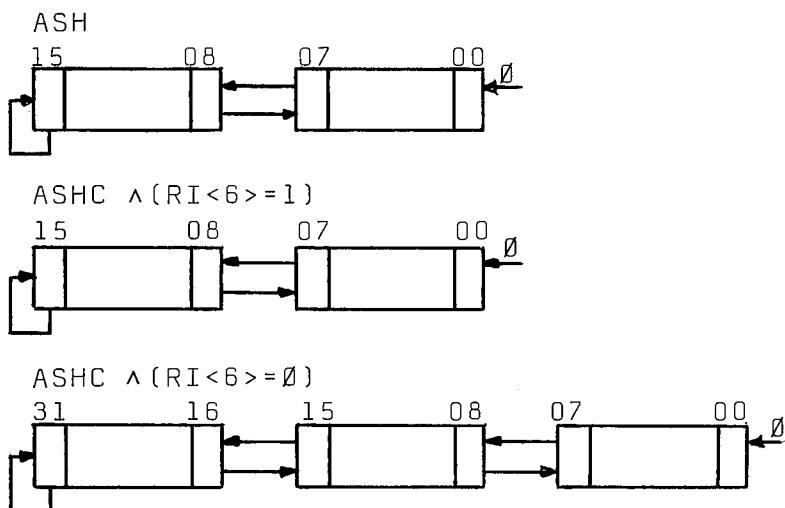

Durante a execução das instruções de ASHC e ASH, o registro EB é utilizado como contador do número de deslocamentos que o operando no registro AX vai sofrer.

Os registros EA e EB ao contrário dos demais, não recebem os dados diretamente da barra T, mas através de multiplexadores (fig. IV-1), isto porque os oito bits menos significativos nos dois registros podem vir da barra T <62:55> ou barra T <07:00>. No início da execução das instruções de ponto flutuante, o expoente a ser carregado em EB ou EA provém da Memória Rascunho bits 62 a 55, via barra T. Durante a fase de execução das instruções, quando são feitas operações com os registros, os dados vem pela barra T <07:00>.

## 5- Registros A, B e AX

São registros de 64 bits utilizados para armazenar as mantissas dos operandos de ponto flutuante ou como registros de trabalho em instruções inteiras.

Nas instruções inteiras os números são armazenados em complemento a 2 estando alinhados à direita, ou seja, o bit <15> do número coincide com a posição <15> do registro. Nas instruções de ponto flutuante as mantissas começam na posição <59> (bit mais significativo). Se a precisão for simples a mantissa tem 24 bits e estará situada de <59> a <36>, em precisão dupla estará situada de <59> a <04>. Os bits adicionais dos registros são utilizados para detecção de transbordo e operações de Normalização e Arredondamento. Além disso, alguns dos bits adi-

cionais se devem ao número mínimo de bits que compõem as pastilhas utilizadas para implementar os registros.

O registro A pode liberar os 64 bits do seu conteúdo na barra A, ou então, os 15 bits menos significativos na barra B, através do multiplexador 8 para 1 (MUX, figura IV-1). Os bits <15:00> do registro A atravessam o multiplexador, para permitir que os resultados de operações aritméticas e lógicas possam ser escritos na memória rascunho, quando necessário.

O registro AX pode liberar todo o seu conteúdo diretamente na barra B, ou somente os 32 bits menos significativos também na barra B, mas através do multiplexador 8 para 1. Este último modo de liberação na barra decorre da necessidade da instrução inteira de deslocamento aritmético ASHC, que é executada em AX. Nesta instrução o operando pode ter 1 ou 2 palavras ocupando AX <15:00> ou AX <31:16> # AX <15:00>. Em qualquer caso, após os deslocamentos o resultado deve ser carregado de volta nos registros gerais. Como já vimos (ver IV-3) a única maneira destes resultados serem carregados na MR é através do multiplexador 8 para 1 e dos duplexadores DX2 e DX1 (figura IV-1), que permitem atingir qualquer módulo na MR.

O registro B é dividido em quatro módulos de 16 bits, sendo que somente o módulo correspondente aos bits menos significativos é liberado diretamente na barra B. Os outros 3 módulos atingem a barra através dos duplexadores DX2, DX1 e DXØ.

Figura IV-2 - Concatenação dos registros A e B

figura IV-3 - Concatenação do Registro AX

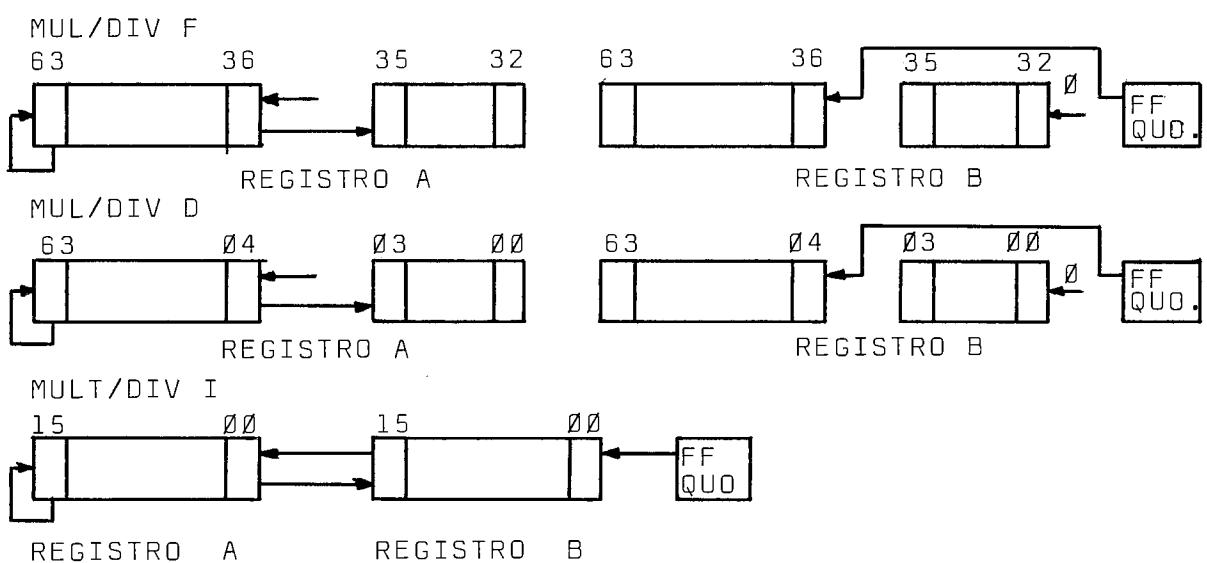

Os registros A e B são concatenados para permitir a execução das instruções de Multiplicação e Divisão. A concatenação é feita em função da instrução e dos diferentes formatos existentes (ponto flutuante simples (F) ou duplo (D) e inteiro (I)), conforme está mostrado na figura (IV-2).

Todos os deslocamentos aritméticos ou simples e as execuções das macros NORMALIZE e EQUALIZE são realizadas no registro AX. As possibilidades de concatenação devido ao grande número de instruções que utilizam o registro AX para fazer deslocamentos são muitas. Por esta razão o microprogramador pode escolher entre dois tipos de controle da concatenação: concatenação normal ou condicionada ao tipo da instrução em execução. A concatenação condicional é totalmente comandada por uma MLE. Esta memória recebe bits do RI, suficientes para identificar a instrução em execução e fornece na saída sinais para comandar duplexadores de concatenação colocados entre os diversos módulos em que o registro está dividido. A figura IV-3 mostra as instruções e os correspondentes modos de concatenação do registro AX. Quando da execução de uma dessas instruções, o microprograma necessita apenas liberar a concatenação condicional e dar a ordem de deslocamento à direita ou esquerda conforme a instrução. Isto permitiu que diversas instruções fossem executadas em uma única microinstrução, conforme está indicado na figura IV-3, economizando palavras da memória de controle.

#### 6- Registros EV(Endereço Virtual) e RB(Régiistro de Barra).

São registros de 16 bits utilizados pela Unidade Aritmética durante comunicação com os registros internos, periféricos ou memória. "RB" serve como um registro "destino", onde são armazenados os dados que chegam a saem da UA. Ele funciona em conjunto com o registro EV, onde é carregado o endereço que será utilizado na operação de E/S. Uma E/S começa quando o chamado endereço virtual de 16 bits gerado pelo processador é carregado em EV. A partir deste instante o endereço sofre um processo de relocação que o transforma no chamado endereço real de 22 bits. Em seguida é feita uma verificação de ocorrência de erros no endereço e a decodificação para determinar o destino do endereço: memória, periféricos ou registros internos. Todas estas operações iniciadas a partir da carga em EV são realizadas pela Unidade de E/S independentemente da Unidade de Controle.

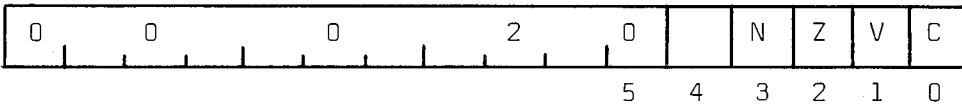

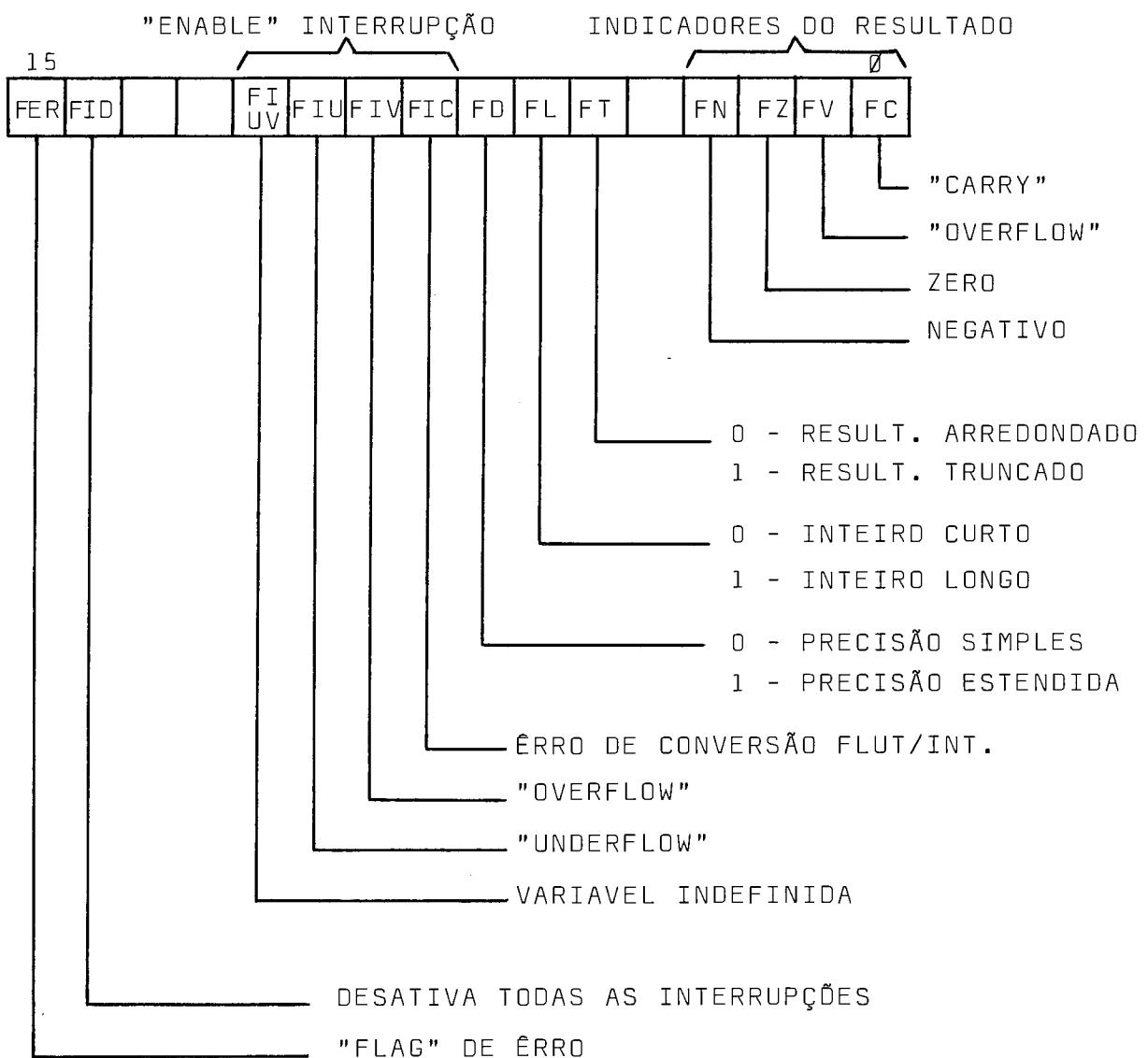

## 7- Registro FPS

Registro de 16 bits que controla o modo de operação da UA em instruções de ponto flutuante, bem como armazena os códigos de condição e dá informações sobre os erros ocorridos durante a execução da instrução anterior. É dividido em campos conforme está mostrado na figura IV-4.

O campo correspondente aos códigos de condição (FPS <03:00>) é posicionado por circuito ao fim de cada instrução, de acordo com o tipo de resultado obtido. O campo seguinte (FPS <07:05>) controla os modos de operação, especificando a precisão dos operandos e se deve haver arredondamento ou truncamento nos resultados. O terceiro e o quarto campo, FPS <11:08> e FPS <14> respectivamente, são usados para permitir ou não interrupção do programa no caso de ocorrência das excessões que estão indicadas na tabela IV-1. O último campo (FPS <15>) é um indicador de que ocorreu alguma excessão durante a execução da instrução, entretanto só é posicionado se os bits que liberam interrupção estão ativados. Caso ocorra erro no código de operação ou tentativa de divisão por zero ele é sempre posicionado.

## 8- Registro FEAT

O registro é utilizado para armazenar o endereço da instrução que está em execução, sendo atualizado cada vez que uma nova instrução inicia sua execução. Os registros FEAT, FEA e FEC possibilitam a recuperação de erros ou excessões ocorridas durante a execução das instruções de ponto flutuante. Quando corre alguma excessão ou erro e os bits que liberam as interrupções estão ativados (FIU, FIUV, FIV e FIC), o código do erro (tabela IV-1) é carregado no registro FEC e o endereço da instrução que está armazenado em FEAT é transferida para FEA. Mais tarde no atendimento da interrupção, a rotina que trata o erro pode então descobrir através de FEC e FEA qual foi o erro e em que instrução ocorreu. Deve-se observar que o programador só tem acesso aos registros FEC e FEA.

Figura IV-4 - FPS: PALAVRA DE "STATUS" DE PONTO FLUTUANTE

| Código | Tipo do erro                        |

|--------|-------------------------------------|

| 0      | não usado                           |

| 2      | código da instrução inválido        |

| 4      | divisão por zero                    |

| 6      | erro de conversão flutuante/inteira |

| 8      | "overflow"                          |

| 10     | "underflow"                         |

| 12     | variável indefinida                 |

Tabela IV-1 - Códigos das exceções flutuantes

## 9- Constantes

Na UA há necessidade de várias constantes, que são utilizadas em diversos instantes durante a execução dos microprogramas. Constantes são usadas por exemplo em:cálculos de endereço dos operandos (operações de auto-incremento e decremento); carga de contadores que controlam o número de deslocamentos em registros (instruções de deslocamento aritmético n posições), obtenção dos endereços onde estão os pontos de entrada das rotinas que tratam dos abortos e "traps", etc. Estas constantes são geradas por 3 fontes distintas na UA: MC1, MC2 que são memórias do tipo MLE (memórias de leitura exclusiva) com 32 posições de 8 bits e L, um circuito de lógica combinacional.

A palavra de microprograma possui 6 bits para escolher a constante a ser usada. Dois bits (campo LIB CNST) escolhem uma das três fontes (00-INATIVO, 01-MC1, 10-L, 11-MC2), e os quatro restantes são utilizados no endereçamento de MC2.

Em MC1 estão armazenados os endereços dos vetores utilizados pelas instruções de "TRAP". Estas instruções (EMT, BPT, IOT, TRAP), servem para realizar chamadas a emuladores, monitores de E/S, interpretadores definidos pelos usuários, etc., e funcionam efetivamente como interrupções por programa. Também em MC1 estão os endereços dos vetores de "TRAP" e abortos ocorridos durante o processamento normal. O endereçamento de MC1 é condicional e feito através de um duplexador que seleciona entre bits do Registro de Instruções (RI) e sinais provenientes da UE/S, quem apontará a constante. Os bits do RI identificam qual das quatro instruções de "trap" está em execução e portanto o vetor correspondente, enquanto que os sinais vindos da UE/S identificam que erro ocorreu, e também o vetor. Como o endereçamento de MC1 é condicional, durante a sua utilização o microprograma apenas faz a sua liberação através do campo LIB CNST e espera o resultado da leitura na barra A <7:0>.

MC2 é dividida em duas partes com 16 palavras de oito bits cada uma. Uma das partes é reservada para armazenar constantes necessárias durante a execução das instruções de ponto flutuante MUL e MOD. A outra contém constantes utilizadas pelas instruções restantes. Dos cinco bits que endereçam esta memória, quatro provém diretamente do microprograma e apontam uma

dentre as 16 constantes armazenadas em cada parte da memória. O quinto vem de uma lógica que especifica se a instrução em execução é MUL ou MOD, sendo o sinal que divide a memória em duas partes. Os bits na saída da memória são liberados na barra B<07:00>.

A lógica L é totalmente condicional, e nela o microprograma só atua liberando o seu resultado na barra B<07:00>. Esta lógica gera as constantes 1, 2, 4 e 8 utilizadas durante os cálculos dos endereços dos operandos tanto de ponto flutuante como inteiros. Para isso ela recebe informações do Registro de Instruções sobre os modos de endereçamento, registros gerais, tipo de instrução em execução, etc.

## 10- Macroinstruções

Mesmo tendo controle microprogramado algumas máquinas incluem também circuitos que realizam tarefas repetitivas (geralmente de natureza aritmética) e que normalmente exigiriam um tempo longo se executadas diretamente por microprograma.

Um exemplo do uso de circuitos extras em substituição a microprogramação e que frequentemente é empregado, ocorre na implementação da multiplicação. A execução desta instrução consiste basicamente, de uma série de testes, somas e deslocamentos. Por meio da microprogramação estas operações seriam realizadas por um laço de microprograma repetido até que todos os dígitos do resultado fossem gerados. Este método tem a desvantagem de ser mais lento que a implementação por circuitos. Isto porque a execução de cada uma das operações básicas na implementação por microprogramação é realizada durante o tempo de execução das macroinstruções, enquanto que por circuito o tempo gasto corresponde a duração efetiva de cada operação, que é menor.

Na UA existem quatro circuitos que são usados para reduzir o tempo de execução de diversas operações: circuitos de Normalização, Equalização, Divisão e Multiplicação. As macroinstruções que utilizam estes circuitos são chamadas macroinstruções, tendo duração variável conforme a tarefa realizada. Existem dois bits do microprograma que escolhem qual dos quatro circuitos será utilizado.

A macro NORMALIZE foi criada primordialmente pa-

ra colocar a mantissa do resultado de uma instrução de SOMA ou SUBTRAÇÃO flutuantes, no intervalo  $0,5 \leq M < 1$ . Esta tarefa é levada a cabo deslocando o conteúdo de um dos registros de mantissa, no caso AX, para a esquerda e decrementando o mesmo número de vezes o conteúdo do registro de expoente (EA). A macroinstrução termina quando o bit 1 mais significativo da mantissa fica alinhado a direita do ponto.

A macro EQUALIZE também foi criada para utilização nas instruções de SOMA e SUBTRAÇÃO flutuantes. Nestas instruções antes de ser realizada a operação, isto é somar as mantissas, é necessário igualar os expoentes. Isto é feito pela macroinstrução, deslocando para direita a mantissa do menor operando (em AX), e decrementando um contador com a diferença entre os expoentes até que ele chegue a zero.

Verificou-se depois que as macros NORMALIZE e EQUALIZE, poderiam, com pequenas alterações, ser também utilizadas em outras instruções, tais como as de conversão de operandos de ponto flutuante em inteiros e de deslocamento aritmético.

As macros MULTIPLIQUE e DIVIDA são usadas tanto nas instruções inteiras quanto de ponto flutuante, embora os operandos nos dois casos tenham diferentes representações.

#### 11- Registro CP (Contador de Programa)

Registro de 16 bits que faz o sequenciamento dos programas, apontando sempre a próxima instrução a ser executada. O CP também pode ser usado como registro geral (Registro 7), respondendo aos modos de endereçamento como os outros registros. Fisicamente está colocado na barra A<15:00> tendo campos do microprograma para carga e liberação como um registro de trabalho. Durante os acessos à Memória Rascunho em que bits do RI apontam um dos registros gerais para uso em cálculo de endereço de operandos, o registro R7 ou CP, comporta-se como se estivesse logicamente dentro da Memória Rascunho, sendo transparente ao microprogramador a sua real posição.

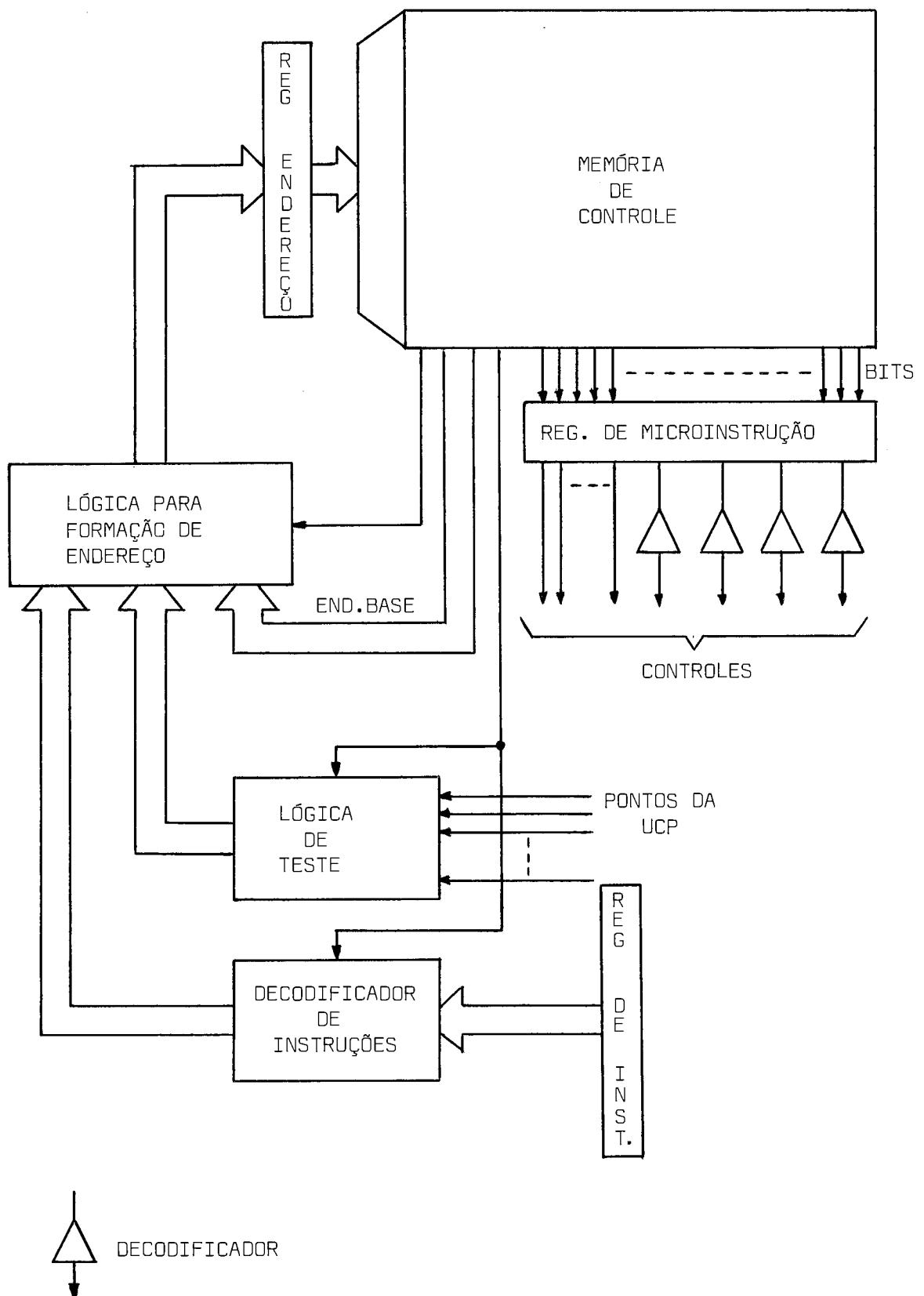

V - ORGANIZAÇÃO DA UNIDADE DE CONTROLE

1-Introdução

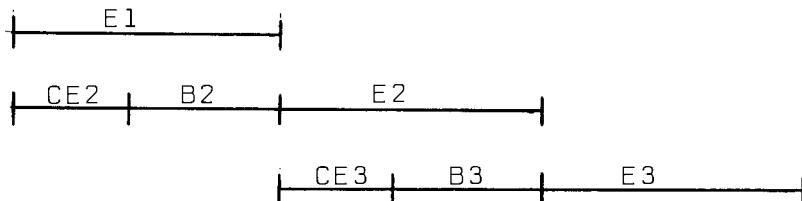

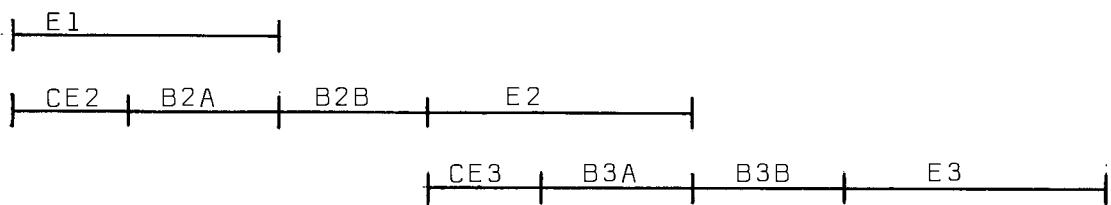

O funcionamento da Unidade de Controle da UCP é muito parecido com o modelo proposto por Wilkes. Na UC a cada ciclo de máquina uma palavra é lida da Memória de Controle e armazenada no Registro de Microinstrução para ser usada durante todo o ciclo. Cada palavra corresponde a uma microinstrução, sendo dividida em campos e cada campo controla pontos específicos da máquina. Campos do micropograma que são usados durante o início da execução da microinstrução e antes que um novo endereço seja carregado no Registro de Endereços da Memória de Controle não são armazenados.

Como base para cálculo do endereço da próxima microinstrução a ser executada é usado um campo do micropograma de 9 bits, chamado de Endereço Base. Este endereço pode ser alterado sob controle do micropograma, permitindo a execução de dois tipos de desvio. Quando é necessário testar o estado de um determinado ponto do processador, por exemplo se o resultado da última operação foi igual a zero, é utilizada uma lógica especial de testes. Se a escolha da próxima micro-rotina depende da instrução que está em execução, o desvio é feito testando-se sinais da saída da lógica que decodifica as instruções. O novo endereço a pós ser montado na lógica de formação de endereços é carregado no Registro de Endereços da Memória de Controle. Esta carga é feita durante a execução da microinstrução, e portanto a busca da próxima palavra é feita em paralelo com a execução da atual.

2- Memória de Controle

Considerável esforço foi feito para diminuir tanto o número de palavras necessárias ao controle como a largura da palavra do micropograma, procurando deste modo reduzir o custo da Memória de Controle. A maioria das tentativas para diminuir a largura da palavra se concentrou em achar a melhor maneira de reunir as diversas microordens isoladas em campos de controle. Cuidado, teve de ser tomado, em não agrupar em um único campo, microordens que poderiam ser usadas na mesma microinstrução, ou em

Fig V-1 - Arquitetura da Unidade de Controle

complicar desnecessariamente a decodificação destes campos, com isso degradando a velocidade da máquina.

Para diminuir o número de bits, também foi usada a técnica de permitir que um campo tivesse dupla função. Por exemplo, a UCP executa na mesma Unidade Aritmética, operações sobre dados em ponto flutuante e inteiros. Como consequência, haveria campos que somente seriam utilizados em operações com um desses dois grupos de dados. Para estes campos foi definida uma dupla função, isto é, controlam pontos diferentes da máquina conforme a instrução seja inteira ou flutuante. Um exemplo é o campo que controla as duas Palavras de Estado do Processador. Há na UCP duas Palavras de Estado, uma para instruções de ponto flutuante e outra para instruções inteiras. O controle destas palavras (carga de novos valores ou alterações em bits) é feito através de um único campo, que atua em uma ou outra conforme o tipo da instrução. Neste caso foi adicionada alguma complexidade na decodificação das microordens, na busca de reduzir o tamanho da palavra.

Na tentativa de diminuir o número de palavras da memória de controle, os microprogramas foram estruturados de maneira a aumentar as micro-rotinas que pudessem ser compartilhadas por várias instruções. Como resultado foi necessário um aumento nos circuitos de desvio, para permitir que ao fim da execução de cada micro-rotina, o microprograma possa determinar, em função da instrução atual, a próxima a ser executada.

Um outro artifício usado para reduzir o número de palavras, foi agrupar em uma única micro-rotina, a fase do microprograma, onde é executada a operação lógica ou aritmética especificada no código de operação de várias instruções. Para realizar estas operações a Unidade Aritmética usa uma lógica combinacional complexa (UAL, Cap.IV-2), capaz de realizar um grande número de funções lógicas e aritméticas (SOMA, SUBTRAÇÃO, OU, E, etc.). Esta lógica é normalmente controlada por um campo do microprograma de seis bits, que especifica qual a função a ser executada durante a microinstrução. Fazendo-se que o controle da UAL pudesse também ser dependente do código de operação da instrução, foi possível agrupar a execução de diversas instruções em uma micro-rotina.

O uso de flip-flops de estado também foi uma téc

nica bastante empregada. Ao microprograma é permitido desviar sobre uma condição interna da máquina, mesmo depois que ela tenha ocorrido, e para isso a condição é armazenada em flip-flops de estado. Deste modo, frequentemente, é possível fazer um desvio diversas microinstruções após a ocorrência da condição, evitando-se duplicação de palavras de controle.

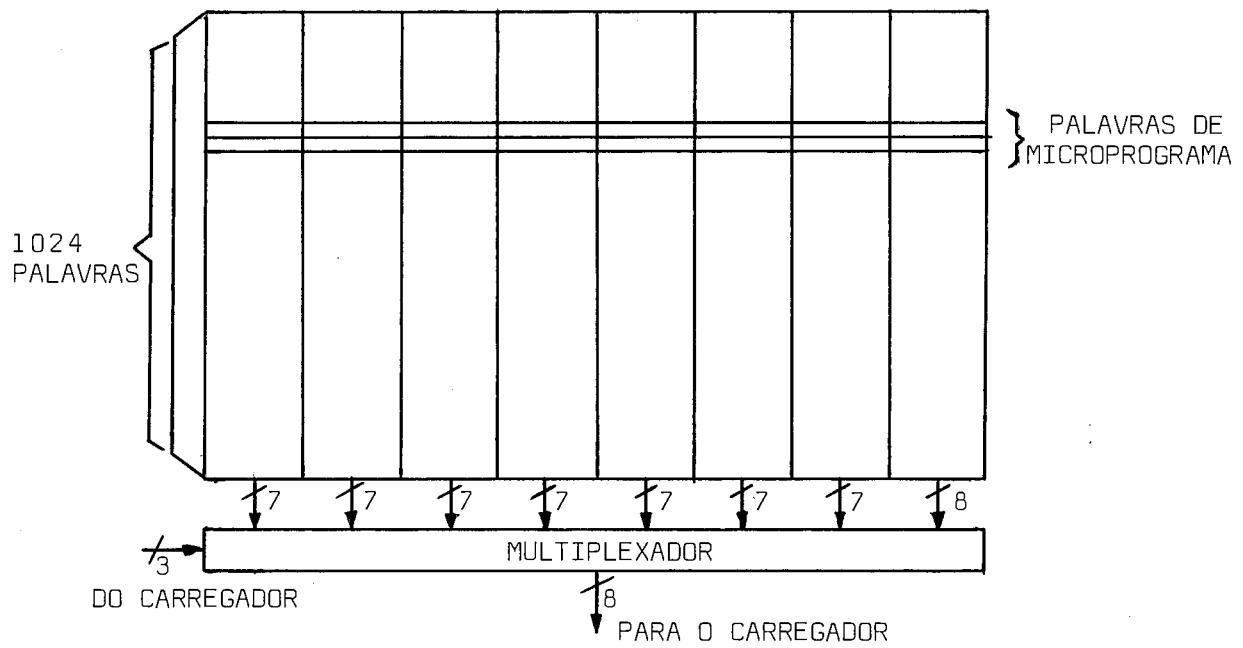

Depois deste trabalho de minimização a memória de controle ficou com 512 palavras e largura igual a 113 bits. Nesta memória são armazenados microprogramas para controlar a Unidade Aritmética e Unidade de Entrada e Saída. A memória será implementada com pastilhas de memória de leitura exclusiva de 512 palavras de 4 bits e tempo de acesso típico igual a 40 ns.

### 3- Palavra de Controle

A palavra de controle é composta de microordens, que podem ser codificadas formando um campo de controle ou não. Para facilitar, os bits isolados da palavra de controle usados como microordens simples, também serão chamados de campos de controle. Com o propósito de aumentar a flexibilidade e consequentemente dar ao programador microinstruções mais poderosas e consistentes com os recursos da máquina, a palavras do microprograma possui campos de controle separados para cada recurso do processador (UAL, Registros, Memória Rascunho, etc.). Isto possibilita que a maioria das operações simultâneas possam ser especificadas, embora nem todas tenham sentido.

Alguns dos campos de controle podem ser logicamente grupados segundo a função que executam dentro do processador. Dentro deste critério podemos criar os seguintes grupos:

- a) Campos de Liberação - Controlam a transferência de dados e endereços entre registros, unidade aritmética e lógica e outras unidades, através de barras de comunicação internas ao processador.

- b) Campos de Seleção - Estes campos fazem o controle dos diversos multiplexadores existentes no processador, selecionando qual registro vai atravessá-lo e ser liberado na barra de comunicação associada ao

multiplexador.

- c) Campos de Controle - Definem uma grande variedade de funções que incluem a operação da UAL,funções de contagem e carga em registros, seleção da macroinstrução que vai ser executada, etc.

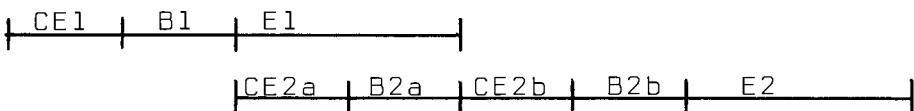

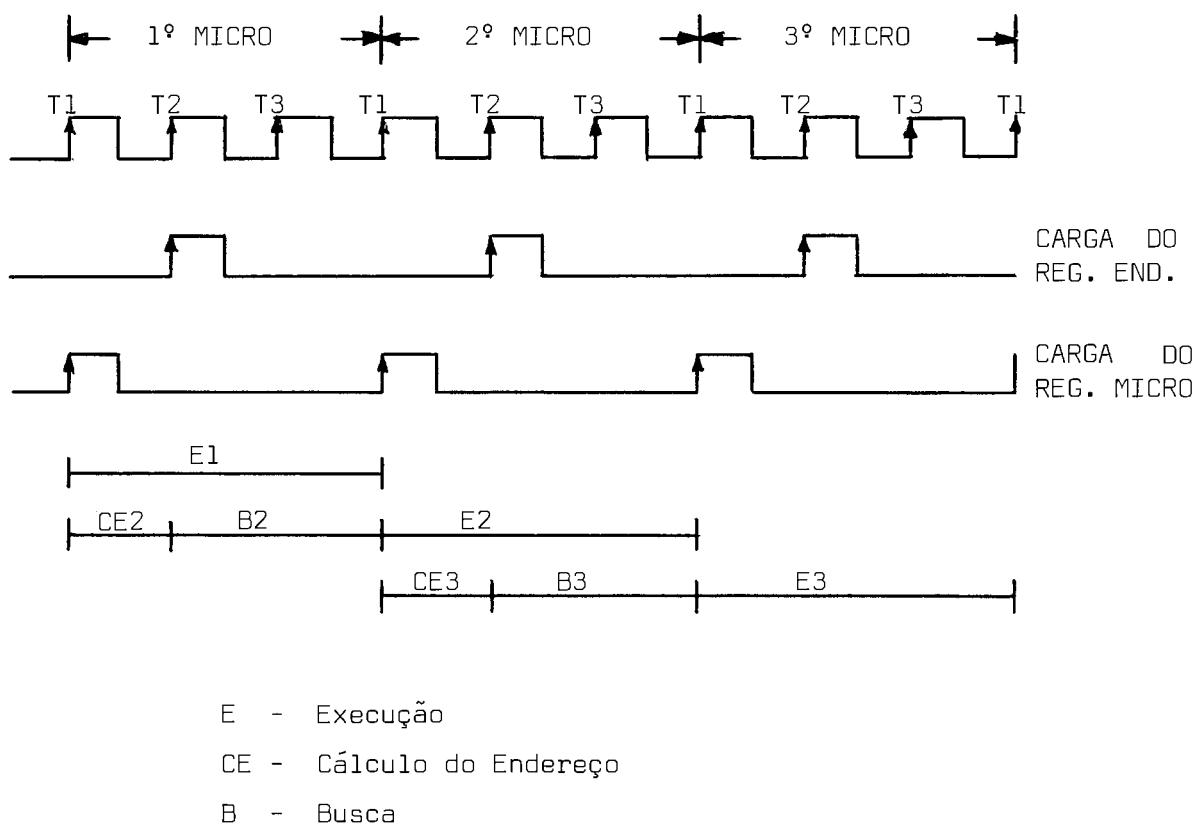

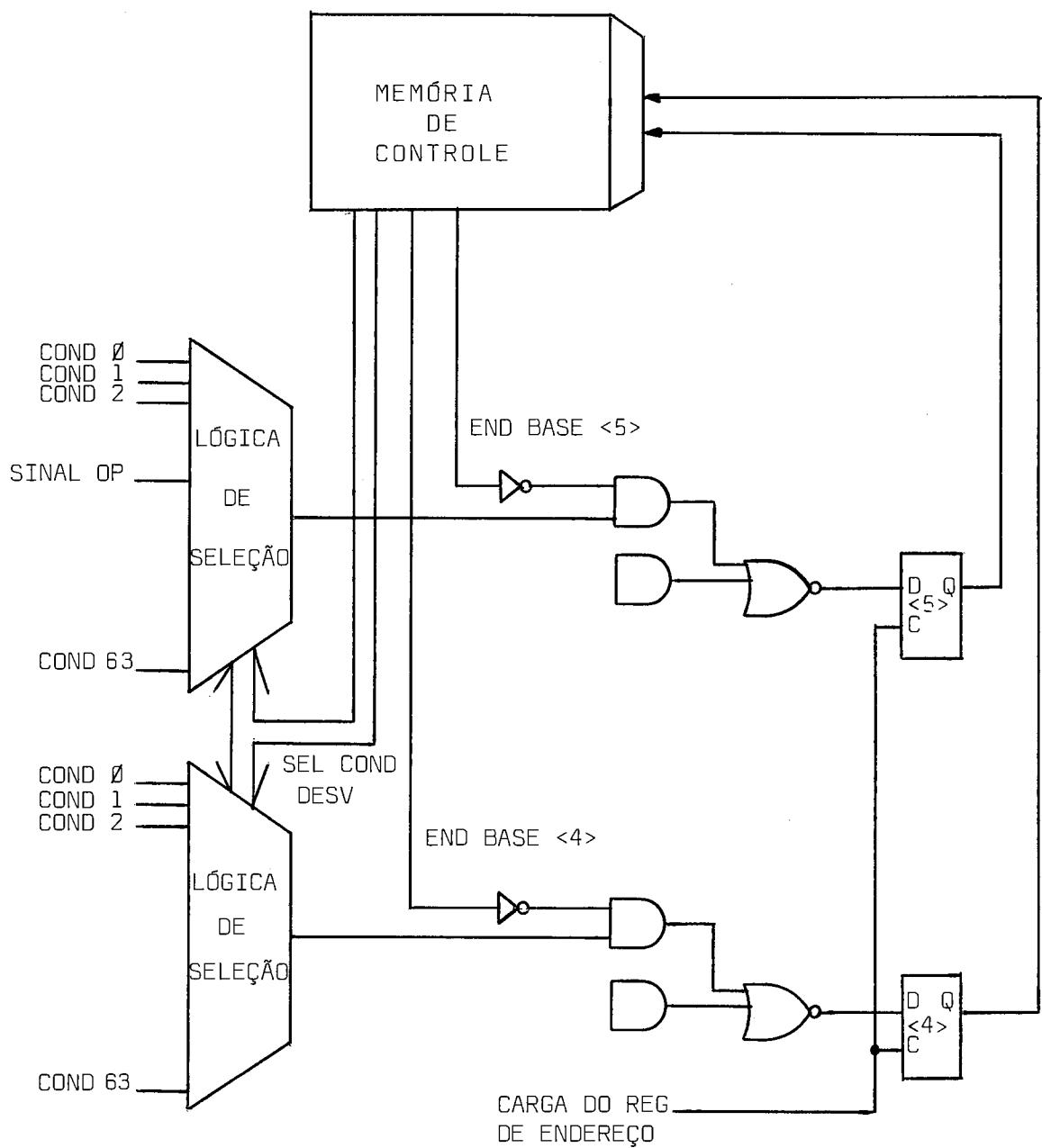

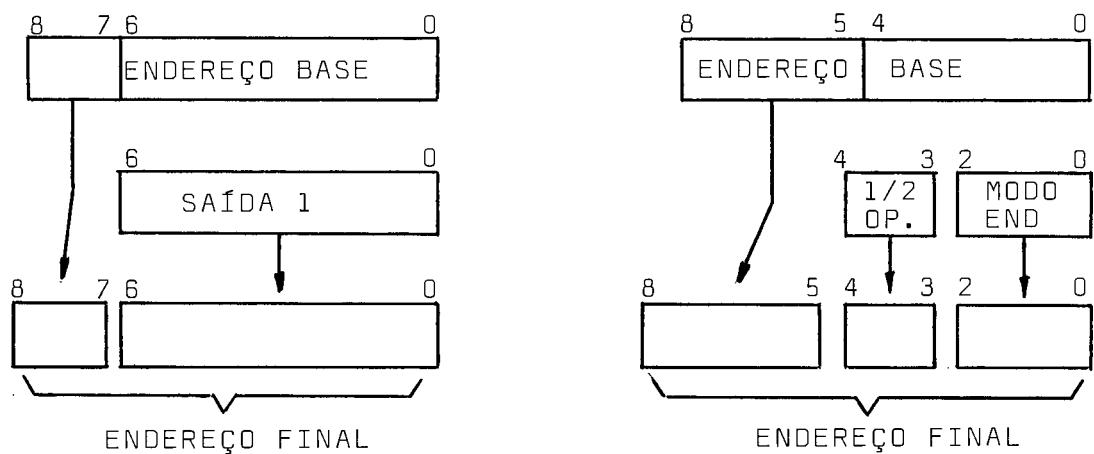

- d) Campos para Comunicação e Sincronismo com a Unidade de Entrada e Saída - No processador as operações de E/S são realizadas em paralelo com a execução dos microprogramas, com o objetivo de diminuir o tempo de execução das instruções. Quando é necessário uma E/S, a Unidade de Controle através destes campos, define o tipo de operação que deve ser feita (escrita ou leitura) e os tipos de operandos envolvidos (dados, endereços ou índices) e continua a execução da microprograma até que seja obrigatório parar. Em operações de leitura o avanço é feito até que a informação requisitada seja necessária ao prosseguimento do microprograma. Em escritas o microprograma avança até uma nova operação de E/S, que só pode ser realizada após uma verificação com a Unidade de Entrada e Saída se ocorreu durante a operação anterior algum tipo de erro. No caso afirmativo o microprograma é desviado para microrotina de tratamento do erro, caso contrário o microprograma é liberado pela Unidade de Entrada e Saída, para continuar seu curso normal.