i

UMA PROPOSTA DE PROCESSAMENTO PARALELO ATRAVÉS

DE UMA ARQUITETURA A MICROPROCESSADORES

José Motta da Rocha Lopes

TESE SUBMETIDA AO CORPO DOCENTE DA COORDENAÇÃO DOS PROGRAMAS DE

PÓS GRADUAÇÃO DE ENGENHARIA DA UNIVERSIDADE FEDERAL DO RIO DE

JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO

DO GRAU DE MESTRE EM CIÊNCIAS (M.Sc.)

Aprovado por:

Sueli Mendes dos Santos

(Presidente)

Leslie Afrânio Terry

Edil Severiano Tavares Fernandes

Michael Anthony Stanton

RIO DE JANEIRO, RJ - BRASIL

NOVEMBRO DE 1982

MOTTA, JOSE

Uma Proposta de Processamento Paralelo Através

de uma Arquitetura a Microprocessadores [Rio de

Janeiro] 1982.

VIII, 145p., 29,7cm (COPPE/UFRJ, M.Sc., Enge-

nharia de Sistemas e Computação, 1982).

Tese - Univ. Fed. Rio de Janeiro, CEPEL

1. Sistema Distribuído Baseado em Microproces-

sadores. I. COPPE/UFRJ II. Título (Série)

AGRADECIMENTOS

A Leslie Afranio Terry pela orientação e por todo o esforço dispendido no desenvolvimento deste trabalho.

A Sueli Mendes dos Santos pela orientação e pelos conhecimentos transmitidos durante os cursos.

A Valmir Carneiro Barbosa pela participação nas discussões que definiram o projeto.

A Cesar Augusto Boavista de Freitas pela revisão do trabalho.

A Rosangela Silva Torres e a Leena Motta da Rocha Lopes pelos trabalhos de datilografia e confecção gráfica da tese.

Ao CEPEL por ter possibilitado o desenvolvimento do presente trabalho através de incentivos e recursos.

SINOPSE

Este trabalho foi motivado pela crescente importância que os projetos de software básico para sistemas distribuídos com microprocessadores tem representado para o desenvolvimento de sistemas de computação mais eficientes.

E proposta a adaptação de um sistema de desenvolvimento de programas, que opera em microcomputadores de pequeno porte, de forma a permitir o processamento científico necessário a um Centro de Controle e Supervisão para Sistemas Elétricos de Potência. Os principais aspectos considerados na máquina estendida são:

- A manutenção da portabilidade existente no sistema original;

- A interligação de microprocessadores por intermédio de uma topologia fortemente conectada;

- A substituição do "stack" linear por uma estrutura mais adequada ao processamento paralelo;

- A introdução de técnicas mais otimizadas de gerenciamento de memória.

Um protótipo para emulação de parte das funções especificadas do processador virtual foi construído a partir do microprocessador 8086. Na implementação das etapas futuras do projeto é prevista a utilização de componentes mais sofisticados.

ABSTRACT

This work was motivated by the growing importance of distributed systems software design in the development of more efficient computer systems.

An adaptation of a development system for sequential programs which was designed for small microcomputer environments is proposed. The new architecture will support the scientific computation that is performed in Supervisory and Control Systems for Electric Power Networks. The main aspects considered in the extended machine are:

- The maintenance of the portability of the original system;

- The use of microprocessors connected in a tightly coupled topology;

- The replacement of the linear stack by a new structure, more adequate to parallel processing;

- The design of improved techniques for memory management.

A prototype based on a 8086 microprocessor emulates some of the functions that were specified for the virtual processor. In the implementation of the future stages of the project the use of more sofisticated components is antecipated.

ÍNDICE

|              |                                                         |    |

|--------------|---------------------------------------------------------|----|

| CAPÍTULO I   | - INTRODUÇÃO                                            | 1  |

| CAPÍTULO II  | - ARQUITETURAS PARA PROCESSAMENTO PARALELO              | 4  |

| II.1.        | - Aumentando a Performance dos Computadores<br>Digitais | 4  |

| II.2.        | - Características dos Computadores Paralelos            | 12 |

| II.2.1.      | - Modelo de von-Neumann                                 | 12 |

| II.2.2.      | - Classificação de Flynn                                | 14 |

| II.2.3.      | - Outros Modelos                                        | 16 |

| II.3.        | - Arquiteturas Sistólicas                               | 16 |

| II.4.        | - Sistemas de Fluxo de Dados                            | 23 |

| II.5.        | - Processamento "Pipeline"                              | 28 |

| II.6.        | - Processamento Associativo                             | 34 |

| II.7.        | - "Array Processors"                                    | 39 |

| CAPÍTULO III | - ARQUITETURAS MIMD UTILIZANDO MICROPROCESSADORES       | 45 |

| III.1.       | - Multiprocessadores                                    | 47 |

| III.1.1.     | - Requisitos Básicos                                    | 49 |

| III.1.2.     | - Estruturas de Interconexão                            | 49 |

| III.2        | - Redes Locais de Comunicação                           | 53 |

| CAPÍTULO IV  | - SISTEMA-P UCSD                                        | 60 |

| IV.1.        | - Organização do Sistema-P                              | 61 |

| IV.2.        | - Máquina-P UCSD                                        | 65 |

| IV.2.1.      | - Tipos de Dados Manipulados pela Máquina-P             | 70 |

| IV.2.2.      | - Conjunto de Instruções                                | 73 |

| CAPÍTULO V   | - ARQUITETURA PROPOSTA                                  | 75 |

| V.1.         | - Principais Aspectos Considerados                      | 75 |

|                               |                                  |     |

|-------------------------------|----------------------------------|-----|

| V.2.                          | - Topologia                      | 76  |

| V.3.                          | - Barramento Global              | 76  |

| V.4.                          | - Processador Real               | 78  |

| V.4.1.                        | - O Microprocessador             | 78  |

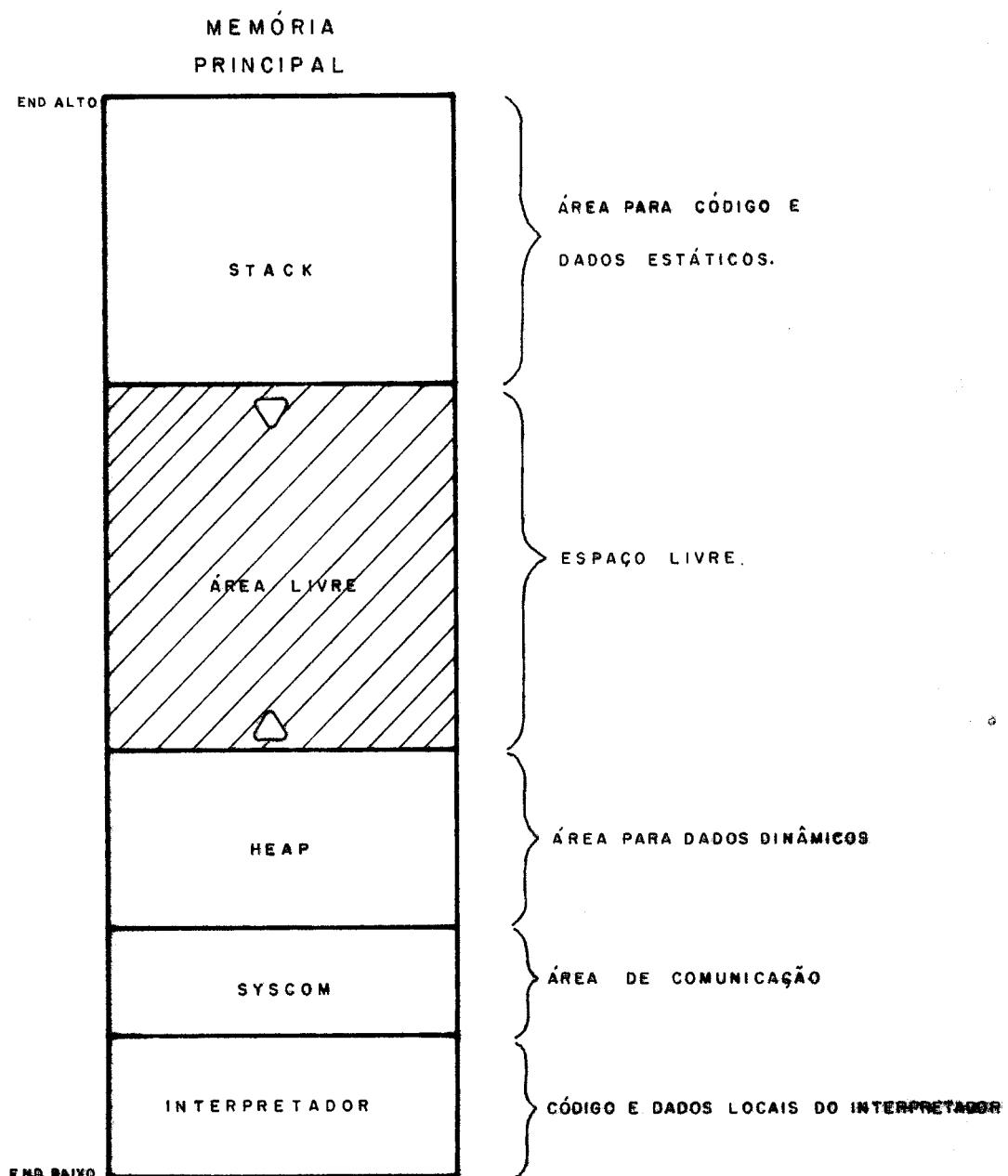

| V.5.                          | - Memória Principal              | 83  |

| V.6.                          | - Outros Recursos Disponíveis    | 93  |

| V.6.1.                        | - Dispositivos Globais de E/S    | 94  |

| V.6.2.                        | - Dispositivos Locais de E/S     | 96  |

| CAPÍTULO VI - SOFTWARE BÁSICO |                                  | 97  |

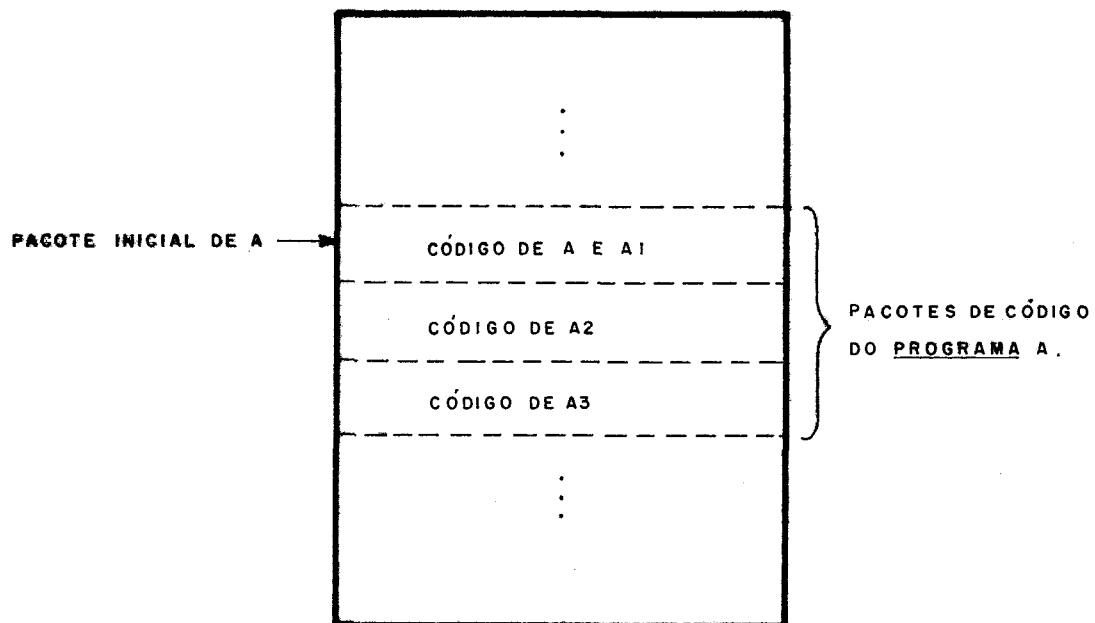

| VI.1.                         | - Máquina-P Estendida            | 97  |

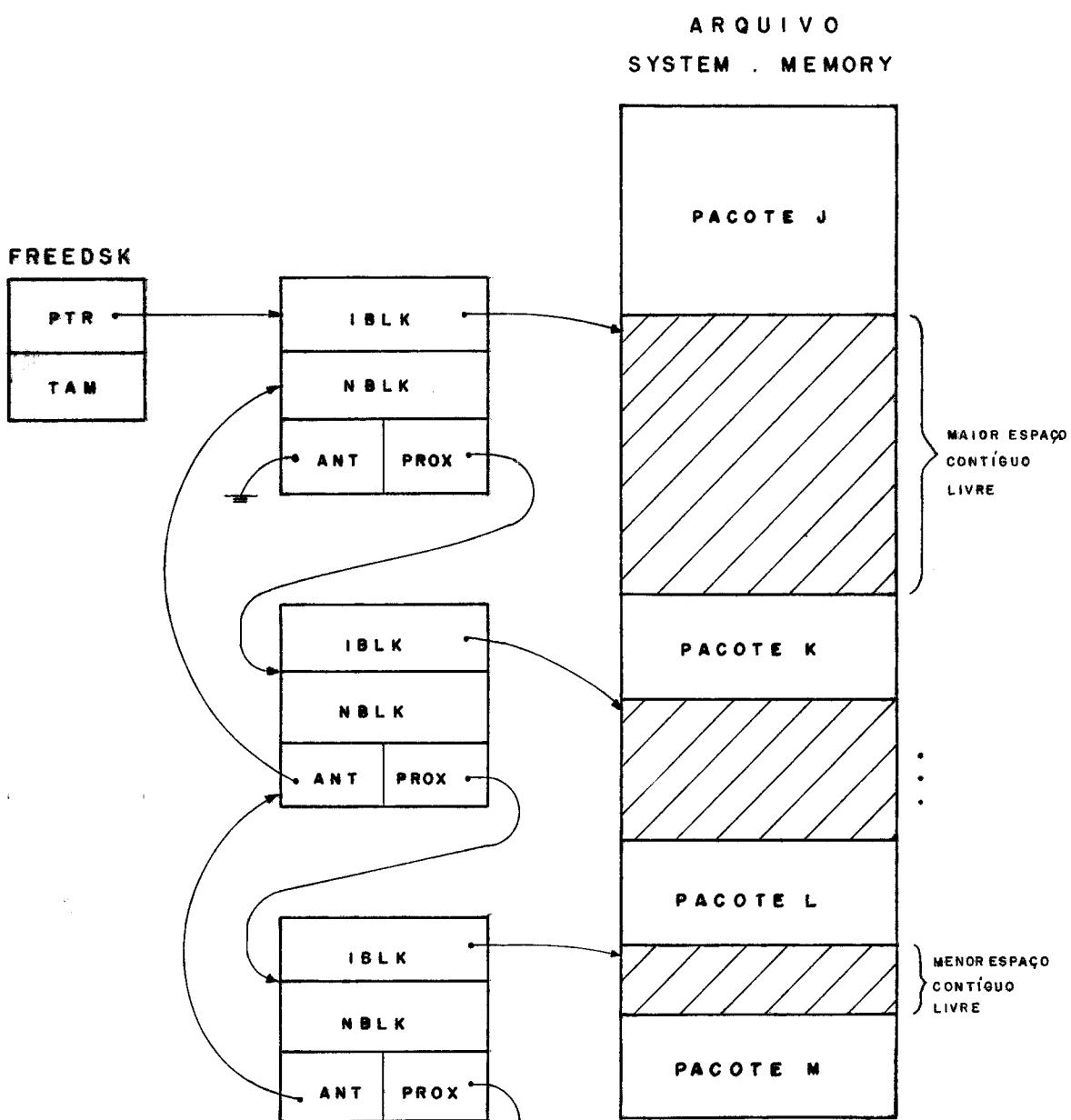

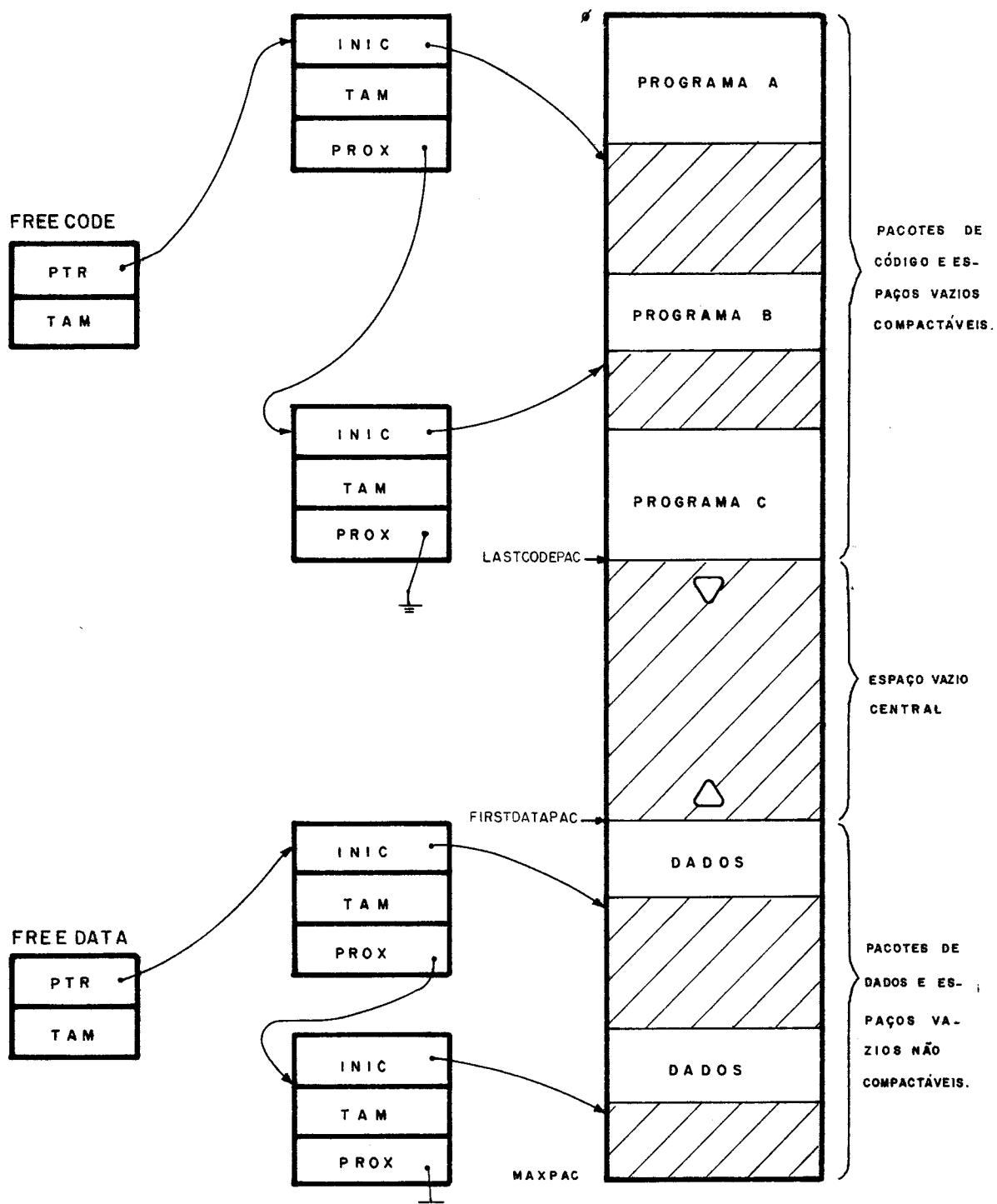

| VI.2.                         | - Gerência de Memória            | 108 |

| VI.3.                         | - Ativação Dinâmica de Programas | 133 |

| CAPÍTULO VII - CONCLUSÃO      |                                  | 137 |

| BIBLIOGRAFIA                  |                                  | 138 |

## I. INTRODUÇÃO

As ciências associadas à computação tem, inegavelmente, evoluído muito rapidamente desde a sua criação. Contudo, observando-se um passado recente, verifica-se que os ganhos em eficiência que foram introduzidos nas máquinas, vem sendo consumidos por tarefas que tem igualmente crescido em complexidade. Esta constatação é confirmada, por exemplo, pela verificação de que o tempo de resposta dos sistemas operacionais multi-usuários não tem variado tanto quanto o potencial dos computadores que os executam.

Os microprocessadores preencheram, durante a última década, espaços que até então estavam inexplorados ou ocupados de forma inefficiente por minicomputadores ou circuitos com lógica discreta. Atualmente, após a consolidação deste mercado, buscam-se novas técnicas que possam alargar o espectro de utilização destes componentes. Uma alternativa bastante promissora tem sido a exploração de estruturas compostas por vários elementos inteligentes, não muito complexos, que, através de cooperação mútua, tenham capacidade para resolver problemas de grande porte. Os Capítulos II e III apresentam a descrição de diversas arquiteturas adequadas ao processamento paralelo.

O presente trabalho faz parte de um programa estabelecido pelo CEPEL para o desenvolvimento de Sistemas de Supervisão e Controle para Sistemas Elétricos de Potência. Os resultados produzidos por este programa tem atendido, até o presente momento, às diretrizes básicas estabelecidas, que são:

- Aquisição de grandezas representativas do estado do sistema elétrico, junto aos processos que estão sendo supervisionados;

- Transmissão das informações aquisitadas através de uma estrutura hierarquizada de centros de tratamento de informação e

- Interação com o elemento humano, visando a exteriorização do

estado do sistema e a aceitação de comandos que o modifiquem.

Nesta linha, foram projetados e construídos um Terminal Remoto para Aquisição de Dados (70, 71) e um Centro de Supervisão Regional (72). Ambos os sistemas estão sendo atualmente industrializados, acarretando a economia de um volume significativo de divisas para o setor, através da nacionalização de tecnologia e equipamentos. Em termos brasileiros, estes projetos ganham ainda maior importância, quando se constata a gama de possíveis aplicações que podem utilizá-los. Como exemplo, podem ser citados o controle e supervisão de siderúrgicas, refinarias, centrais de abastecimento de água e processos industriais de uma forma geral. Todas estas atividades oneram substancialmente a balança de importações atual.

O desenvolvimento deste trabalho foi motivado pela necessidade de promover a expansão vertical da linha anteriormente citada, pois os modernos centros de controle exigem cada vez mais a incorporação de funções complexas de processamento. Estas funções incluem estimadores de estado, configuradores, fluxos de potência, etc.. Estas tarefas vem sendo realizadas por minicomputadores de "grande porte" (como o VAX 11/780), pois demandam uma capacidade de processamento superior àquela permitida pelos microcomputadores comerciais atuais (1).

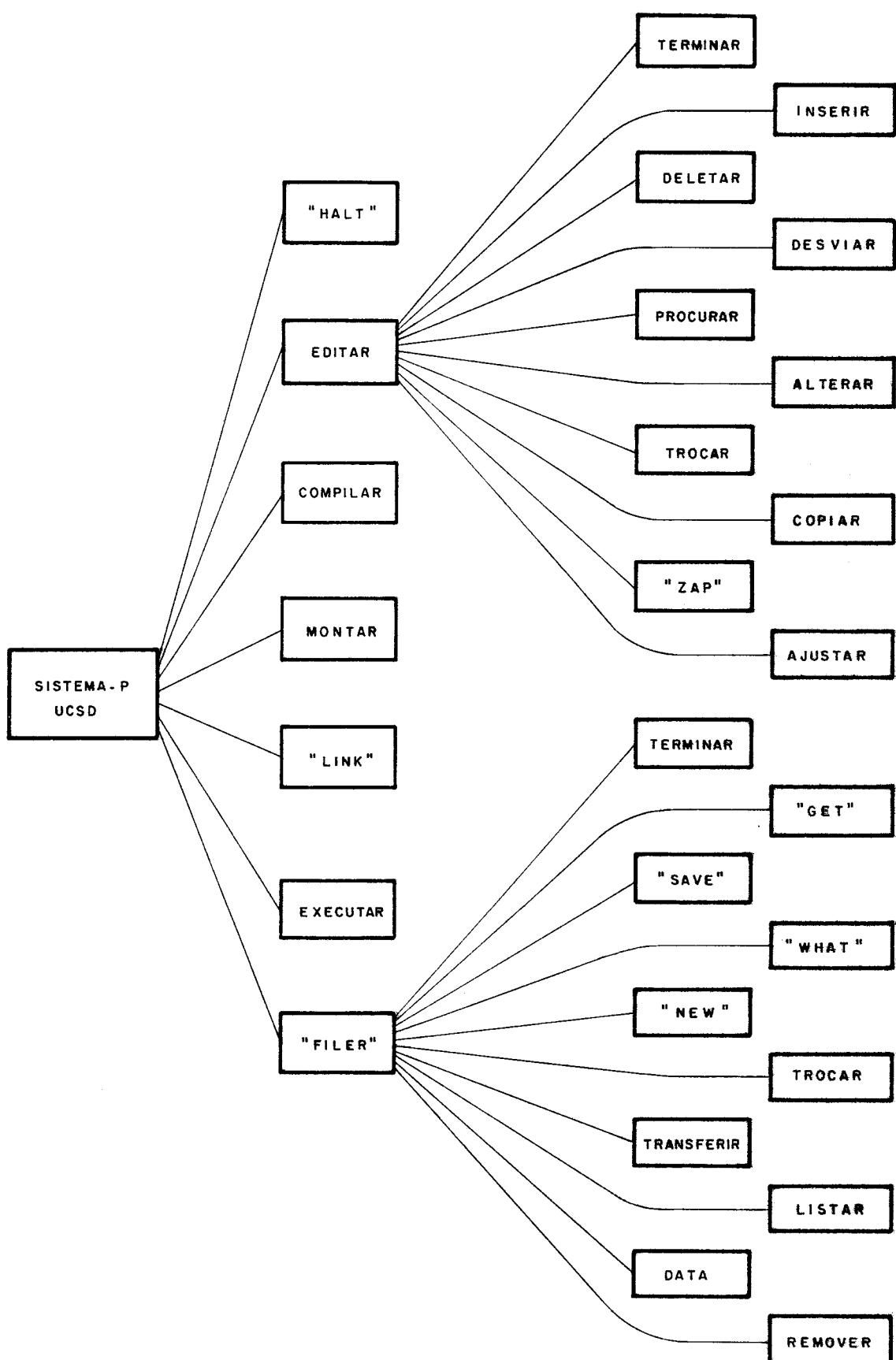

Como ponto de partida para a realização do software do projeto foi utilizado um sistema construído pela Universidade da Califórnia em San Diego (UCSD), capacitado para fornecer aos usuários de microcomputadores facilidades de edição, compilação e execução de programas sequenciais. O Sistema-p, como é chamado, é na sua maior parte escrito em linguagem de alto nível e pode ser facilmente adaptado a diversos ambientes de computação. Um pseudo-processador, que executa um código intermediário (código-p), garante que somente uma pequena parte do sistema (correspondente à emulação da máquina virtual) esteja diretamente relacionado com o hardware específico de uma determinada implementação.

A adaptação do Sistema-p para atender aos requisitos do projeto

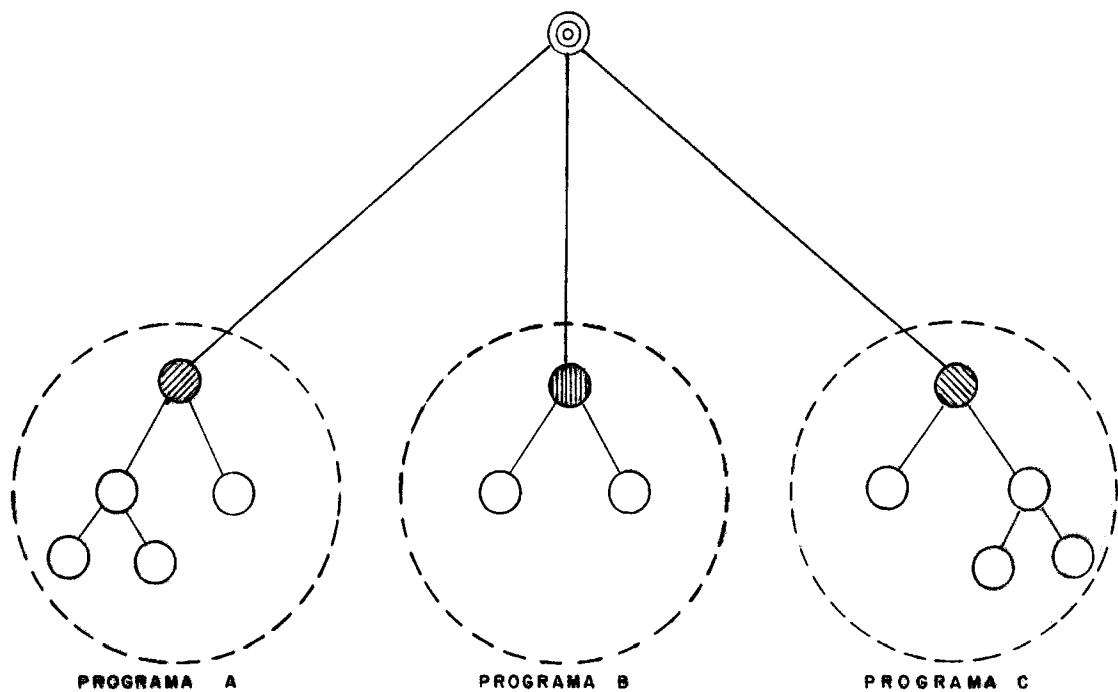

foi dividida em duas etapas: adaptação da linguagem Pascal UCSD à programação concorrente e a especificação de uma arquitetura que emulasse o pseudo-processador do Sistema-p. A primeira etapa, que encontra-se descrita em Barbosa et al (69), adicionou diversos construtos à linguagem para possibilitar o sincronismo entre processos concorrentes e garantir a exclusão mútua aos recursos comuns por eles compartilhados. A etapa aqui descrita inclui o projeto de uma arquitetura baseada em microprocessadores dispostos segundo uma topologia fortemente conectada, além da especificação de um interpretador capaz de executar o pseudo-código da máquina-p estendida. As principais alterações realizadas na versão original do sistema, descritas nos dois últimos capítulos deste trabalho, são:

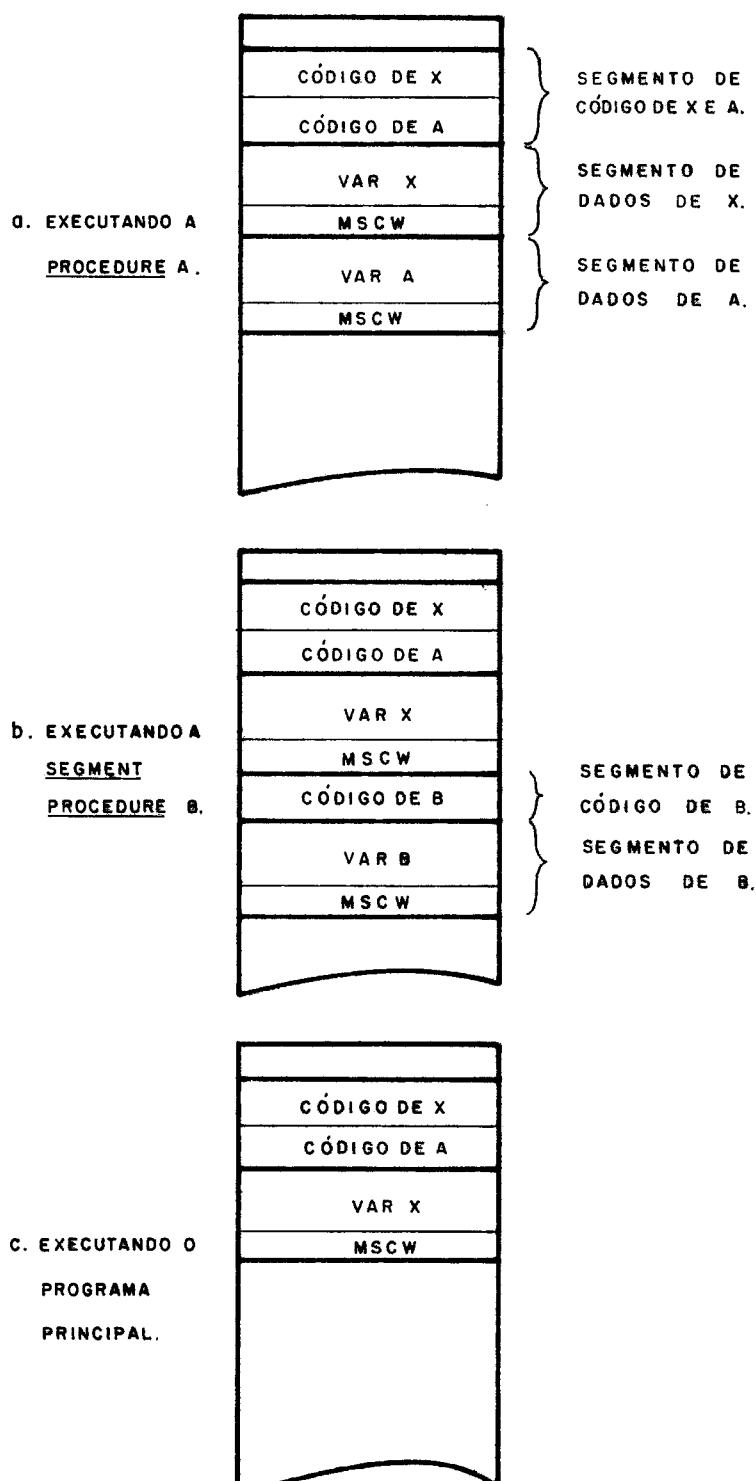

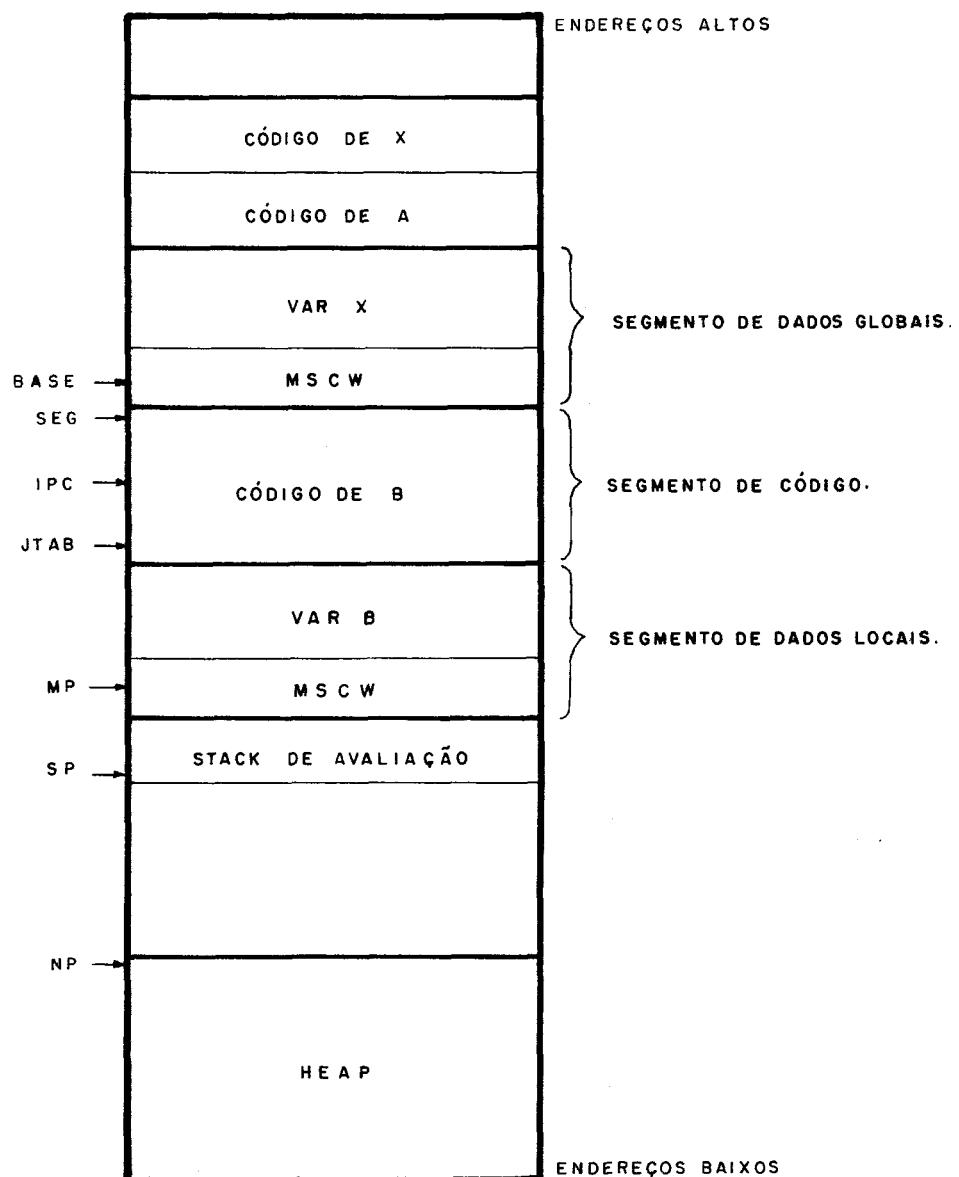

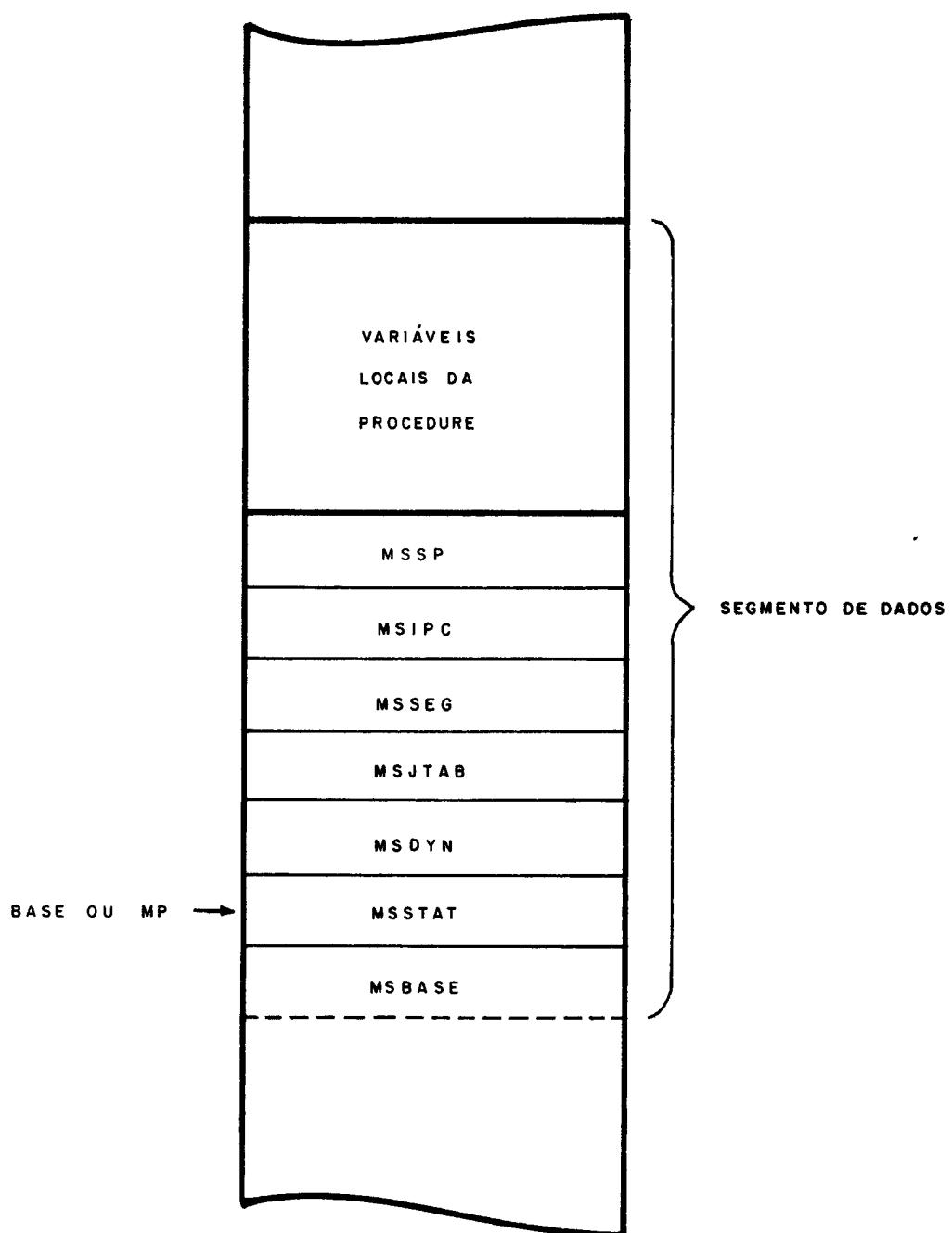

- a extensão do stack linear da máquina-p para uma estrutura em árvore que permitisse o acesso simultâneo de diversos processos a regiões comuns de memória;

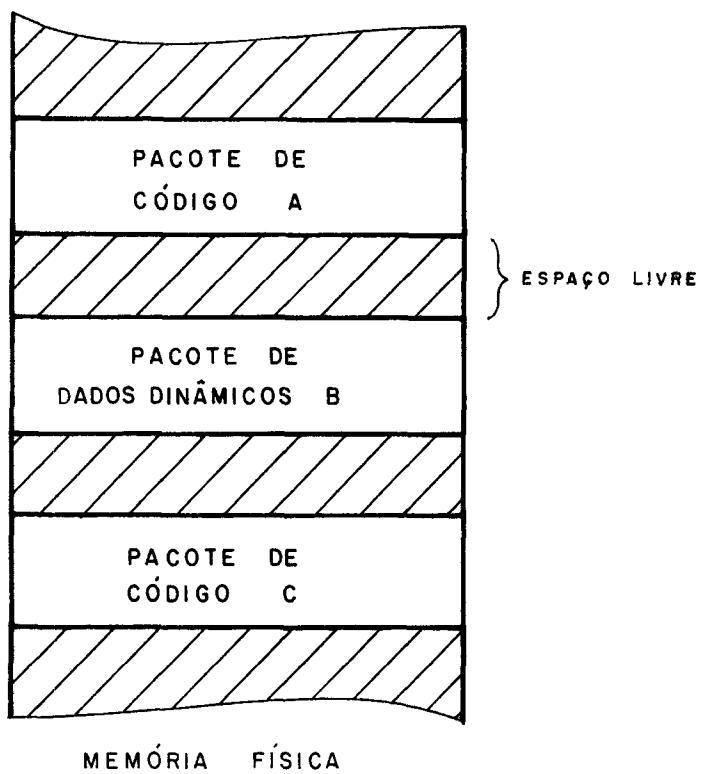

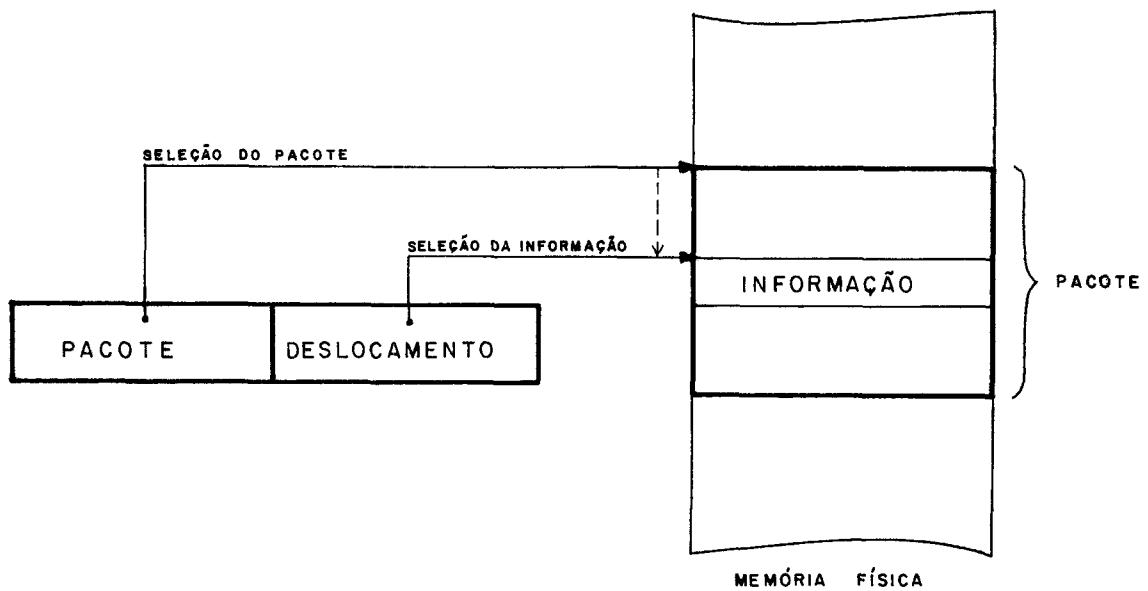

- a partição da memória principal em segmentos distintos, visando a separação das áreas de código e dados estáticos e dinâmicos;

- a introdução de memória virtual, para armazenar os diversos segmentos existentes e

- otimização da alocação do espaço físico de memória através de páginas fixas.

## II. ARQUITETURAS PARA PROCESSAMENTO PARALELO

A performance de um determinado sistema computacional depende de vários fatores, que podem ser agrupados em duas categorias. A primeira classe leva em consideração apenas os aspectos externos ou inerentes às máquinas que estão sendo usadas. A eficiência do software de aplicação, traduzida pela organização e qualidade dos algoritmos empregados, são exemplos de fatores situados nesta classe. Outro fator importante é a interação com o homem, que quando bem explorada resulta numa máxima utilização do potencial humano, sem que suas limitações afetem a performance do sistema como um todo.

A segunda classe de fatores diz respeito às características dos elementos utilizados para realizar o processamento. Basicamente, incluem-se neste caso o hardware do equipamento e o software que o controla. Atualmente não são bastante nítidas as fronteiras entre estes dois territórios, razão pela qual se deve sempre considerar a influência de uma decisão em ambas as partes.

Este capítulo irá discorrer sobre as principais atividades que consomem o trabalho de pesquisa da atualidade, tentando maximizar a performance dos computadores atuais através desta última classe de alternativas.

### II.1. AUMENTANDO A PERFORMANCE DOS COMPUTADORES DIGITAIS

Dando ênfase especial às características físicas da máquina, podem ser citados alguns fatores que influenciam bastante a performance de um sistema computacional.

- Tecnologia de fabricação dos componentes,

- Adequação da arquitetura à aplicação, e

- Grau de concorrência com que são executados os programas.

O primeiro item é de vital importância, porque foram os progressos introduzidos nos últimos anos que possibilitaram os

enormes aumentos de velocidade, densidade e sofisticação dos circuitos lógicos. A origem desta evolução se baseou na perspectiva de redução dos custos de processamento de componentes, proporcional ao aumento da densidade dos mesmos. Este fato, aliado à demanda de sistemas mais compactos - por razões diversas como: tamanho, confiabilidade, etc. - incentivaram ainda mais o refinamento da produção, criando nas indústrias do setor uma espécie de compulsão à miniaturização.

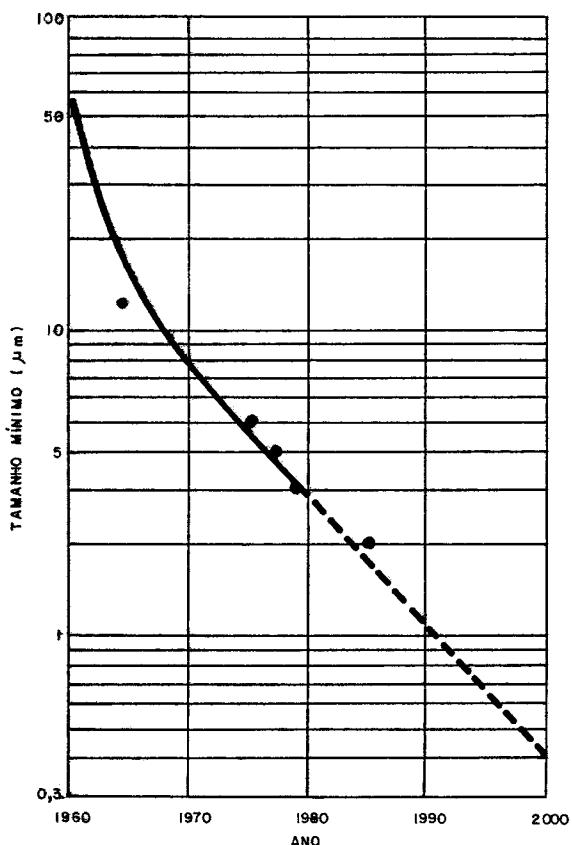

Os dispositivos atuais apresentam resolução da ordem de dois microns, como podemos ver na Figura II.1. A expectativa para a próxima década é reduzir este tamanho em uma ordem de grandeza, forçando uma mudança na unidade de medida para angstrons (2). A fotolitografia, o meio pelo qual os resistores químicos são expostos através de máscaras para definir a geometria dos dispositivos, é o processo que garante as menores dimensões possíveis atualmente.

Entretanto, a utilização da luz para exposição estará sempre limitada à faixa de 1 um, quando então passará a ser imperativo o uso de raios-x, feixes de elétrons ou feixes de íons no processo litográfico. É prevista também a substituição dos reveladores líquidos - que apresentam um comportamento irregular - por um processamento a seco, utilizando plasma.

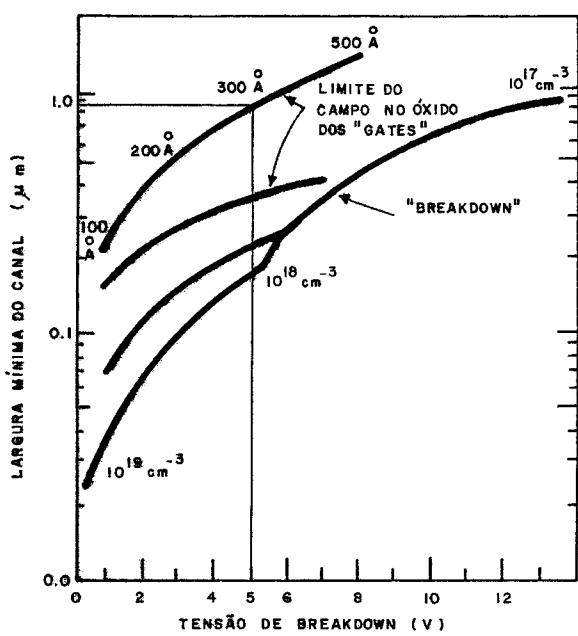

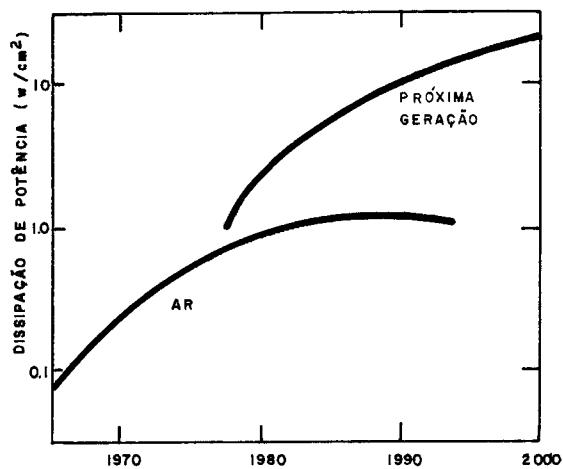

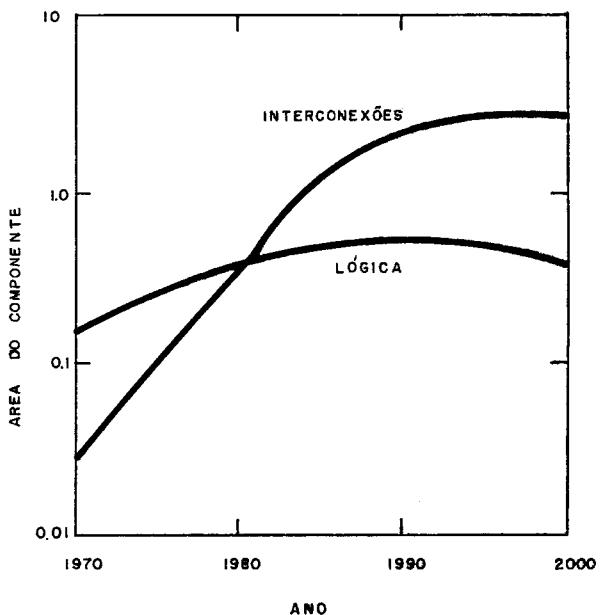

Por outro lado, mesmo que os problemas de exposição e revelação das geometrias submicrométricas sejam resolvidos, não há garantia de que seja possível uma produção em massa destes componentes. Antes que os limites da tecnologia atual sejam ultrapassados, outros fatores precisarão ser levados em consideração. Será preciso entender e modelar o comportamento das submicro-estruturas (Figura II.2), descobrir um meio de conectar a enorme quantidade de dispositivos que serão produzidos num mesmo substrato (Figura II.3) e desenvolver encapsulamentos adequados à rápida dissipação de calor (Figura II.4).

FIGURA II. 1 - TAMANHOS MÍNIMOS EM CIRCUITOS INTEGRADOS : UMA REDUÇÃO VERTIGINOSA.

FIGURA II. 2 - "BREAKDOWN": OS CAMPOS ELÉTRICOS CRESCEM À MEDIDA QUE OS DISPOSITIVOS DIMINUEM. UM "GATE" DE 300  $\text{\AA}$  DEVERÁ ROMPER-SE COM UMA TENSÃO DE 5 V, QUANDO O CANAL ULTRAPASSAR A MARCA DE 1  $\mu\text{m}$ . ESPERA-SE UMA REDUÇÃO DAS FONTES DE ALIMENTAÇÃO PARA CIRCUITOS VLSI.

**FIGURA II.3 - LIGAÇÕES :**

AS LIGAÇÕES INTERNAS DEMANDAM

CADA VEZ MAIS ESPAÇO NOS "CHIPS".

ESTE NÃO É DOS PIORES PROBLEMAS,

MAS VEM MERECENDO ATENÇÃO ESPE-

CIAL DE ALGUNS FABRICANTES.

**FIGURA II.4 - DISSIPAÇÃO DE CALOR :**

A LIMITAÇÃO DOS INVÓLUCROS QUE UTILIZAM

AR OBRIGARÁ A UTILIZAÇÃO DE UM OUTRO

MEIO REFRIGERANTE (MEIOS LÍQUIDOS PERMITEM

UM LIMITE DE 20 w/cm<sup>2</sup>).

As tecnologias disponíveis atualmente são várias, e a Tabela II.1 apresenta uma comparação entre as principais (2). Esta tabela não inclui algumas tecnologias "não-siliciana", como por exemplo as junções Josephson, que utilizando nióbio ou chumbo apresentam uma velocidade natural da ordem de 1ps com produto velocidade-potência no mínimo três ordens de grandeza menor que os dispositivos de Si e GaAs (3).

Os principais candidatos para aplicação em VLSI ("Very Large Scale Integration") são as tecnologias  $I^2L$  (ou outra forma de lógica-de-corrente), n-MOS, C-MOS e GaAs (2).

O futuro dos dispositivos bipolares é incerto, por causa do grande número de passos necessários ao seu processamento, principalmente porque na maioria deles é necessária a introdução de impurezas por difusão ou implantação de íons. Outro problema dos dispositivos bipolares é a tendência a dissipar mais potência que as outras tecnologias. Uma excessão à regra são os dispositivos  $I^2L$ , que com um baixo produto velocidade-potência poderão se compatibilizar com o processamento VLSI. Incluem-se nesta lista algumas variantes desta tecnologia que estão em fase de estudo:  $I^2L/MTL$  ("merged-transistor logic"), ISL ("integrated schottky logic") e STL ("schottky transistor logic").

As tecnologias MOS deverão representar um papel importante em VLSI por diversas razões. Assim, apesar da perspectiva então pessimista no aumento da densidade, os projetistas de dispositivos agiram acertadamente quando decidiram investir em melhoramentos nesta tecnologia (4). Os dispositivos MOS consomem pouca potência e são também auto-isolantes. Isto significa que as cargas podem ser armazenadas nos "gates" capacitivos, viabilizando, por exemplo, a lógica dinâmica empregada na construção de memórias.

Uma razão importante para o uso de silício na fabricação de componentes eletrônicos é a facilidade com que são criadas camadas isolantes neste material. Entretanto, a demanda de dispositivos mais rápidos e densos leva a que se continue a investigar materiais alternativos. Contudo, existem ainda

| PROPRIEDADE                                                               | TECNOLOGIA ATUAL - 1979 - 1982 |               |                |                  |                   |                |                 |                | FUTURO, 1985-1990             |                       |

|---------------------------------------------------------------------------|--------------------------------|---------------|----------------|------------------|-------------------|----------------|-----------------|----------------|-------------------------------|-----------------------|

|                                                                           | BIPOLAR                        |               |                |                  | MOS               |                |                 |                | SILÍCIO EM<br>SAFIRA<br>(sos) | ARSENIATO<br>DE GÁLIO |

|                                                                           | TTL                            | LSTTL         | ECL            | I <sup>2</sup> L | p-MOS             | n-MOS          | C-MOS(bulk)     | C-MOS(SOS)     |                               |                       |

| COMPLEXIDADE DO PROCESSO (NÚMERO DE PASSOS REALIZADOS)                    | 18 A 22                        | 18 A 23       | 19 A 23        | 13 A 17          | 8 A 14            | 9 A 15         | 14 A 17         | 14 A 20        | 14 A 20                       | 16                    |

| COMPLEXIDADE DA LÓGICA (NÚMERO DE COMPONENTES EM UMA PORTA C/ 2 ENTRADAS) | 12                             | 12            | 8              | 3 A 4            | 3                 | 3              | 4               | 4              | 3 A 4                         | 2                     |

| DENSIDADE DE EMPACOTAMENTO (PORTAS/MM <sup>2</sup> )                      | 10 A 20                        | 20 A 40       | 15 A 20        | 75 A 150         | 75 A 150          | 100 A 200      | 40 A 90         | 100 A 200      | 200 A 500                     | 300 A 1000            |

| TEMPO DE PROPAGAÇÃO (ns) (VALOR TÍPICO)                                   | 6 A 30<br>(10)                 | 2 A 10<br>(5) | 0.7 A 2<br>(2) | 7 A 50<br>(20)   | 30 A 200<br>(100) | 4 A 25<br>(15) | 10 A 35<br>(20) | 4 A 20<br>(10) | 0.2 A 0.4<br>(0.3)            | 0.05 A 0.1<br>(0.07)  |

| PRODUTO DE VELOCIDADE DE POTÊNCIA (pJ)                                    | 30 A 150                       | 10 A 60       | 15 A 80        | 0.2 A 2          | 50 A 500          | 5 A 50         | 2 A 40          | 0.5 A 30       | 0.1 A 0.2                     | 0.01 A 0.1            |

| CHANCE DE MELHORAMENTO                                                    | BAIXA                          | BAIXA         | BAIXA          | MODERADA         | BAIXA             | ALTA           | MODERADA        | ALTA           | ALTA                          | ALTA                  |

TABELA II.1 - OPÇÕES TECNOLÓGICAS

problemas a enfrentar, como no caso das memórias de bolhas magnéticas que, após conseguirem superar em quatro vezes a densidade dos dispositivos de silício, tiveram sua produção interrompida por diversos fabricantes de renome internacional. Outras tecnologias, como as que usam o arseniato de gálio - que é extremamente tóxico e não permite a criação de camadas isolantes, e os materiais supercondutores das junções Josephson - que só funcionam à temperaturas perto do zero absoluto, tem atualmente custos que não incentivam o seu processamento e operação em escala comercial.

Outro fator que influencia a performance dos computadores digitais é a compatibilidade entre a sua arquitetura e as necessidades para as quais eles estão sendo projetados (5). Eis alguns parâmetros que são normalmente observados durante a especificação de uma máquina:

1. Tamanho da palavra: Pode-se medir a velocidade de um computador através do número de bits por ele processados em cada unidade de tempo. Observando-se que um único processador convencional opera uma palavra por vez, chega-se à conclusão de que a otimização do tamanho da palavra, para atender a uma determinada aplicação, é altamente desejável. Este fato pode ser notado durante a execução de programas numéricos que necessitam de precisão múltipla, em computadores com palavras de tamanho reduzido.

2. Conjunto de instruções: As aplicações que utilizam um determinado tipo de operação muito frequentemente demandam um processo especial de tratamento que dedique atenção a elas. Em caso contrário, será necessária a emulação destas operações por um conjunto de outras primitivas, o que certamente ocasionará certa ineficiência. Algumas situações críticas requerem até a introdução de coprocessadores ou controladores inteligentes, especialmente projetados para executar uma função específica. São casos típicos e bastante conhecidos os processadores de ponto flutuante e os canais que interligam dispositivos de entrada/saída diretamente à memória.

3. Organização do sistema: A topologia de interconexão dos elementos principais - unidade(s) de controle, unidade(s) aritmética(s) e lógica(s), módulo(s) de memória e controlador(es) de E/S - desempenha um papel bastante importante na caracterização de uma máquina. É através da topologia que serão especificadas as regras que irão governar o fluxo de dados e controle entre as unidades, incluindo a possibilidade de caminhos simultâneos.

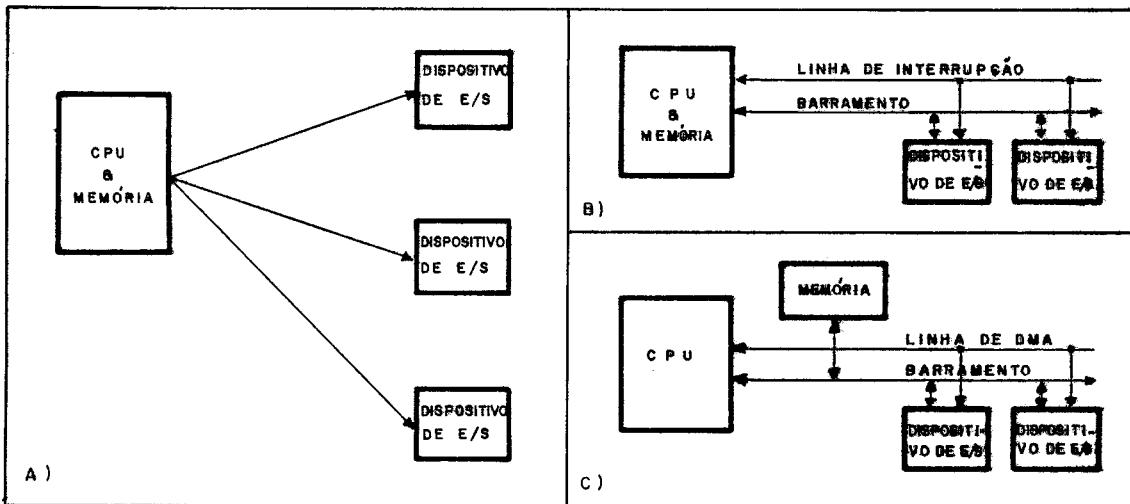

4. Dispositivos de entrada/saída: Normalmente a especificação de um sistema dedica um grande esforço na parte que se refere à manipulação interna de dados. Mas a facilidade com que o computador se comunica com o resto do sistema também contribui de forma bastante significativa para sua performance final (6). Os pontos principais a serem considerados são em primeiro lugar a compatibilidade entre a demanda da troca de informação desejada e a capacidade do periférico em atendê-la. Este requisito é influenciado não só pelo tipo de unidade a ser usada, mas também pelas conexões existentes entre processador(es), memória(s) e periférico(s). Em segundo lugar deve ser escolhida uma forma de tratar a entrada/saída, (Figura II.5), que satisfaça aos requisitos de tempo de resposta, taxa de ocupação do processador, etc..

Um outro fator que exerce influência sobre a performance de um sistema computacional diz respeito ao grau de paralelismo com que são executadas as suas funções. A descentralização da inteligência permite melhorar a eficiência de uma máquina sem que seja necessário aumentar a velocidade individual de seus componentes. Contudo, para que se possa tirar o melhor proveito do paralelismo é preciso que sejam investigadas estruturas que melhor se adaptem a cada caso. As experiências que vem sendo realizadas tem comprovado o potencial desta solução. Os maiores problemas encontrados estão associados à maior complexidade funcional das estruturas paralelas, devido justamente à concorrência existentes entre suas partes.

O assunto paralelismo será abordado neste trabalho em seguida. A discussão será, a princípio, orientada para a definição e

classificação das arquiteturas para processamento paralelo.

## II.2. CARACTERÍSTICAS DOS COMPUTADORES PARALELOS

A disciplina de arquitetura de computadores está atualmente em um período de transição. O advento de VLSI e de ferramentas automáticas para o desenvolvimento de sistemas (7) liberaram os projetistas de restrições que até hoje impediram uma evolução maior na área. Como consequência, vive-se hoje uma fase de consolidação de conhecimentos, através da realização e observação de experiências - pré-requisitos essenciais para a elaboração de uma boa formulação científica. O que se apresenta a seguir é um levantamento destas experiências.

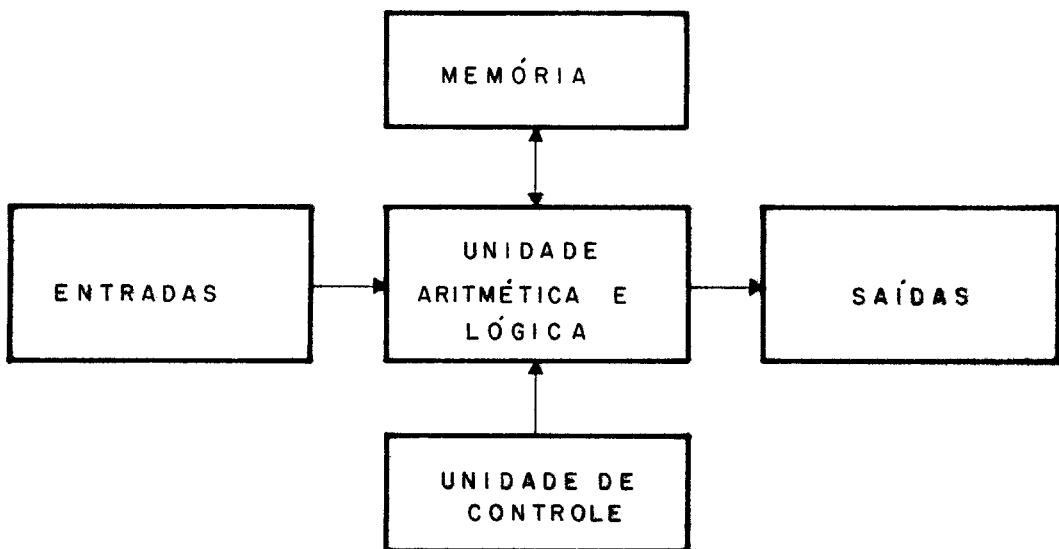

### II.2.1. Modelo de von-Neumann

John von Neumann estabeleceu uma arquitetura que se aplicava a um "instrumento para processamento de informações" (8). Este instrumento era composto por uma unidade central de processamento (CPU), que operava sequencialmente em dados baseados e armazenados de forma serial numa memória. Esta filosofia de execução sequencial dominou os computadores digitais por mais de trinta anos, fornecendo máquinas versáteis, gerais e com uma excelente relação custo-benefício. Os principais elementos desta arquitetura encontram-se na Figura II.6. A maioria das arquiteturas que iriam suceder à máquina de von Neumann continuariam a utilizar tais elementos, sob diferentes formas de agrupamento.

A memória consiste de células de informação ordenadas sequencialmente, que são acessadas normalmente através de endereço ou conteúdo. As operações usualmente previstas para a memória são leitura e escrita, mutuamente exclusivas.

A unidade aritmética e lógica (ALU), como o nome indica, é responsável pelas transformações matemáticas que são realizadas nos dados.

FIGURA II.5 - CASOS TÍPICOS DE TRATAMENTO DE E/S :

- A) "LOOP" DE ESPERA (" POLLING");

- B) INTERRUPÇÃO E

- C) ACESSO DIRETO A MEMÓRIA

FIGURA II.6 - ARQUITETURA PROPOSTA POR VON NEUMMAN

A unidade de controle coordena o intercâmbio de informações entre as demais unidades, bem como as operações realizadas por elas. É também esta unidade que responde aos sinais externos de interrupção através de alteração na sequência de execução dos programas. O termo processador se refere à combinação de uma unidade de controle e uma ou mais ALU's.

As unidades de entrada e saída (E/S) possibilitam ao computador a troca de informações com outros equipamentos. As operações de E/S são utilizadas com quatro finalidades: armazenamento de informações, comunicação com o elemento humano, comunicação com outros computadores e transdução de sinais.

As linhas que interligam os módulos da Figura II.6 representam os canais de endereçamento, controle e dados do computador. A capacidade destes canais é caracterizada por vários fatores como a impedância dos circuitos de acoplamento, banda passante dos condutores, ruído, taxa de falhas desejada, quantidade de linhas, etc.. Os meios de conexão constituem um capítulo importante nas arquiteturas paralelas.

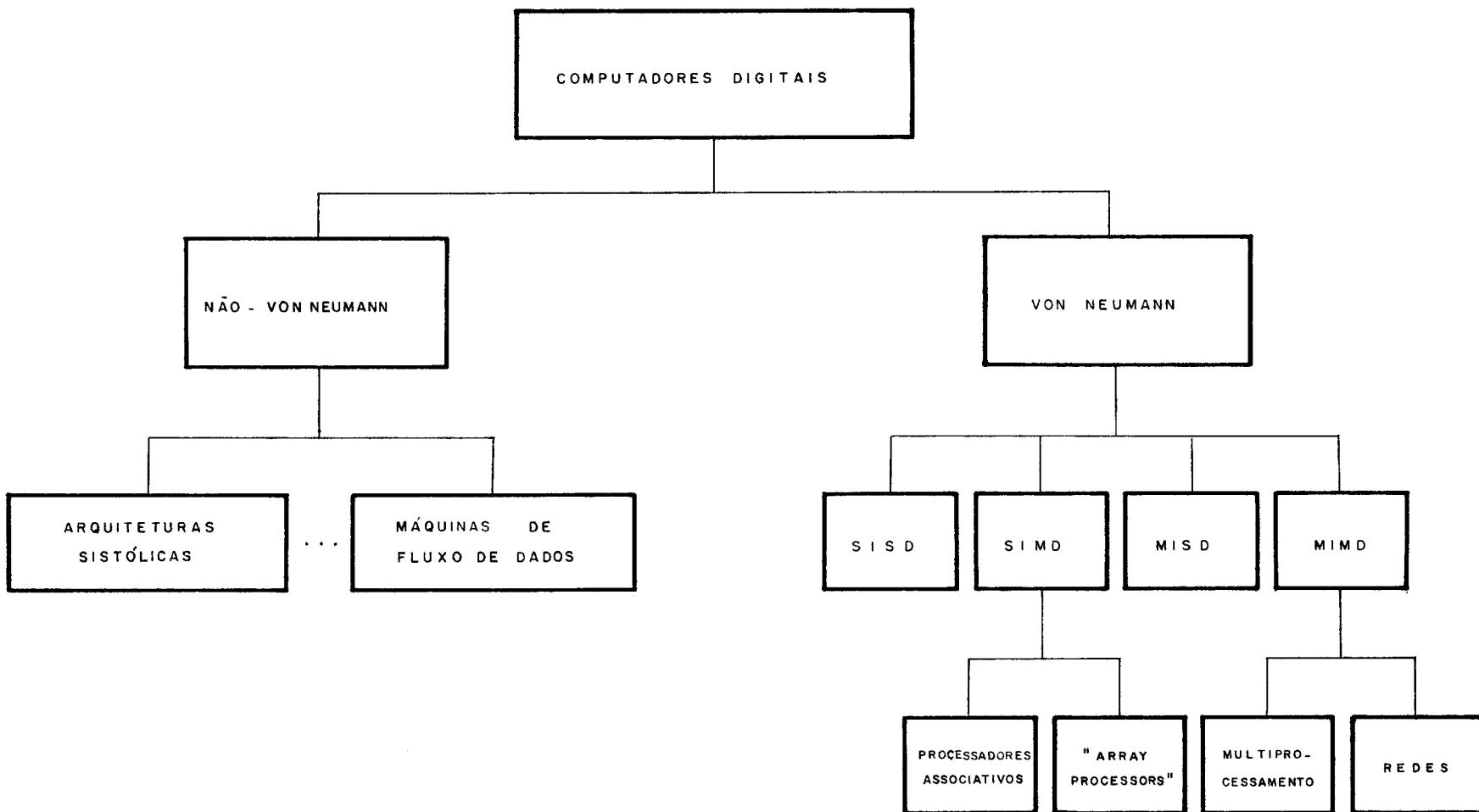

## II.2.2. CLASSIFICAÇÃO DE FLYNN

Até o início da década de 70 não havia uma classificação ou codificação para as estruturas "von Neumannianas" que fosse largamente aceita. A razão é que ou o assunto era abordado sob um ponto de vista microscópico demais, através da teoria dos autômatas, ou então eram tomados como referência grupos específicos de máquinas e/ou problemas. Flynn então sugeriu uma divisão hierárquica (9) que, utilizando o conceito de "stream" (\*), tratava do assunto de uma forma bastante macroscópica, sem fixar-se em nenhum ambiente particular. A classificação se baseava no grau de interação entre os "streams" de instruções e dados das diversas estruturas, resultando no aparecimento de quatro tipos de organização:

1. "Single-instruction stream/single-data stream" (SISD): Este grupo representa os equipamentos convencionais de computação, onde as instruções são executadas sequencialmente, manipulando um dado de cada vez.

2. "Single-instruction stream/multiple-data stream" (SIMD): Estes computadores apesar de executarem uma única instrução por vez, manipulam várias peças de informação simultaneamente. Incluem-se nesta categoria os "array processors" em geral e as máquinas associativas.

3. "Multiple-instruction stream/single data stream" (MISD): Há controvérsia na literatura sobre a existência ou até mesmo sobre o significado de uma máquina MISD, porque isto implicaria na manipulação simultânea de um mesmo dado por duas ou mais instruções. É óbvio que isto não é válido para uma única fração elementar de dado, mas o conceito de "stream" pode ser estendido para tipos de dados mais complexos, passando então a fazer sentido esta classificação. O processador "pipeline" satisfaz, segundo alguns, os critérios necessários aos membros desta classe.

4. "Multiple-instruction stream/multiple -data stream" (MIMD): Esta categoria abrange todos os sistemas que, executando mais de uma instrução por vez, manipulam simultaneamente várias peças de dados. A revolução dos mini e micro-computadores permitiu o desenvolvimento de todo o potencial das organizações múltiplas, tanto em rede de computadores como em arquiteturas a multiprocessador.

---

(\*) "Stream" neste contexto significa uma sequência de itens (instruções ou dados) na forma em que são executados ou operados por um processador.

### II.2.3. OUTROS MODELOS

Para complementar a classificação dos computadores paralelos é preciso fugir do conceito de máquina orientada para "streams" (de dados ou instruções) e até mesmo do modelo de von Neumann. Para isso, faz-se necessária uma abstração dos conceitos de execução sequencial de programas e de memórias endereçadas globalmente, que vinculam fatalmente uma arquitetura aos casos já citados anteriormente. O trabalho de classificação do grupo não alinhado à von Neumann ainda está para ser feito, havendo no entanto alguns casos isolados que podem ser citados. É o caso de máquinas digitais (10 a 15) especialmente projetadas para uma determinada aplicação e dos sistemas de fluxo de dados (23 a 30) que vem sendo estudado como uma alternativa geral para as máquinas e linguagens tradicionais.

A Figura II.7 engloba as categorias citadas até o presente momento. Os demais itens deste capítulo irão dissertar sobre algumas arquiteturas não convencionais que, através da exploração do paralelismo, tem apresentado alternativas promissoras para o desenvolvimento de sistemas mais poderosos. O próximo capítulo é dedicado aos sistemas com múltiplos processadores. Este grupo tem a vantagem de atingir um grande espectro de aplicações, em virtude do seu baixo custo, aliado à alta disponibilidade do sistema final. Em contrapartida, a demanda de um maior volume de software através de hardware menos eficiente (em relação às outras arquiteturas) vem comprometendo uma utilização comercial mais ampla de tais sistemas.

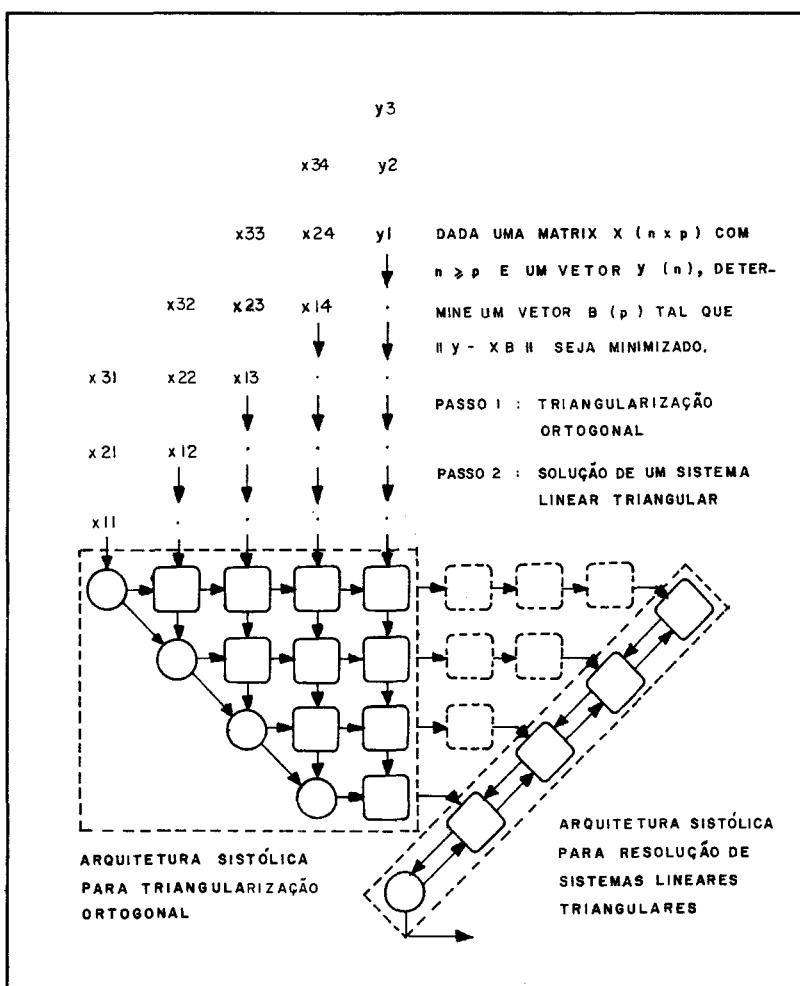

### II.3. ARQUITETURAS SISTÓLICAS

Na produção de uma máquina, devem ser levados em consideração dois tipos de custos: os não recorrentes e os recorrentes. Despesas de projeto, por exemplo, são contabilizadas de uma única vez e diluídas por toda a produção, enquanto que gastos materiais são levados em consideração em cada unidade fabricada.

As principais restrições feitas aos sistemas especiais tem

FIGURA II.7 - UMA CLASSIFICAÇÃO PARA OS COMPUTADORES DIGITAIS.

relação com o seu custo de projeto, em virtude da aplicabilidade limitada inerente a tais equipamentos.

Um dos meios para reduzir estes custos é a criação de uma metodologia que permita uma certa automatização de procedimentos. Uma idéia é decompor a estrutura que se deve projetar num agrupamento de módulos simples não muito diferentes e repetitivos. Para que a idéia seja viável técnica e economicamente é desejável que o acoplamento entre estes módulos seja bastante elementar.

As chances de sucesso nesta área aumentam consideravelmente se forem utilizados projetos em VLSI, onde um "single-chip" pode armazenar centenas de milhares de componentes. Neste nível de complexidade, torna-se imprescindível a utilização de módulos simples e regulares, similares àqueles empregados na construção de sistemas bem estruturados de software (16). Um exemplo bastante interessante desta categoria são as arquiteturas sistólicas, descritas a seguir.

As arquiteturas sistólicas (\*) representam um caso típico de máquinas especiais, que foram originalmente concebidas para implementação em VLSI de operações em matrizes (17). Um sistema sistólico é composto por um conjunto de células interconectadas, cada qual capaz de realizar alguma operação simples. As vantagens registradas no projeto e implementação de estruturas simples e regulares levaram à adoção de topologias sistólicas do tipo matriz ou árvore (Figura II.8).

Nos sistemas sistólicos, a informação flui entre as células de uma maneira análoga ao sangue nas veias do corpo humano. A comunicação com o mundo exterior fica a cargo das células fronteiriças, que injetam informações no sistema de forma pulsante, como um coração.

---

(\*) Sistólica: Adj. relativo a, ou próprio de sístole; 1. Med. Estado de contração das fibras musculares do coração Cf. diástole.

FIGURA II. 8 - SOLUÇÃO PELO MÉTODO DOS MÍNIMOS QUADRADOS UTILIZANDO MATRIZES SISTÓLICAS UNI E BI - DIMENSIONAIS ( $p = 4$ )

As tarefas computacionais podem ser conceitualmente classificadas em "io-bound" ou "compute-bound", de acordo com a quantidade de operações de cada tipo que são realizadas. Por exemplo, o algoritmo de multiplicação de matrizes representa uma tarefa "compute-bound", porque cada elemento da matriz é multiplicado por todos os elementos de alguma linha ou coluna da outra matriz. Por outro lado, a soma de matrizes é "io-bound", já que o número total de somas realizadas não é maior que o número total de elementos das duas matrizes. A partir destas considerações Kung (12) conclui que:

1. Qualquer tentativa para acelerar uma tarefa "io-bound" tem que ser baseada em um aumento da banda passante da memória. Isto pode ser conseguido com o uso de componentes mais rápidos (e caros) ou memórias intercaladas (com uma gerência mais complicada).

2. A aceleração de tarefas "compute-bound" podem, de um modo geral, ser realizadas de uma forma simples e barata através da solução sistólica.

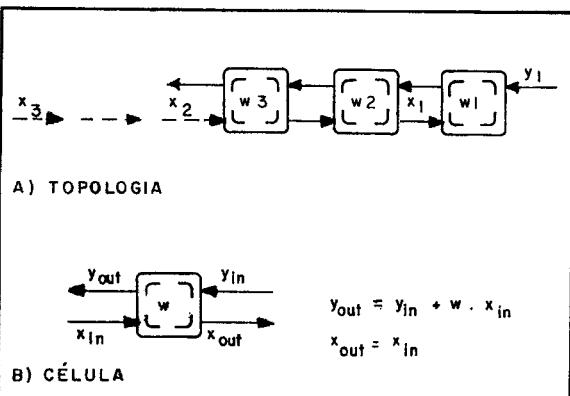

Como exemplos, serão apresentados a seguir alguns exemplos de estruturas sistólicas (12), para resolver o problema da convolução:

Dada a sequência de pesos  $w_1, w_2, \dots, w_k$

e a sequência de entradas  $x_1, x_2, \dots, x_n$

computar a sequência de saídas  $y_1, y_2, \dots, y_{n+1-k}$

definida por  $y_i = w_1 x_i + w_2 x_{i+1} + \dots + w_k x_{i+k-1}$

Este problema é representativo de uma grande classe de computações que podem ser resolvidos via projetos sistólicos. Na essência, trata-se de combinar duas sequências de uma maneira tal que resulte numa sequência de  $y_i$ 's. Rotinas com cálculos semelhantes podem ser encontrados em filtragem, reconhecimento de padrões, correlação, interpolação, avaliação polinomial (incluindo transformadas de Fourier discretas) e multiplicação e divisão de polinômios.

A convolução é um problema "compute-bound" por natureza, dado que cada entrada " $x_i$ " deve ser multiplicada por cada um dos " $k$ " pesos. Se a cada multiplicação precisarmos acessar o " $x_i$ " na memória, certamente haverá um estrangulamento. As ilustrações a seguir serão simplificadas para o caso em que  $k = 3$ .

Matrizes Semi-Sistólicas com Dados Globais: Uma das técnicas para aproveitamento máximo da sequência de  $x_i$ 's é fazer com que cada elemento seja totalmente utilizado em todas as células de uma só vez. Dá-se o nome de "broadcasting" a esta técnica, adotada na arquitetura da Figura II.9. O princípio básico deste projeto foi inicialmente proposto para implementação de um processador de reconhecimento de padrões (18) e em multiplicação de polinômios (19). Notar que a arquitetura é capacitada para armazenamento de informações, o que minimiza o acesso à memória principal.

Matrizes Puramente Sistólicas: Embora o "broadcasting" resolva teoricamente o problema, ele apresenta dificuldades de implementação prática. A transmissão do(s) dado(s) global(is) requer o uso de uma rede que percorra todas as células, o que certamente conduzirá a problemas de expansão e/ou aceleração do sistema. O diagrama da Figura II.10 resolve os três problemas: o da convolução, o de máxima utilização das sequências e o da viabilização prática em larga escala.

Esta estrutura pode ser naturalmente estendida para realizar filtragem recursiva (20,21) e divisão polinomial (22). Outra característica desta matriz sistólica é o tempo de resposta constante, com um valor de " $y_i$ " a cada dois ciclos de tempo. Além destas duas soluções, várias outras são apresentadas por Kung (12).

Os problemas de contenção introduzidos pela excessiva quantidade de acessos à memória nos sistemas convencionais refletem uma inadequação da arquitetura ao problema, de acordo com a discussão introduzida no item II.1.

Em geral os projetos sistólicos podem ser aplicados a qualquer

FIGURA II. 9 -

SOLUÇÃO SISTÓLICA PARA A CONVOLUÇÃO,

ONDE ELEMENTOS  $x_i$ 's SÃO FIXOS E  $y_i$ 's

SE MOVEM SISTOLICAMENTE.

FIGURA II. 10 .

SOLUÇÃO PURAMENTE SISTÓLICA, ONDE OS PESOS  $w_i$  PERMANECEM ESTÁTICOS, ENQUANTO AS SEQUÊNCIAS  $x_i$  E  $y_i$  MOVEM-SE SISTOLICAMENTE, EM SENTIDOS OPOSTOS.

problema "compute-bound" regular, isto é, aquele que realiza computações repetitivas em um grande conjunto de dados. O desenvolvimento de arquiteturas sistólicas irá permitir a ampliação de sistemas especiais, que apresentam rotinas bem delineadas. Mas o objetivo final é aplicar estas técnicas em ambientes genéricos de computação. Para isso são necessários investimentos na integração de componentes para tais sistemas e na criação de blocos programáveis que possam ser flexivelmente configurados em células básicas diferentes.

#### II.4. SISTEMAS DE FLUXO DE DADOS

A idéia de produzir uma máquina baseada em fluxo de dados data da década de 60 (23 a 25), mas só recentemente é que a pesquisa nesta área vem registrando avanços consideráveis. Alguns pesquisadores tem encarado estes computadores como sucessores em potencial das máquinas e linguagens de von Neumann (26).

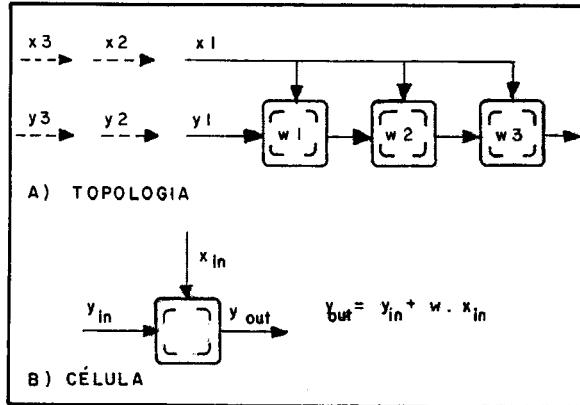

O conceito de fluxo de dados difere do mecanismo de execução sequencial de instruções sendo baseado em dois princípios:

1. Assincronismo: todas as operações são realizadas quando e somente quando seus operandos estiverem disponíveis.

2. Funcionalidade: todas as operações são expressadas através de funções, ou seja, não são considerados os endereços das variáveis mas sim os seus valores.

Esta filosofia reflete um mecanismo que pode ser associado a um grafo direcionado, onde cada nodo representa uma operação a ser realizada.

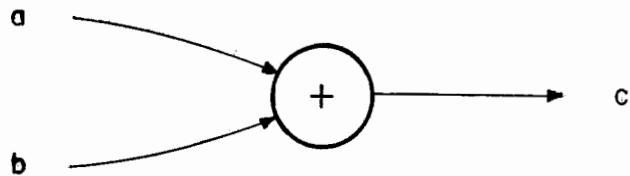

Os arcos "a" e "b" do operador "+" da Figura II.11 transportam os "tokens" de entrada que serão operados (somados no caso) e colocados no arco de saída "c". No caso geral, os dados fluem através do grafo, percorrendo os diversos operadores. O segundo princípio acima citado tem como consequência a eliminação dos efeitos colaterais ("side effects") do sistema, acarretando uma

$$c = a + b$$

FIGURA II. 11 - UM OPERADOR EM "DATA FLOW"

FIGURA II. 12 - REPRESENTAÇÃO DE UMA EXPRESSÃO EM "DATA FLOW".

total liberdade para que quaisquer duas operações sejam executadas concorrentemente.

Não é possível declarar um nodo como executável apenas pela validade do princípio número um, porque os tokens de entrada podem pertencer a diferentes partes da computação. Gajski et al (27) apresentam cinco soluções para este problema. Uma delas consiste em limitar (em um) o número de tokens residentes nos arcos a cada instante. Obtém-se daí uma possível "regra de disparo" do operador, que o torna executável somente quando os tokens de entrada estiverem disponíveis e o de saída desocupado.

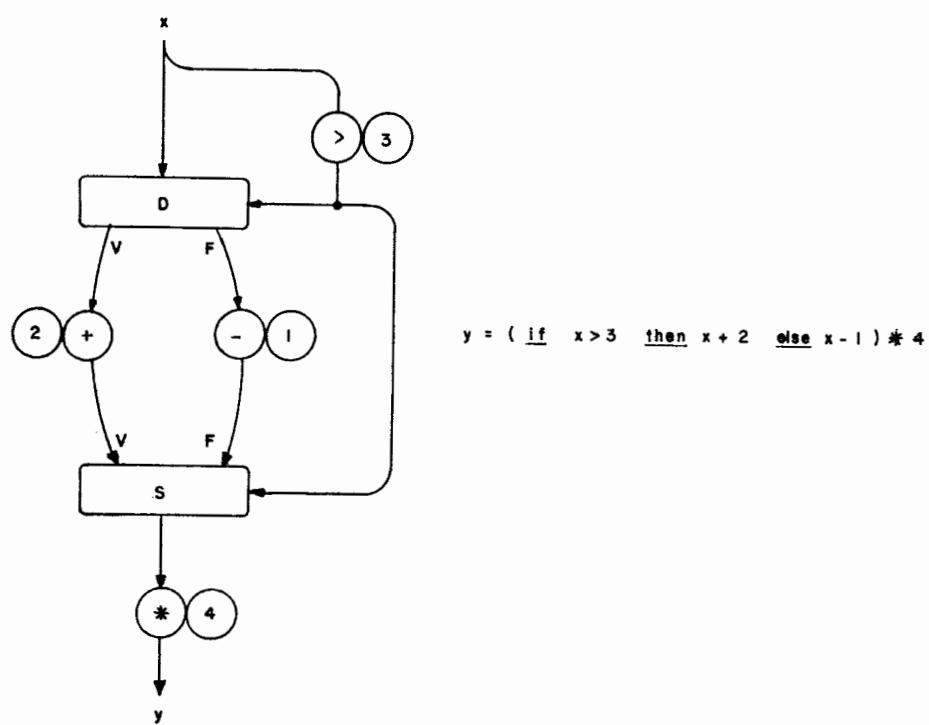

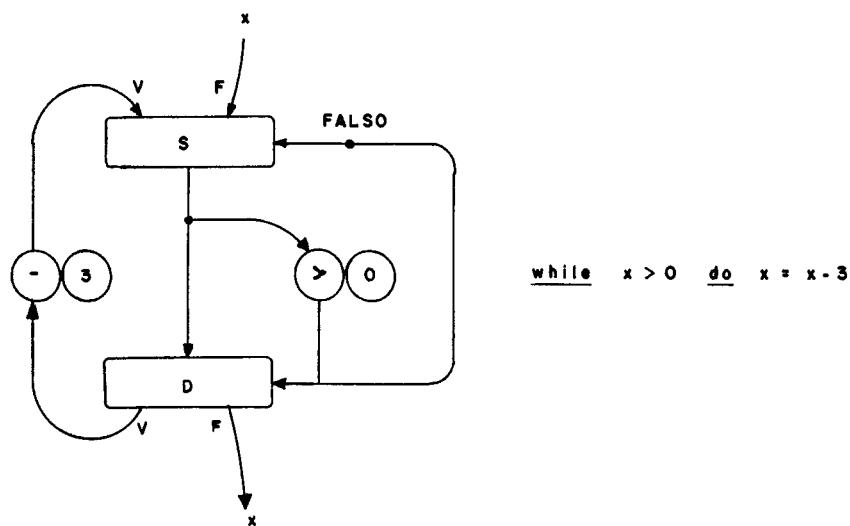

As estruturas para realizar testes de condição e iterações estão ilustradas através de exemplos nas Figuras II.12 e II.13 respectivamente (28). O nodo distribuidor (D) envia o dado de entrada para a saída "V" ou "F" dependendo do estado da entrada booleana de controle. Analogamente, o nodo seletor (S) transfere para a saída uma das duas entradas, de acordo com a porta de controle.

Como se pode observar nos exemplos anteriores, é bastante direta a relação entre os grafos direcionados (29) e a arquitetura de fluxo de dados propriamente dita. Contudo, este não é um meio muito apropriado de programação em virtude da dificuldade de manipulação de diagramas e da alta propensão a erros. Vários pesquisadores tem orientado seus trabalhos para o desenvolvimento de formas de representação de programas que se adaptem bem aos conceitos próprios deste tipo de computação (30). Três classes de linguagem de alto nível tem sido consideradas (27): a primeira é a classe imperativa, que tenta adaptar linguagem como FORTRAN e PL-I para o processamento de fluxo de dados. A segunda é a classe funcional, representada por linguagens que apresentam compatibilidade natural, como o Lisp e o FP que são imunes a efeitos colaterais. A terceira classe é composta por linguagens especialmente projetadas, denominadas linguagens para fluxo de dados. As mais conhecidas são Id, LAU e Val, que reunem características das linguagens imperativas e das linguagens funcionais. Estas características são discutidas por Ackerman (30), e as principais são a semântica funcional - que

FIGURA II. 13 - REPRESENTAÇÃO DE UMA ITERAÇÃO EM "DATA FLOW"

FIGURA II. 14 - MECANISMO BÁSICO PARA EXECUÇÃO DE INSTRUÇÕES NA MÁQUINA DE FLUXO DE DADOS.

permite ao programador abster-se do controle sobre a alocação de memória para código e dados, e o paralelismo implícito - já que o compilador é o responsável pela deteção e criação de caminhos paralelos nos programas.

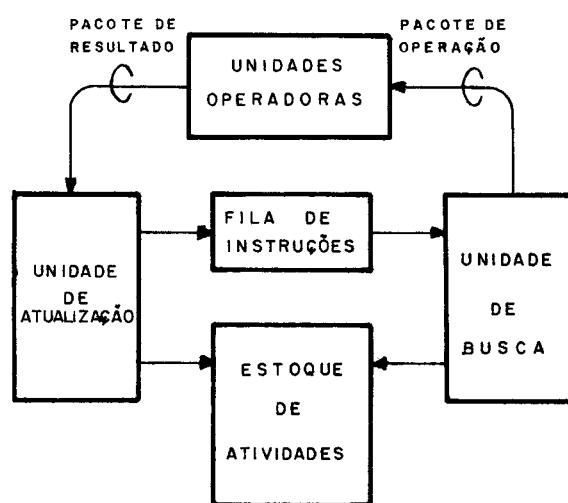

O mecanismo básico para execução de instruções utilizado em diversos projetos de fluxo de dados está representado esquematicamente na Figura II.14 (5). O estoque de atividades é composto por um grupo de elementos que definem o programa que está sendo executado. Cada elemento contém os valores dos argumentos de entrada, a descrição do operador que vai ser utilizado e a definição das outras atividades elementares que deverão receber o resultado da operação. Cada atividade elementar tem um endereço de identificação, que é colocado na fila de instruções quando a "regra de disparo" do operador assim o permitir. A unidade de busca pega o endereço de uma instrução na fila e forma o pacote de operação com os dados lidos na atividade elementar correspondente. Após o término da execução da instrução pelas unidades operadoras é gerado um pacote com os resultados. A partir deste pacote, a unidade de atualização preenche os argumentos nas atividades elementares destino. E também a unidade de atualização que identifica se uma atividade elementar já atendeu a todos os requisitos para ser executada, quando então coloca o seu endereço na fila de instruções. O grau de concorrência em um determinado instante pode ser medido pelo número de entradas da fila de instruções. Este mecanismo é conhecido como pipeline circular.

As principais críticas que são feitas atualmente aos grupos que investigam este assunto estão relacionadas com a falta de compromisso com o real ambiente de computação existente atualmente. A principal razão disto é a orientação "bottom-up" que está sendo dada às pesquisas, visto que somente ao nível de operadores escalares é que foram atingidos objetivos importantes. Outro aspecto que trará dificuldade à implantação deste tipo de processamento é o conservadorismo que tende a existir nos meios computacionais. Grande esforço está sendo feito hoje em dia para padronização e aumento da produtividade do elemento humano, o que parece conflitar com as ferramentas

até agora desenvolvidas para fluxo de dados.

### II.5. PROCESSAMENTO "PIPELINE"

Há bastante controvérsia na literatura sobre a classificação deste tipo de arquitetura. Flynn considerou o processador "pipeline" como um dos três tipos básicos de máquinas SIMD (9), no mesmo artigo em que introduziu tal classificação para as arquiteturas de computadores. Outras interpretações contudo citam tal arranjo como pertencente à categoria MISD (5 e 31). No escopo deste trabalho estas arquiteturas não serão posicionadas em nenhum grupo específico. Em vez disso, as técnicas de "pipelining" serão consideradas como uma filosofia de projeto, visando a obtenção de um maior aproveitamento dos componentes de hardware. Esta decisão é baseada na constatação de que esta "filosofia" é utilizada de forma bastante diversificada em aplicações que variam desde supercomputadores até unidades periféricas inteligentes, ou até mesmo na arquitetura interna de alguns microprocessadores.

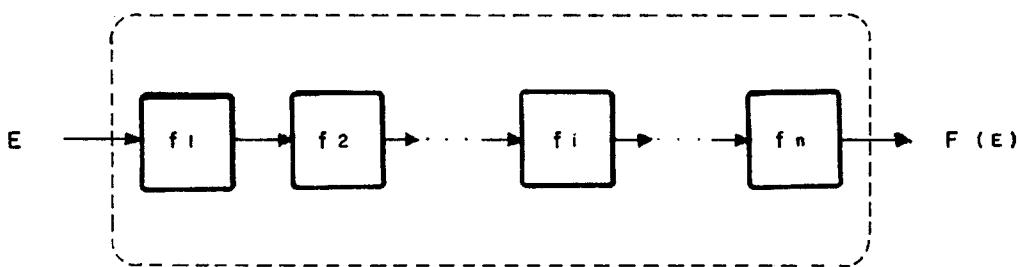

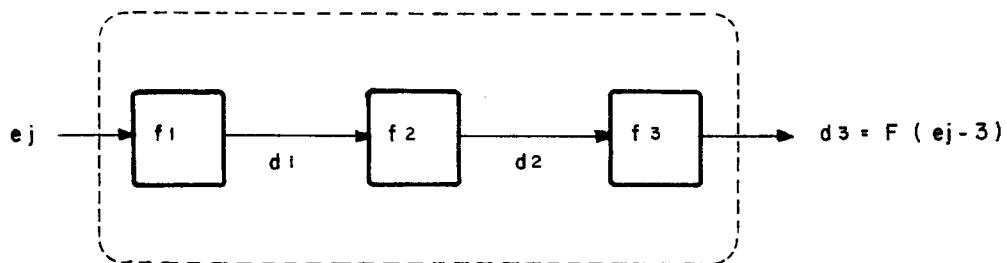

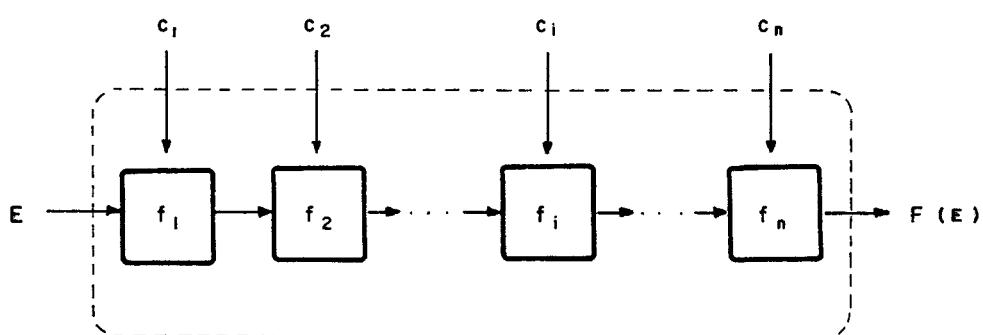

Uma estrutura "pipeline" é caracterizada pela organização em série de seus elementos. Cada um deles é incumbido de operar de forma independente o dado que recebe e de transmitir o resultado para o elemento seguinte. A Figura II.15 apresenta esquematicamente uma solução para processar uma determinada função  $F$ . A subdivisão em sucessivas sub-funções  $f_i$  transforma a função original em:

$$F(E) = f_n(f_{n-1}(\dots f_i(\dots f_2(f_1(E))\dots)\dots))$$

O tempo total de execução da função  $F$  é igual à soma dos tempos gastos por cada  $f_i$ . Este valor permite definir o fator de latência ( $L$ ) da estrutura, medido em unidades de tempo  $\Delta t$ . A performance do sistema ao ser alimentado por uma entrada  $E$  é medida pela quantidade de dados processados por unidade de tempo:

FIGURA II. 15 - ESTRUTURA "PIPELINE", ONDE CADA ELEMENTO REALIZA UMA FUNÇÃO  $f_i$  SOBRE O DADO QUE RECEBE, TRANSMITINDO O RESULTADO AO ELEMENTO SEGUINTE.

$$d_1 = f_1(e_j - 1)$$

$$d_2 = f_2(f_1(e_j - 2))$$

$$d_3 = f_3(f_2(f_1(e_j - 3))) = F(e_j - 3)$$

FIGURA II. 16 - SISTEMA "PIPELINE" ALIMENTADO POR UMA SEQÜÊNCIA DE ENTRADAS  $e_j$ .

$$\text{Perf} = \frac{1}{L\Delta t}$$

Admitindo-se agora que a entrada E é composta por uma sequência definida por:

$$E = e_1, e_2, \dots, e_j, \dots$$

e que as funções  $f_i$  são independentes, pode-se alimentar o sistema com a entrada  $e_2$  assim que  $f_1$  terminar o tratamento de  $e_1$ . A aplicação sucessiva deste procedimento resultará no preenchimento da série de  $f_i$ 's, ficando cada elemento responsável pela geração de um dado  $d_i$ . A Figura II.16 representa tal situação para três elementos.

Observar que, se for mantido um fluxo de entrada constante, o sistema poderá teoricamente responder com uma saída para cada entrada injetada. A performance final foi aumentada  $n$  vezes, apesar do período de latência para tratamento de uma entrada ter continuado o mesmo.

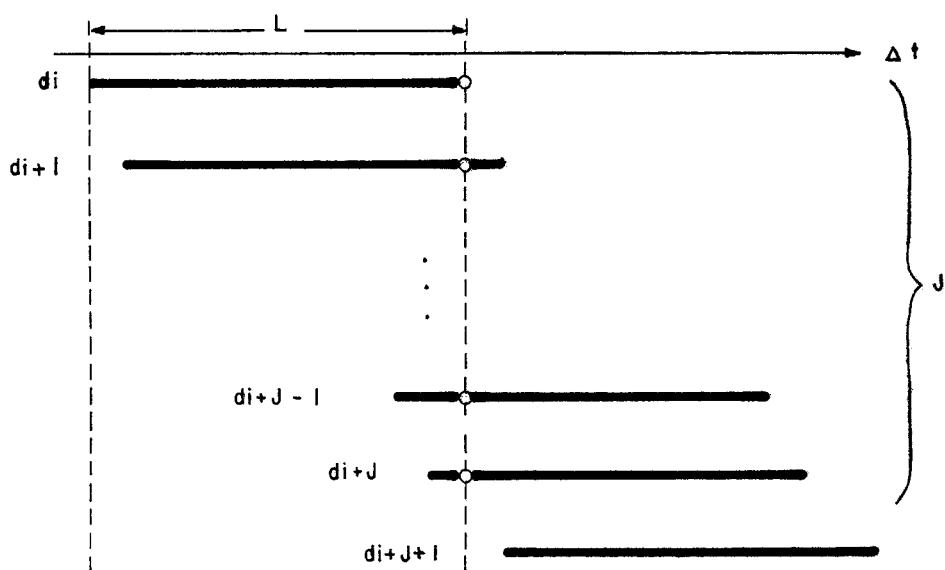

De uma forma mais geral, é definido o fator de inércia do sistema como sendo o número de dados que estão sendo processados durante o tempo de latência para tratamento de uma entrada. A Figura II.17 ilustra este caso.

Consequentemente a expressão da performance máxima alcançada pelo sistema pipeline é dada por:

$$\text{Perfmax} = \frac{J}{L\Delta t}$$

Entretanto, a performance máxima do sistema só é obtida no caso em que a "linha de produção" está completamente cheia, ou seja, todos os operadores contém dados nas suas entradas. No caso real é necessário considerar dois fatores que contribuem para o seu esvaziamento. O primeiro está relacionado com a dificuldade de programar as sequências E de entrada de forma a manter um fluxo constante de dados. Esta preocupação tem levado os projetistas a

FIGURA II. 17 - O FATOR DE INÉRCIA  $J$  REPRESENTA O NÚMERO DE DADOS QUE ESTÃO SENDO OPERADOS DURANTE O TEMPO DE LATÊNCIA  $L$   $\Delta t$ .

FIGURA II. 18 - SISTEMA "PIPELINE" COM ENTRADAS EXTERNAS  $c_i$ .

desevolver ferramentas de software especiais que permitam arrumar o programa de forma a extrair o máximo possível de paralelismo das aplicações. Dá-se o nome de "vetorização" a essa técnica.

Outro fator que pode causar retardo na sequência de processamento normal do sistema está relacionado à disponibilidade de dados externos. Para exemplificar, considere um sistema "pipeline" como o da Figura II.18. Neste sistema, a função de cada elemento não depende somente do dado de entrada  $d_i$ , mas também de um outro dado externo  $c_i$ . É óbvio que qualquer retardo introduzido pela ausência dos dados externos irá se refletir na performance final do sistema. Flynn (9) analisa a situação em que o dado  $c_i$  é dependente das próprias funções da estrutura, ou seja:

$$c_i = h(d_1, d_2, \dots, d_j, \dots, d_{i-1})$$

onde cada  $d_j$  representa o dado gerado pelo elemento  $j$  da linha de "pipes".

Outras características interessantes dos sistemas pipeline surgem quando o custo é levado em consideração. Sterling (5) demonstra para um caso simples que é grande o custo adicional de adaptação para processamento pipeline. Em alguns casos, apesar do ganho em performance há significativa perda na relação performance/custo. Na mesma referência é investigada também a redução da eficiência causada pelos incrementos de hardware que são necessários para garantir o perfeito funcionamento do sistema "pipeline".

Os problemas de perda de eficiência em sistemas que utilizam processamento "pipeline" podem ser observados através de medidas de performance, em exemplos reais de aplicação. O estudo de Bucy, citado em (32), escolheu um problema de filtragem não linear que requeria aproximadamente 83000 operações em ponto flutuante para cada iteração. Este problema foi resolvido em vários sistemas diferentes e a Tabela II.2 mostra a grande diferença entre as velocidades máximas teóricas e as velocidades

| NOME       | TIPO                    | VELOCIDADE ( M. FLOPS ) |          | CUSTO APROXIMADO<br>( US DOLAR / FLOP ) |                  |

|------------|-------------------------|-------------------------|----------|-----------------------------------------|------------------|

|            |                         | MÁXIMA TEÓRICA          | ABSOLUTA | REAL                                    | RELATIVA AO MAX. |

| CRAY - I   | SUPERCOMPUTADOR         | 140                     | 38.4     | 27 %                                    | 0.21             |

| STAR - 100 | SUPERCOMPUTADOR         | 50                      | 16.8     | 34 %                                    | 0.48             |

| AP - 120 B | PROCESSADOR DE MATRIZES | 12                      | 5.9      | 49 %                                    | 0.03             |

TABELA II - 2 - ALGUNS DADOS DO ESTUDO DE BUCY SOBRE A PERFORMANCE DE SISTEMAS QUE UTILIZAM PROCESSAMENTO PIPELINE .

médias reais alcançadas por estas máquinas. A medida de velocidade utilizada é o Megaflop (mflop), que é equivalente a um milhão de operações em ponto flutuante por segundo.

## II.6. PROCESSAMENTO ASSOCIATIVO

Os primeiros estudos envolvendo o conceito de processamento associativo datam da década de 50 (33), embora só há dez anos tenham sido registradas realizações práticas significativas de tais arquiteturas (34). A motivação para o desenvolvimento desta área partiu da constatação de que as soluções para processamento de uma certa classe de problemas demandavam excessivo tempo de execução nas máquinas convencionais. Não se tratava apenas de um simples aumento de velocidade, mas sim de uma utilização mais racional das potencialidades disponíveis.

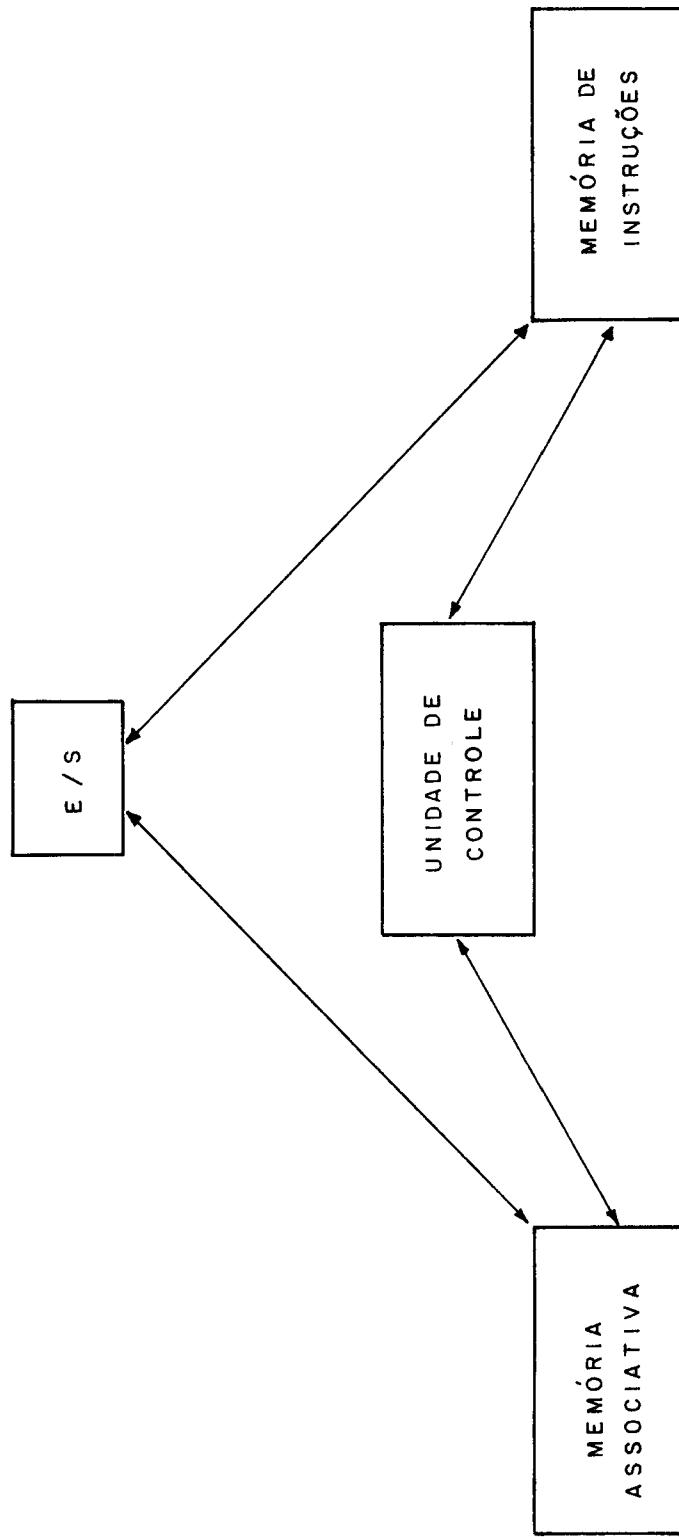

Um computador associativo típico, representado esquematicamente na Figura II.19 comprehende: uma memória associativa para armazenar os dados; uma unidade de controle para coordenar a execução dos programas; uma memória de instruções e unidades de E/S.

A memória associativa é um dispositivo armazenador de informações organizado por células, que são acessadas por intermédio de seu conteúdo. Além disso, as células da memória associativa são capazes de realizar o processamento nos dados localmente, eliminando assim a necessidade de transferências para alguma unidade central. A consequência disso é a fusão das atribuições da memória e da unidade aritmética e lógica em um único módulo. Uma outra característica dos processadores associativos é a separação física da memória em duas partes: código e dados.

De acordo com a sua organização, podemos classificar um dispositivo associativo em quatro categorias: totalmente paralelo, bit-série, palavra-série e orientado por blocos.

Os dispositivos totalmente paralelos podem por sua vez serem

FIGURA II. 19 - ESTRUTURA DE UM COMPUTADOR ASSOCIATIVO TÍPICO.

divididos em sistemas organizados por palavra e com lógica distribuída. Nos sistemas totalmente paralelos organizados por palavra as operações são utilizadas simultaneamente em todas as palavras da memória. Este grupo representa o processador associativo ideal no que diz respeito à velocidade e versatilidade. Porém a grande quantidade de circuitos necessários à esta arquitetura não incentiva muito a sua implantação. O segundo grupo de processadores associativos puramente paralelos é o de lógica distribuída. Esta organização é bastante eficiente na manipulação de dados de tamanho variável. A memória de lógica distribuída é composta por células estanques de armazenamento, onde a comunicação é feita entre duas células vizinhas e a unidade de controle. Um processador associativo deste tipo foi desenvolvido pelo "Bell Laboratories" para a "U.S.Army Advanced Ballistic Missile Defense Agency", sendo batizado de "Parallel Processing Ensemble" (PEPE) (35). PEPE era usado em conjunto com um computador sequencial de alta velocidade.

A categoria de dispositivos associativos bit-série representam um compromisso entre os aspectos funcionais dos sistemas totalmente paralelos e os custos envolvidos na implementação de tais dispositivos. Em vez de dedicar inteligência a cada célula (bit) da memória, é reservada uma única unidade lógica para cada palavra. Assim sendo, somente um bit de cada palavra é processado simultaneamente em toda a memória. A desvantagem desta solução é o retardo introduzido no processamento igual à quantidade de bits por palavra de memória. Porém, além da grande redução ainda registrada no tempo total de processamento, há a vantagem de uma substancial economia de hardware em relação aos sistemas totalmente paralelos. Um modelo deste grupo é o sistema STARAN (36) fabricado pela Goodyear Aerospace Corp..

Os computadores que processam as palavras serialmente não utilizam memórias endereçadas por conteúdo, não podendo ser rigorosamente considerados como dispositivos associativos. O que diferencia estas máquinas dos computadores convencionais é o hardware especial que controla o processamento durante a varredura de um trecho da memória sequencial. A utilização de

uma única instrução para realizar este processamento economiza ao computador o tempo de "fetch" repetitivo de instruções. Operações deste tipo são suportadas por diversos computadores atualmente, como o VAX 11/780 e o microprocessador INTEL 8086.

Para aplicações que requeriam uma grande capacidade de armazenamento, as soluções associativas até agora apresentadas não são viáveis. Os sistemas bit-série tornam-se muito caros e os sistemas palavra-série resultam num tempo de processamento excessivo. Algumas tentativas para estender o conceito de associatividade às memórias de massa (37 e 38), procuraram tirar vantagem dos discos de cabeça fixa de alta performance. As propostas sugerem a associação de tais equipamentos a uma lógica externa, que tenha capacidade de manipular os dados à medida que eles passem sob a cabeça de leitura.

A programação dos dispositivos associativos é quase toda feita em baixo nível, quer seja em linguagem de máquina ou microcódigo. O sistema STARAN, por exemplo, utiliza um montador simbólico (APPLE - "Associative Processor Programming Language"), que sofre adaptações especiais em cada ambiente que é instalado. Uma outra alternativa, que permite o desenvolvimento de programas através de linguagens de alto nível é a inclusão de construtos específicos para processamento associativo em linguagens já existentes. Convém ressaltar que há normalmente uma dificuldade natural com a programação de máquinas associativas, em virtude das diferenças conceituais inerentes aos sistemas SIMD.

As aplicações mais adequadas ao processamento associativo são aquelas que apresentam uma ou mais das seguintes propriedades (39): busca rápida em grandes bancos de dados; realização de operações aritméticas e lógicas em grandes conjuntos de dados ou manipulação de bancos de dados que sofram alterações dinâmicas.

Estas aplicações incluem soluções para problemas de processamento de sinais, armazenamento e recuperação de informações, suporte para sistemas de computadores além de aplicações numéricas tais como otimização de funções, solução de

equações diferenciais, operações com matrizes, manipulação de grafos, etc..

A primeira experiência prática com um sistema associativo real de proporções significativas (34) foi dedicada ao processamento de sinais de radar. A Administração Federal da Aviação dos Estados Unidos (FAA) utilizou-se de um sistema para controle de tráfego aéreo, baseado na máquina associativa de Knoxville para monitorar aeronaves, isolando as que estivessem em rotas de colisão ou situações potencialmente perigosas. A performance alcançada por tal sistema excedeu em duzentas vezes o tempo de resposta das máquinas convencionais da época. O sistema STARAN, já citado, foi construído a partir desta experiência.

Nos sistemas de gerenciamento de bancos de dados o formato, estrutura e quantidade de informações variam durante o tempo de vida útil do sistema, o que torna adequada a sua implementação através de dispositivos associativos (40). Apesar das dificuldades de construção prática de uma grande memória endereçada por conteúdo, prosseguem as investigações visando o desenvolvimento de memórias de massa associativas (37 e 38). Além disso, há trabalhos orientados para processamento "on-line" e compressão/descompressão de dados (41).

Algumas funções de controle presentes nos computadores podem se beneficiar dos dispositivos associativos. É o caso por exemplo de pequenas unidades auxiliares destinadas a controlar a alocação de memória virtual em grandes computadores (42). Os dispositivos associativos são também considerados potencialmente úteis pelos grupos interessados em processamento de linguagens.

Os processadores associativos são propostos como sendo sistemas computacionais bastante flexíveis para processamento de informações não-numéricas. Tais sistemas podem manter uma alta eficiência de hardware, na maioria dos casos, sem que isto incorra em um software complexo (41). São ainda necessárias pesquisas principalmente na área de arquitetura, para avaliar o potencial das diversas organizações e prover adaptações às técnicas de VLSI. Na área de software é preciso que haja

desenvolvimento de novos algoritmos para suportar as estruturas de dados mais comuns (árvores, listas, pilhas, etc.), de linguagem de alto nível adequadas e de ferramentas de suporte.

Por outro lado, a grande confiança depositada atualmente nas linhas mais conservadoras de projetos de hardware e software, aliada à possibilidade de simulação das máquinas associativas em ambientes convencionais, justifica em parte, a baixa prioridade dada atualmente ao desenvolvimento de computadores associativos comerciais.

## II.7. "ARRAY PROCESSORS"

As aplicações que envolvem processamento científico, exigem alguns requisitos especiais de um sistema computacional. Alta performance em cálculos repetitivos, manipulação de grandes conjuntos de dados, boa precisão em cálculos sucessivos, representação de valores em um largo espectro numérico e um razoável conforto para programação são exemplos de características importantes. De uma forma geral, os algoritmos para cálculo científico consistem de longas sequências de somas, multiplicações, multiplicações-somas, etc., envolvendo números reais e complexos. A viabilização destas aplicações está veiculada a um tratamento eficiente destas sequências, principalmente nos casos de processamento em tempo real.

A utilização de computadores de uso geral em aplicações científicas de grande porte, tem normalmente conduzido a uma alta relação custo/performance no resultado final. Se por um lado os requisitos de velocidade são satisfeitos com o emprego de supercomputadores, os custos envolvidos podem tornar esta solução proibitiva. Além disso, outros aspectos como o tamanho físico e a potência consumida precisam ser levados também em consideração. Por outro lado, os sistemas de menor porte, apesar do seu baixo custo, não apresentam um rendimento satisfatório para uma grande quantidade de aplicações científicas.

As restrições citadas, envolvendo computadores de uso geral,

foram responsáveis pelo aparecimento de máquinas mais velozes, destinadas a executar operações científicas específicas. Os "array processors" representam uma parcela significativa deste conjunto. Este termo tem sido ambigamente citado na literatura (43) para referenciar dois tipos de arquitetura que serão tratadas separadamente neste trabalho.

O primeiro tipo, aqui denominado processador em matriz diz respeito a um computador composto por vários elementos processadores, que podem estar eventualmente dispostos segundo uma topologia matricial. Estes elementos normalmente têm capacidade para realizar operações simultâneas nos dados que manipula, oferecendo soluções bastante poderosas, ainda que o custo relativamente alto. Os processadores em matriz se enquadram rigorosamente na categoria de máquinas SIMD, já que as instruções afetam simultaneamente todos os elementos processadores de uma mesma maneira. O sistema ILLIAC IV, por exemplo, é uma das mais famosas máquinas deste tipo, tendo sido concebida pela Universidade de Illinois para suportar 256 elementos processadores, divididos em quatro quadrantes. Apesar das operações multi-quadrantes não terem sido implementadas, foi construída uma versão com 64 elementos processadores, controlados por uma unidade central que dispunha de memórias independentes para instruções e dados. O objetivo inicial deste projeto estava voltado para processamento de matrizes, mas havia a possibilidade de se programar o ILLIAC IV para funcionar como uma máquina associativa de 64 elementos.

Um segundo tipo de arquitetura, emprega o termo "array processor" para indicar os tipos de dados que vão ser manipulados. Estes equipamentos (44), doravante batizados de processadores periféricos de matrizes, costumam operar em conjunto com um sistema principal (normalmente um minicomputador) realizando de maneira eficiente operações em dados do tipo matriz. Um exemplo de processador periférico de matrizes bastante conhecido comercialmente é o AP-120B, fabricado pela Floating Point Systems (45).

Os processadores periféricos representam atualmente uma

ferramenta bastante eficiente para acelerar o processamento de aplicações científicas "compute-bound". O baixo custo e o alto grau de maturação alcançado pelo hardware e software dos equipamentos existentes refletem uma experiência acumulada pelos fabricantes e usuários deste tipo de máquina, desde a época que sucedeu a Segunda Guerra Mundial. Uma amostra do potencial deste tipo de ferramenta pode ser observada na Tabela II.3, onde o AP-120B se destaca por seu baixo custo relativo.

O projeto de um processador periférico de matrizes é orientado para o acoplamento a um computador hospedeiro, com a intenção de aumentar a performance do mesmo em tarefas computacionais específicas. A composição interna de um equipamento destes, normalmente inclui várias unidades aritméticas independentes, empregadas na realização de somas, multiplicações, etc.. Uma alta performance é usualmente alcançada através da exploração de paralelismo e/ou "pipelining" na estrutura.

Nos processadores periféricos de matrizes, além da separação dos meios de armazenamento de instruções e dados, verifica-se a existência de memórias para cada tipo de dado. As palavras de instrução, que são praticamente um microcódigo da máquina, são normalmente mais largas que as palavras de dados. As diversas combinações de operações, visando uma máxima utilização das diversas unidades aritméticas tornam vantajosa a criação de memórias de dados independentes. Resumindo, a diferença de tamanho das palavras, combinada com a necessidade de haver paralelismo no acesso às informações, conduz normalmente à separação das memórias internas dos processadores periféricos de matrizes, de acordo com a sua aplicação.

O desenvolvimento de sistemas digitais de computação baseados em processamento periférico é bastante explorado por duas grandes linhas de investigação (46): o processamento matemático de vetores, voltado principalmente para a resolução de equações diferenciais parciais e o processamento digital de sinais (47), que manipula com dados serializados no tempo.

A primeira linha de pesquisa é fundamental na análise de

| MÁQUINA        | VELOCIDADE MÁXIMA TEÓRICA (M FLOPS) | CUSTO DA INSTALAÇÃO (US \$ x 10 <sup>6</sup> ) | CUSTO RELATIVO (\$ / FLOP) |

|----------------|-------------------------------------|------------------------------------------------|----------------------------|

| CRAY - I       | 140                                 | 8                                              | 4.6                        |

| STAR - 100     | 50                                  | 8                                              | 12.8                       |

| ILLIAC IV      | 80                                  | 10                                             | 10.0                       |

| CDC 7600       | 15                                  | 3                                              | 16.0                       |

| AP - 120 B     | 12                                  | 0.15                                           | 1.0                        |

| IBM 370 - 168  | 4                                   | 2                                              | 40.0                       |

| CDC 6600       | 3                                   | 1                                              | 26.7                       |

| VAX - 11 / 780 | 0.5                                 | 0.20                                           | 32.0                       |

| PDP - 11 / 70  | 0.2                                 | 0.15                                           | 60.0                       |

TABELA II.3 - TABELA DE COMPARAÇÃO ENTRE COMPUTADORES DE USO GERAL E "ARRAY PROCESSORS".

sistemas físicos associados a diversas áreas como meteorologia, hidrodinâmica, fissão nuclear, transferência de massa e calor, poluição do ar e da água, etc.. A utilização de computadores digitais para solução destes problemas requer uma discretização dos pontos continuamente distribuídos no domínio espaço-tempo. Quanto maior o número de pontos levados em consideração, menores são as possibilidades de erros na solução final.

As séries temporais de dados, resultantes da digitalização de informações analógicas criaram uma nova classe de problemas, que estimularam o desenvolvimento de processadores periféricos de matrizes. Em aplicações tais como radar, sonar, prospecção geofísica de petróleo, processamento de imagem, etc., são aquisitados e tratados valores analógicos de tensão, corrente, intensidade de luz, deslocamento, etc.. Estas variáveis são amostradas sincronamente e convertidas para um formato digital adequado ao seu processamento e armazenamento. O processamento - que pode englobar filtragem, correlação, análise espectral, etc. - deve em grande parte dos casos ser executado em tempo real. Consequentemente, o desempenho computacional requerido excede a capacidade dos computadores sequenciais mais comuns. Tipicamente, os processadores periféricos de matrizes são bastante eficientes na realização das operações normalmente utilizadas em processamento de sinais.

As ferramentas de programação empregadas nos processadores periféricos de matrizes são, na maioria, de baixo nível, sendo bastante comum a utilização de microprogramação. A razão disso é a necessidade de alcançar a máxima eficiência no processamento predominantemente paralelo. Ainda não há um meio de representação simbólica, quer seja com linguagens de alto nível ou código "assembly"-equivalente, que permita um controle eficiente e preciso das potencialidades suportadas pelas arquiteturas. Sendo assim, a (micro) programação destas máquinas torna-se tarefa bastante árdua, já que o usuário precisa entender os mecanismos de transferência simultânea de dados através dos caminhos paralelos. Além disso, é preciso que sejam considerados na execução de cada operação os retardos relativos introduzidos por cada módulo. Em virtude das limitações naturais

já citadas (ver Seção II.5), a eficiência alcançada pelos processadores periféricos de matrizes é baixa para os casos não triviais, sendo considerado excelente valores acima de cinquenta por cento da velocidade máxima teórica.

Os usuários podem escapar do "fantasma" da microprogramação empregando bibliotecas matemáticas fornecidas pelos fabricantes. Estas unidades de microcódigo, compostas por até algumas centenas de instruções otimizadas, podem ser introduzidas no programa de aplicação por meio de chamadas de alto nível.

### III. ARQUITETURAS MIMD UTILIZANDO MICROPROCESSADORES

As arquiteturas MIMD são caracterizadas pela presença de duas ou mais unidades processadoras destinadas a realizar operações múltiplas em conjuntos distintos de dados. Embora sob o ponto de vista técnico não exista nenhuma restrição quanto ao porte destas unidades, será dada maior ênfase às estruturas MIMD compostas por microprocessadores. Esta escolha reflete a tendência atual em agregar componentes VLSI com o objetivo de obter arquiteturas mais poderosas. Esta perspectiva vem se tornando mais promissora após o lançamento de microprocessadores com performance comparável à máquinas de médio porte (48).

Embora os componentes VLSI estejam ocupando uma ampla faixa no espectro de aplicações de sistemas digitais, resta saber se estes componentes poderão ser agrupados para construir grandes sistemas genéricos de computação. Em outras palavras, caberia aqui uma pergunta: pode um determinado conjunto de microprocessadores ser interconectado para executar tarefas que necessitam de uma velocidade global de ordem de vários milhões de instruções por segundo? Atualmente não há uma resposta definitiva para esta pergunta, embora existam diversas razões para acreditar que grandes sistemas a multimicroprocessadores sejam viáveis a médio prazo. Estes argumentos já foram bastante discutidos na literatura em geral, e estão ligados à capacidade de realização de sistemas com boas características de performance/custo, disponibilidade, modularidade, flexibilidade, etc..

Uma diferença em performance de aproximadamente duas ordens de grandeza separa atualmente os microprocessadores das máquinas de grande porte empregadas em processamento numérico pesado. A seguir são apresentados os principais problemas que os projetistas estão enfrentando para tentar reduzir esta diferença (49).

- Decomposição de tarefas: Como dividir as tarefas entre os processadores? A decomposição deve ser automática (através de

compiladores ou rotinas chamadas em tempo de execução) ou deve ser deixada para o programador?

- Interferência: Após a decomposição das tarefas entre os diversos processadores, quais as técnicas a serem empregadas para minimizar a contenção pelos recursos de memória e E/S?

- Estruturas de interconexão: Quais são os tipos mais eficientes de conexão entre processador/memória e processador/processador? Quais os protocolos que devem ser associados a cada caso?

- Estrutura de software: Que estruturas são mais adequadas para sistemas com dezenas ou centenas de processadores? Problemas importantes nesta área são gerenciamento de recursos, distribuição de software, proteção e confiabilidade.

- Mecanismo de mapeamento de endereços: Que mecanismos são apropriados para efetuar a conversão de endereços virtuais para reais? Estes mecanismos devem permitir o compartilhamento de código e dado ao mesmo tempo em que devem garantir níveis adequados de proteção e eficiência.

- Prevenção de retardos infinitos ("deadlocks"): A disputa pelos recursos dá margem a uma situação perigosa em que todos os processadores ou uma parte deles estejam impedidos de executar, por estarem esperando a liberação de um recurso que não irá ocorrer. Esta situação deve ser evitada.

- Tolerância a falhas: Quais as estruturas de hardware e software que tirarão o máximo proveito da capacidade de recuperação inerente às estruturas com múltiplos processadores?

- Entrada e saída: Como os dispositivos de entrada e saída, especialmente memórias de massa, devem ser integrados a um sistema a multi-microprocessadores?

A investigação destas e de outras questões (50) deve ser

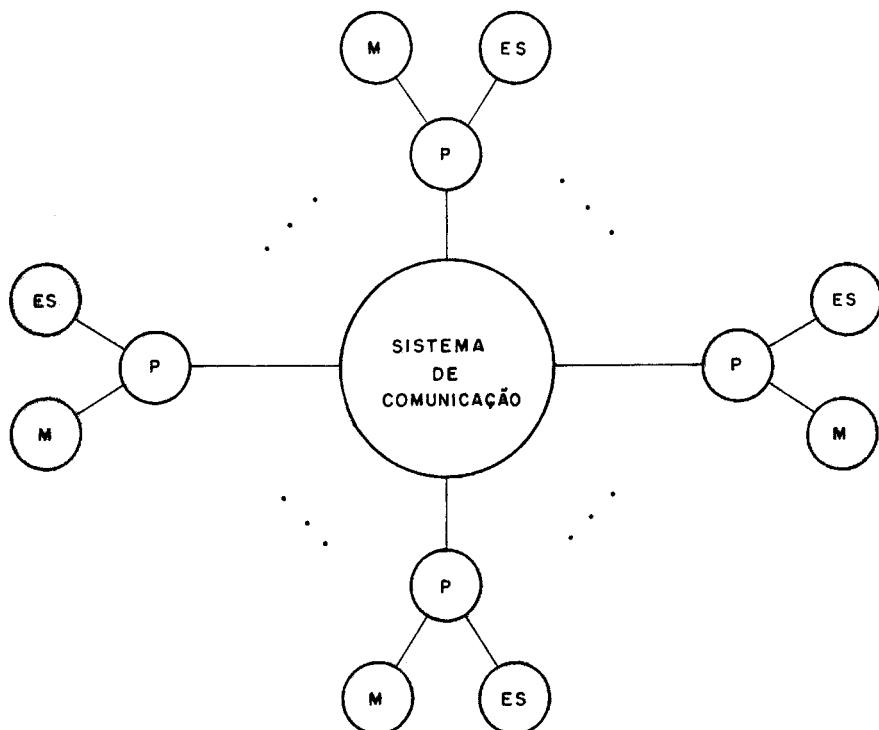

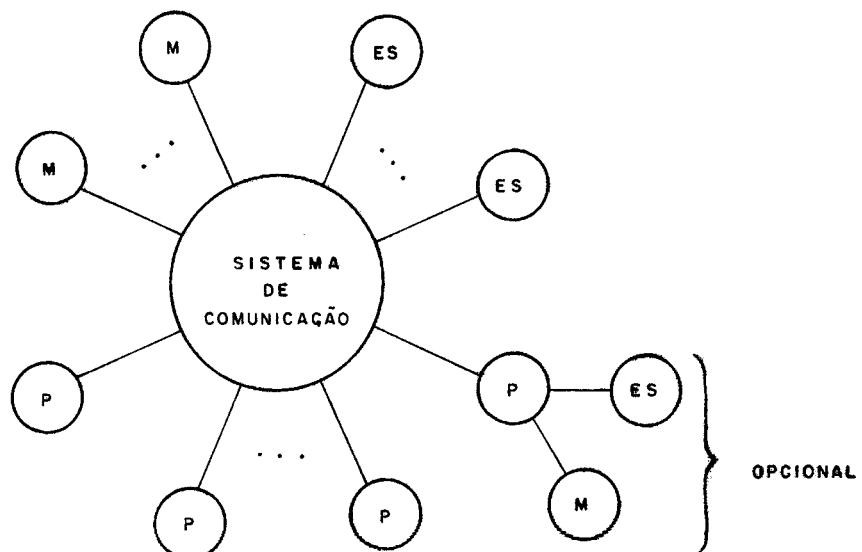

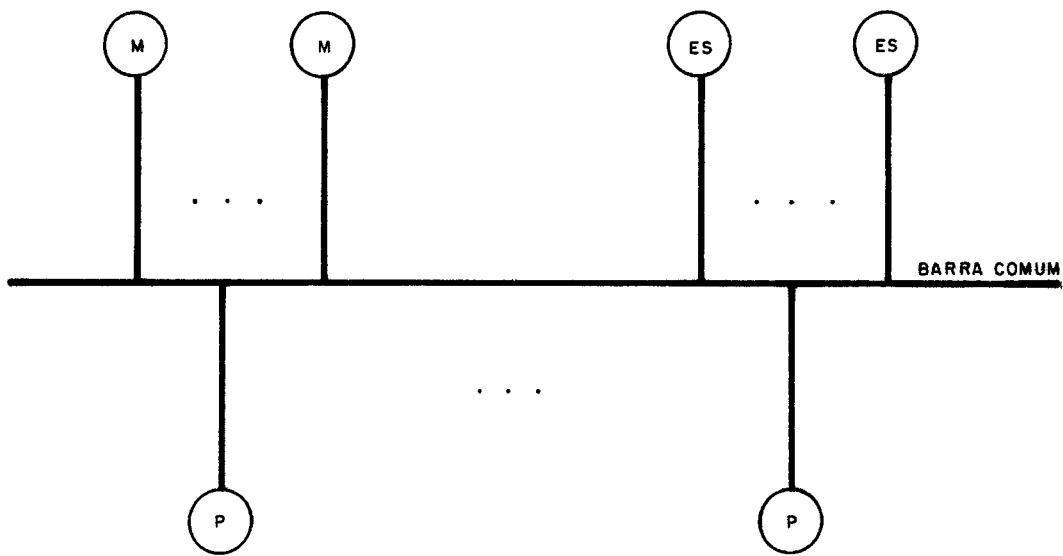

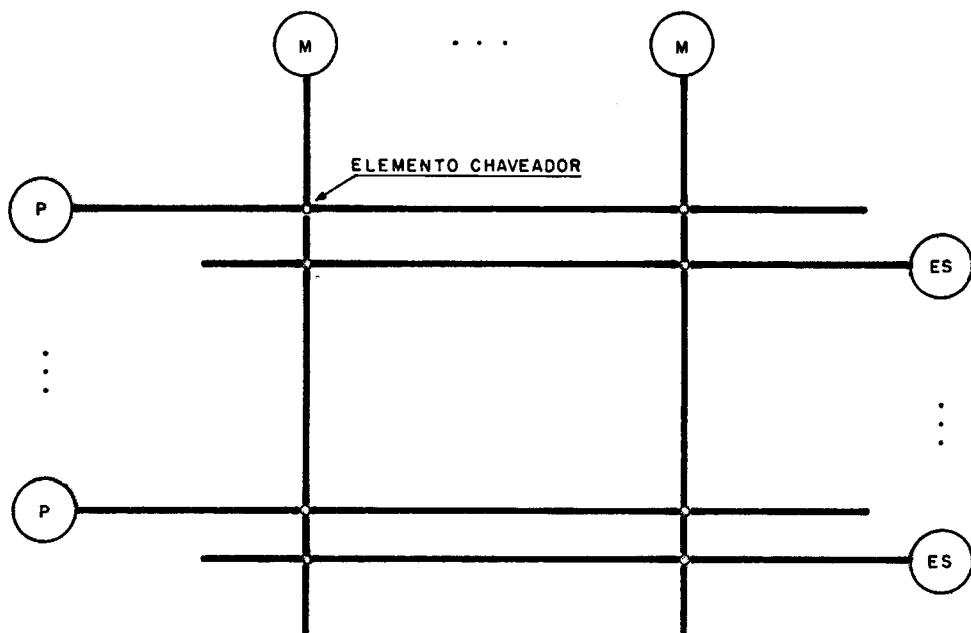

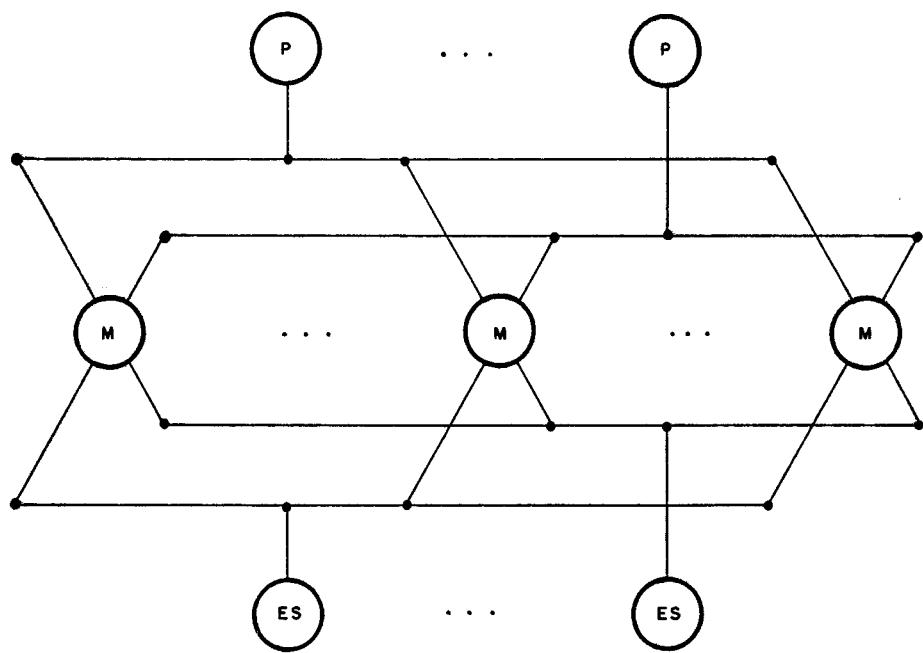

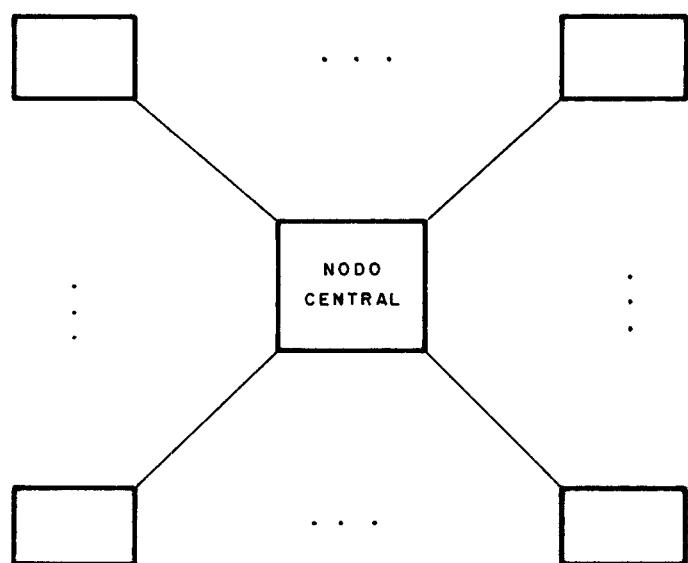

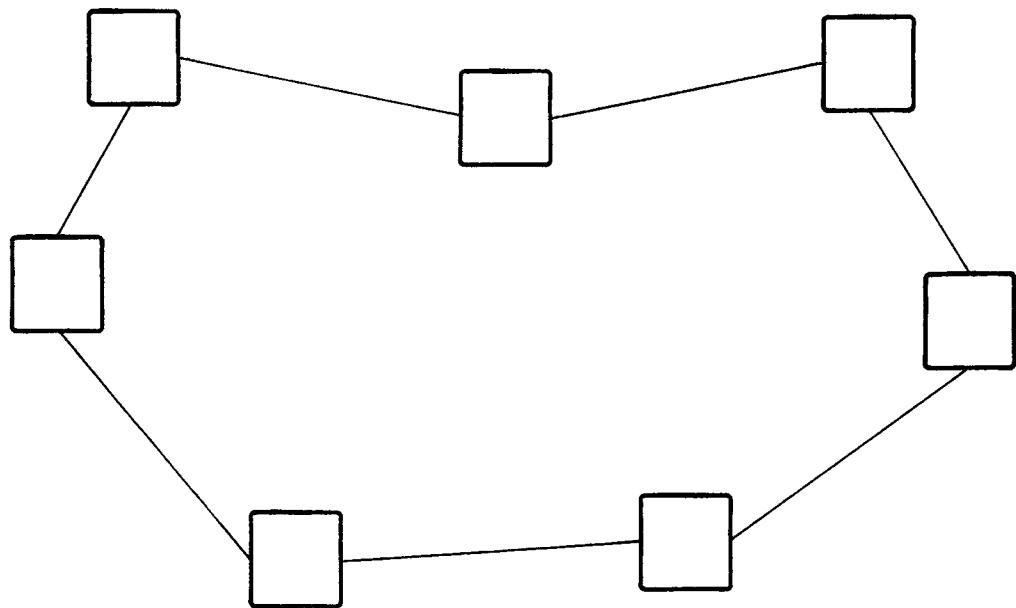

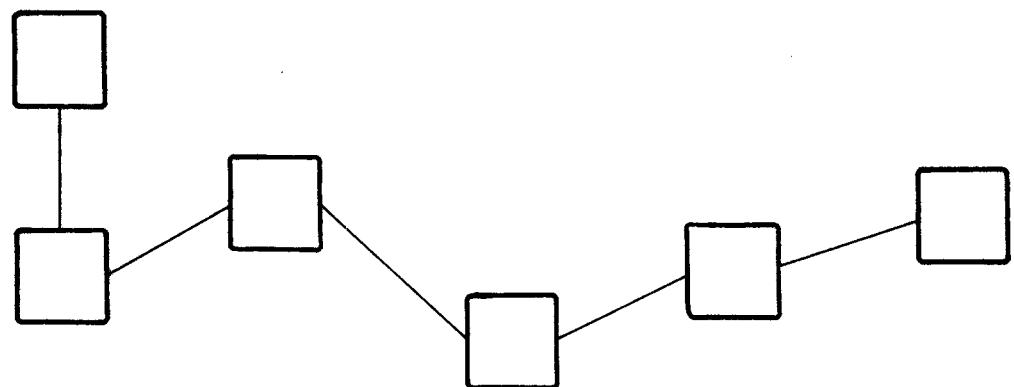

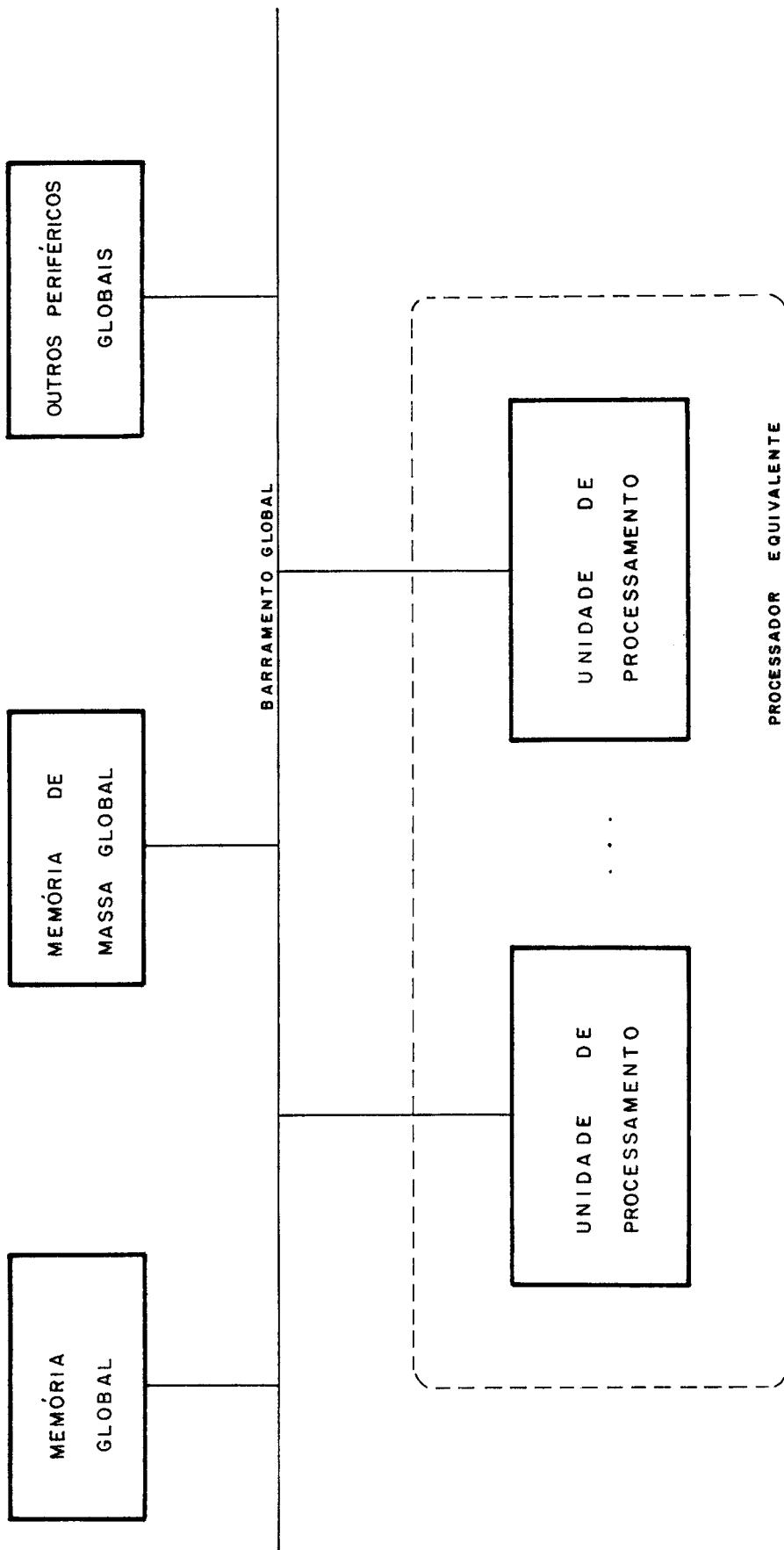

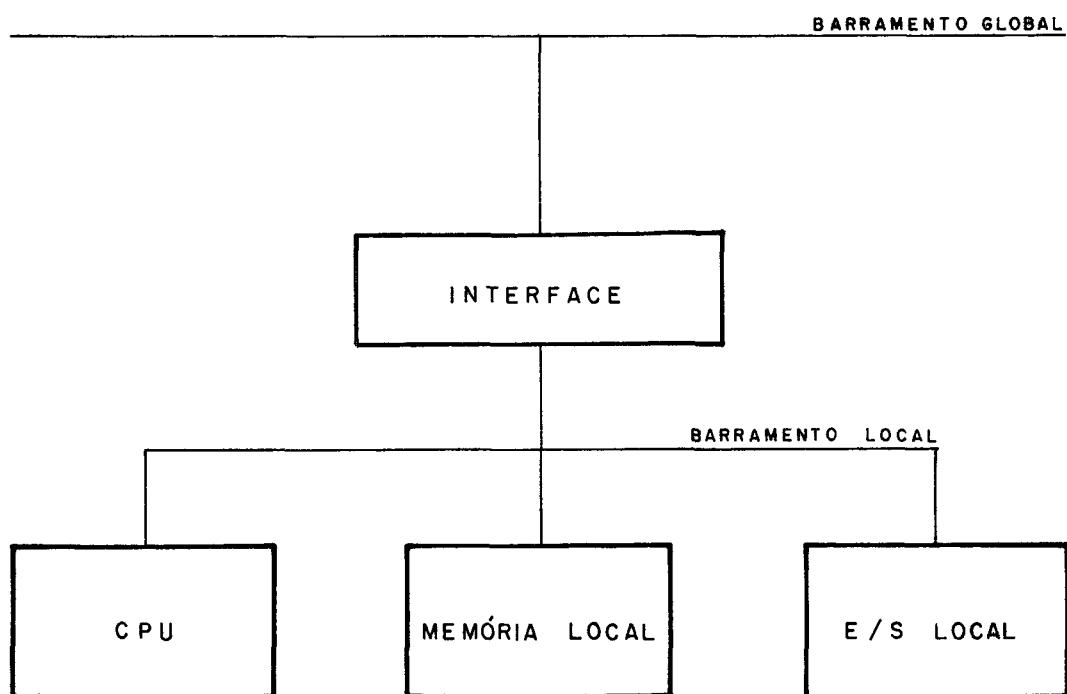

analisada segundo parâmetros atualizados, já que diversos fatores, como o custo de componentes por exemplo, tem sofrido constante modificações através do tempo. As duas arquiteturas mostradas na Figura III.1 diferem quanto ao grau de acoplamento existente entre os elementos que a compõe. Esta diferença reflete na verdade dois conjuntos de problemas e soluções que estão sendo investigados para atender a dois tipos diferentes de aplicação: as que exigem distribuição da inteligência para execução de tarefas independentes e as que buscam na aproximação dos componentes uma maior eficiência na resolução de problemas mais interligados. A seguir serão analisadas mais detalhadamente estas duas alternativas.

### III.1. MULTIPROCESSADORES

As pesquisas iniciais na área de multiprocessamento foram direcionadas para aplicações militares e de controle. O objetivo inicial era explorar a grande disponibilidade que poderia ser obtida com a interligação de um grupo de unidades idênticas, cada uma capaz de executar as mesmas tarefas. Somente mais tarde é que os projetistas começaram a capitalizar os ganhos em performance que poderiam ser alcançados por tais arquiteturas. As maiores dificuldades com que os pesquisadores do assunto se depararam estavam relacionadas com o software destas máquinas. Em alguns casos, os computadores eram comercializados antes mesmo que houvesse disponibilidade de um sistema operacional adequado.

Um computador baseado em multiprocessamento, é tido como uma máquina formada por dois ou mais processadores com capacidades aproximadamente semelhantes, agrupadas de forma tal que todos possam compartilhar a memória e os periféricos principais do sistema. Os processadores são controlados por um sistema operacional que deve prover uma estreita interação entre eles, tanto nos diversos níveis de software quanto nas funções de hardware (51).

a. - ESTRUTURA FRACAMENTE CONECTADA: O PRINCIPAL RECURSO COMUM É O PRÓPRIO SISTEMA DE COMUNICAÇÃO.

b. - ESTRUTURA FORTEMENTE CONECTADA: OS RECURSOS PRINCIPAIS DO SISTEMA SÃO LIGADOS DIRETAMENTE AO SISTEMA DE COMUNICAÇÃO.

FIGURA III.1 - FORMAS DE INTERLIGAÇÃO DE PROCESSADORES, MEMÓRIAS E E/S.

### III.1.1 REQUISITOS BÁSICOS

Da definição pode-se concluir, como primeiro requisito para um sistema baseado em multiprocessamento, que o fluxo de dados deve ser organizado de uma forma tal que permita que um processador possa acessar uma informação em qualquer parte do sistema (memória ou e/s). A única ressalva aceitável e vantajosa em determinadas situações ocorre nos casos em que recursos locais são reservados para um determinado processador. Dependendo da eficiência e segurança desejadas na arquitetura final, outros requisitos se fazem necessários:

- Mútua exclusão: Para garantir a integridade dos dados deve ser previsto no hardware um acesso exclusivo aos recursos compartilhados.

- Endereçamento virtual: Um esquema de endereçamento que utilize referências lógicas em vez de físicas permite maior flexibilidade no gerenciamento da alocação de recursos.

- Deteção e recuperação de falhas: Um processador deve ser capaz de sinalizar ou interromper qualquer outro. Isto permite, entre outras coisas, a verificação e a manutenção do bom estado de funcionamento do sistema. Em caso de pane, as informações que estavam sendo acessadas em um processador devem poder ser transferidas para o elemento que irá continuar a execução. A recuperação exige ainda que um processador possa reinicializar outro que esteja potencialmente operacional.

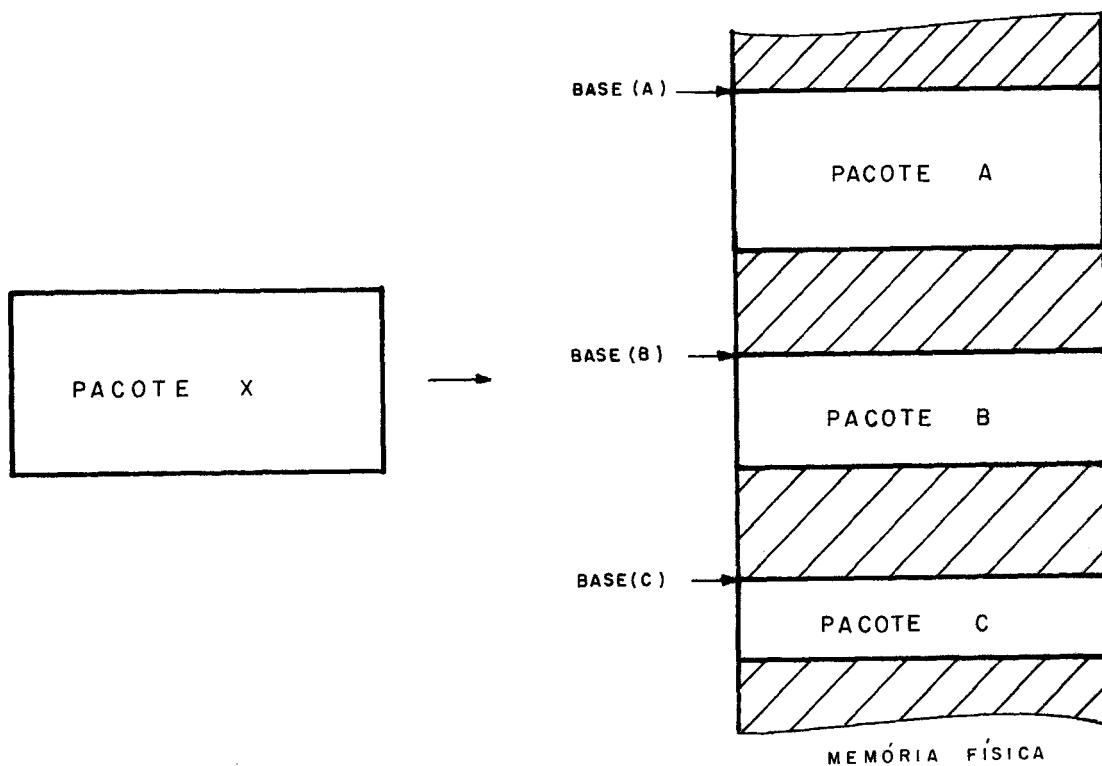

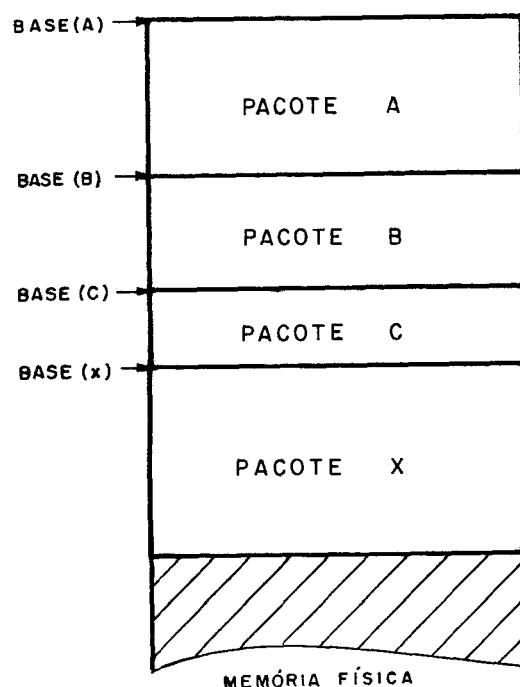

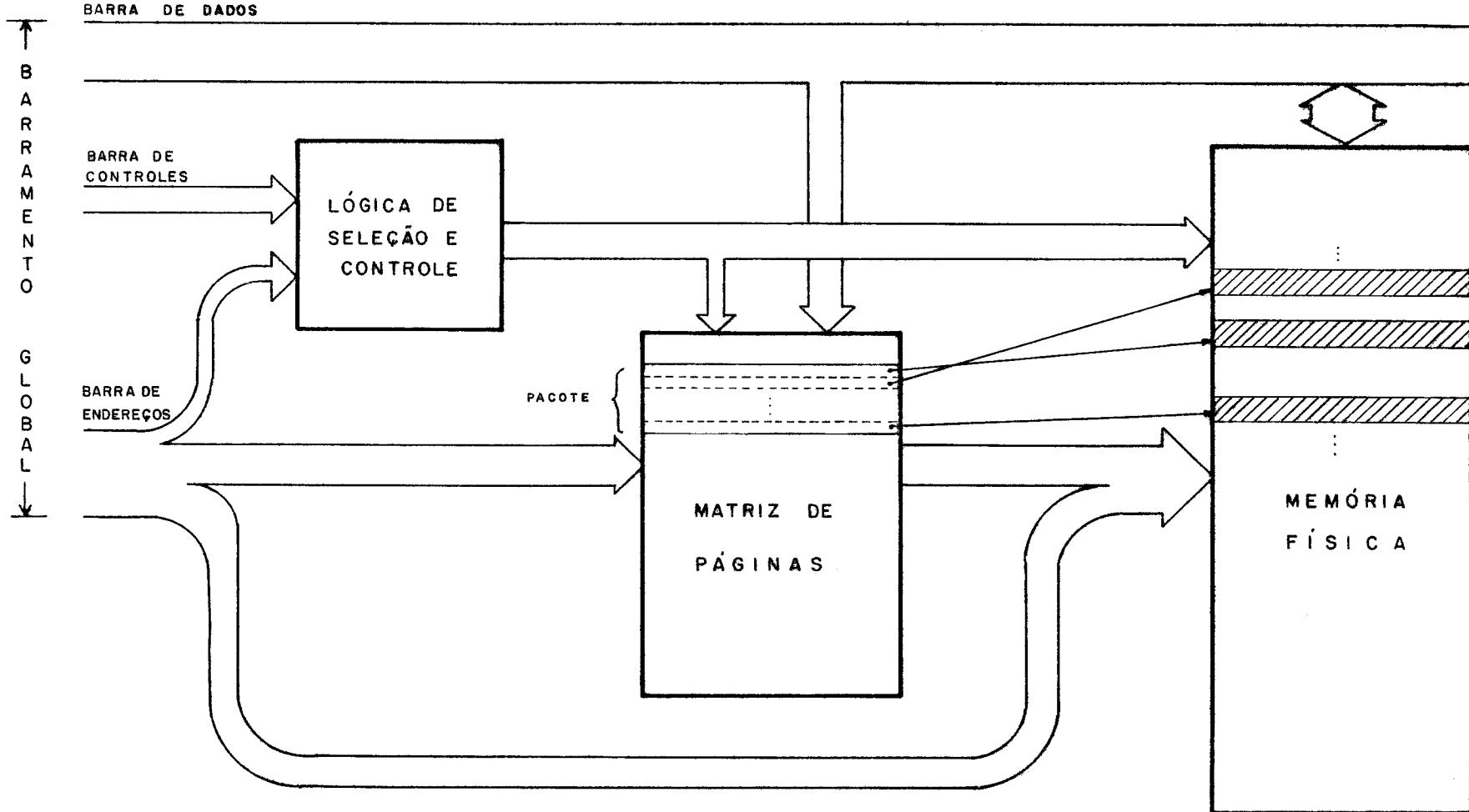

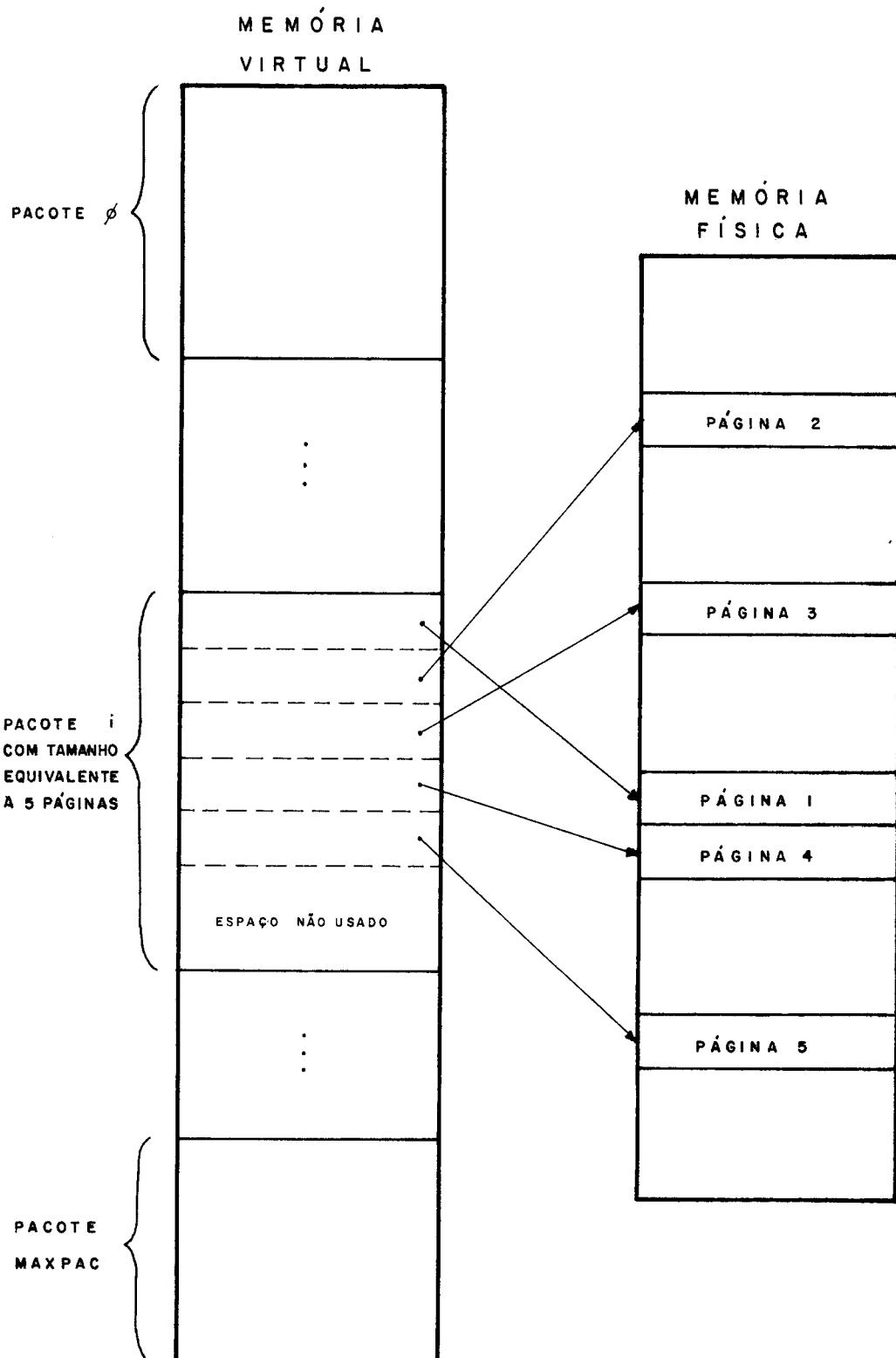

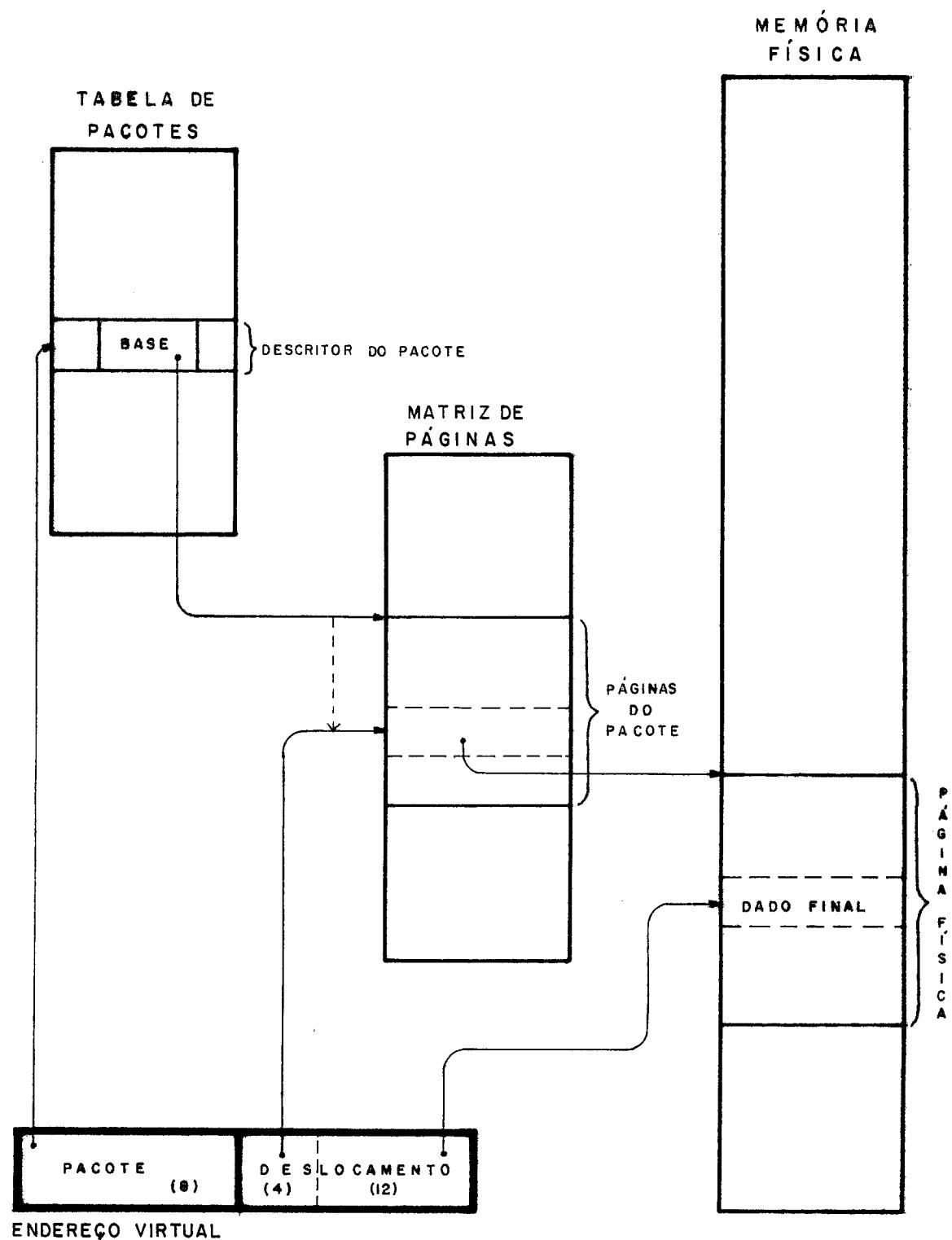

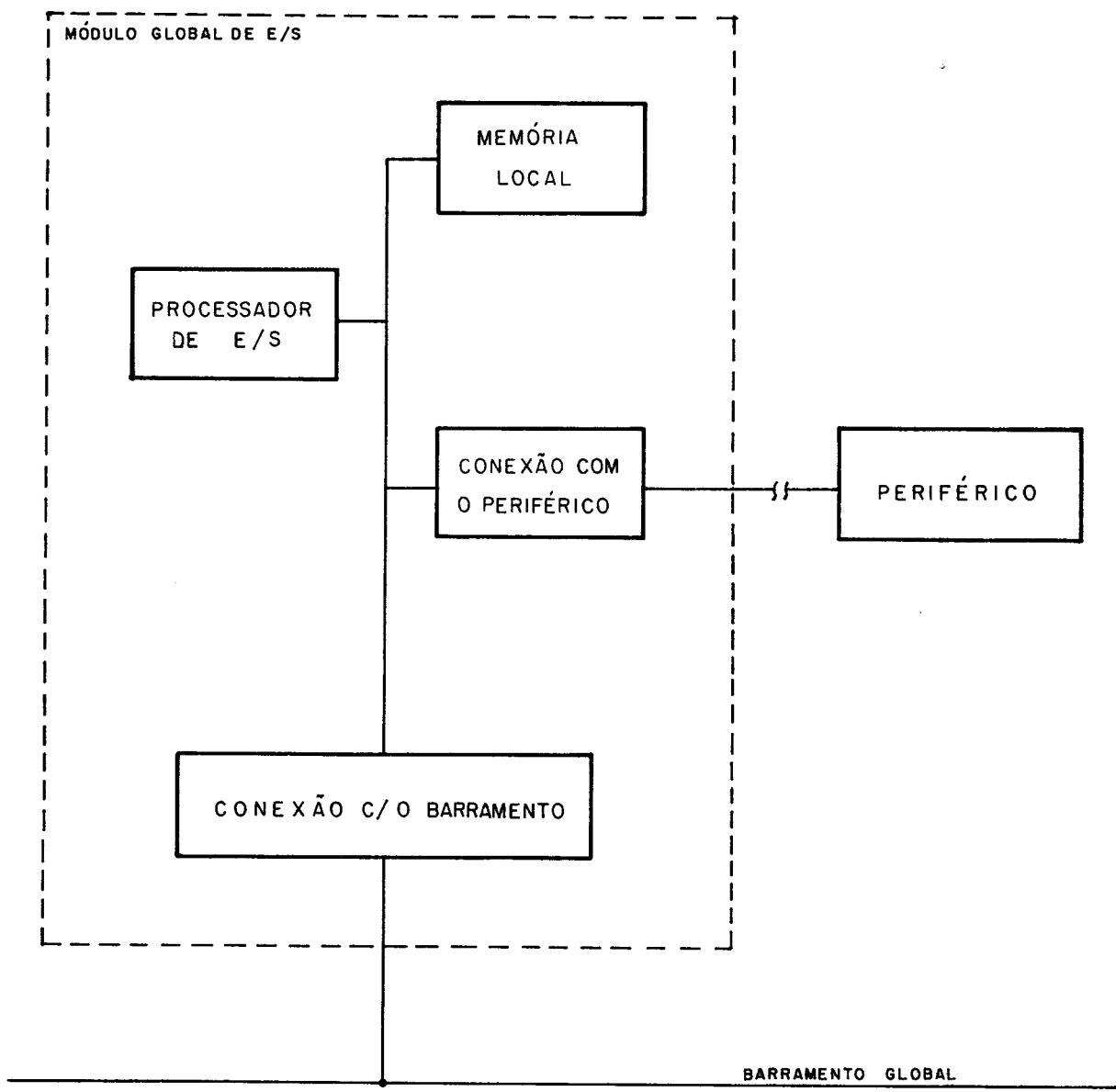

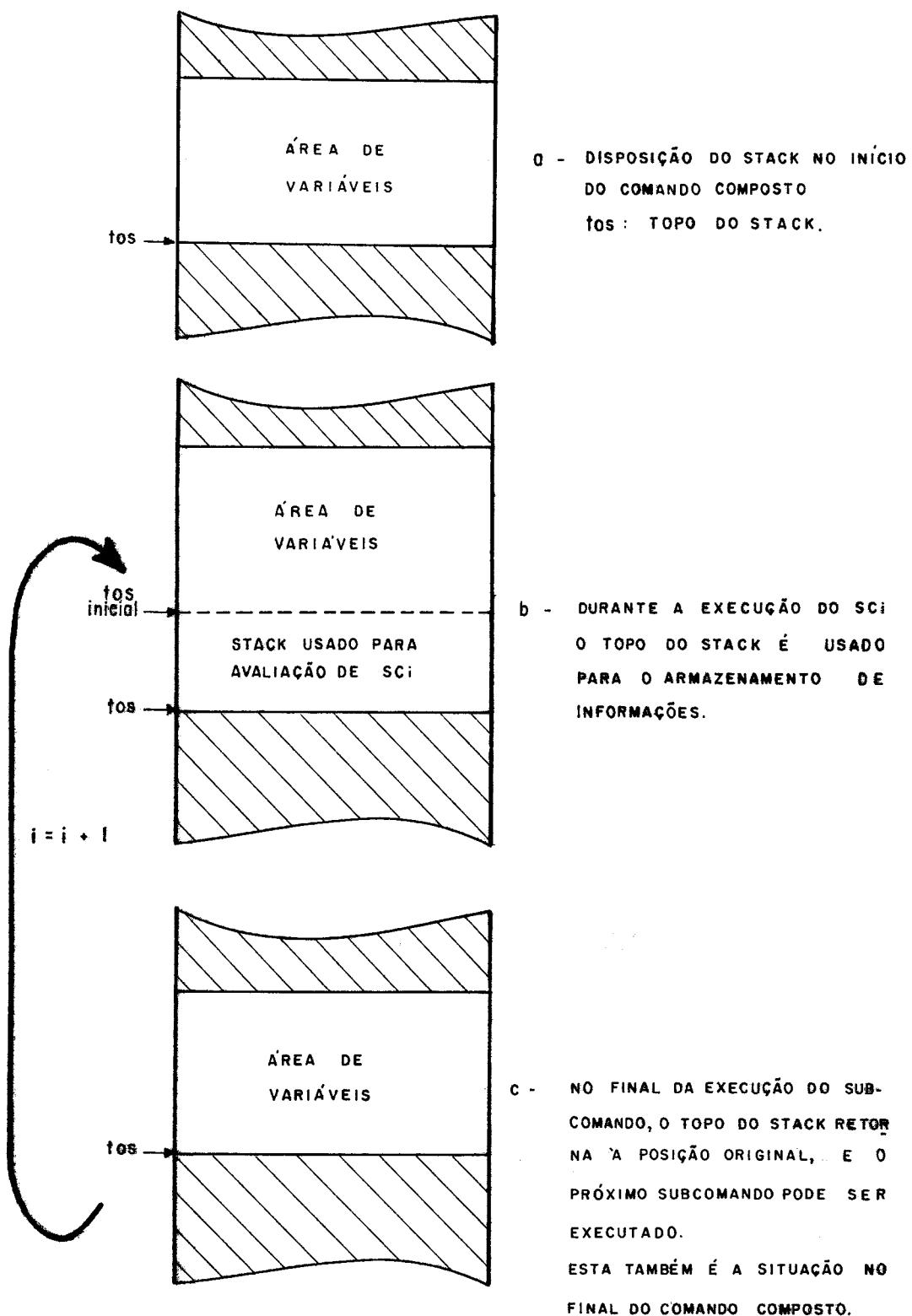

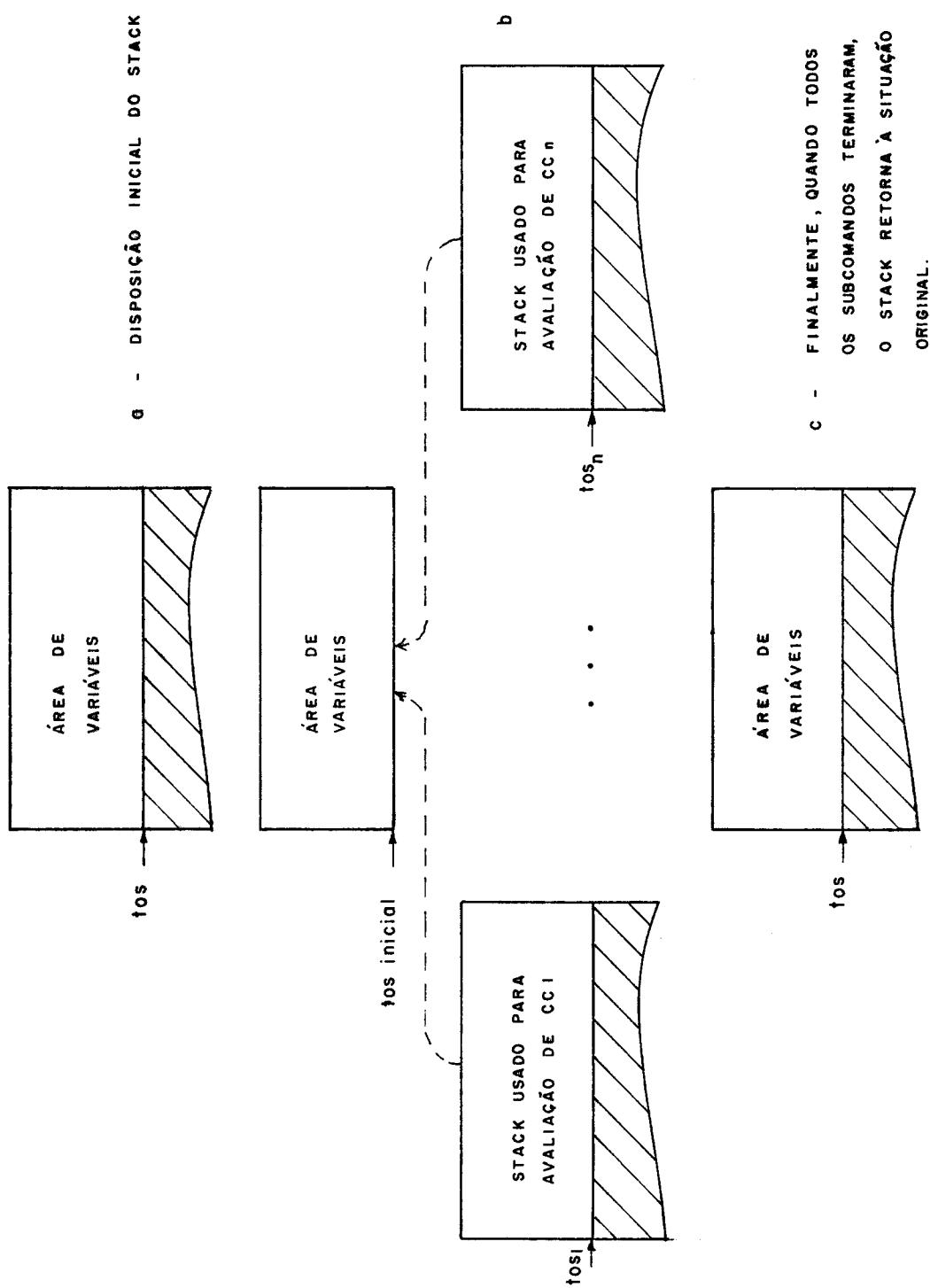

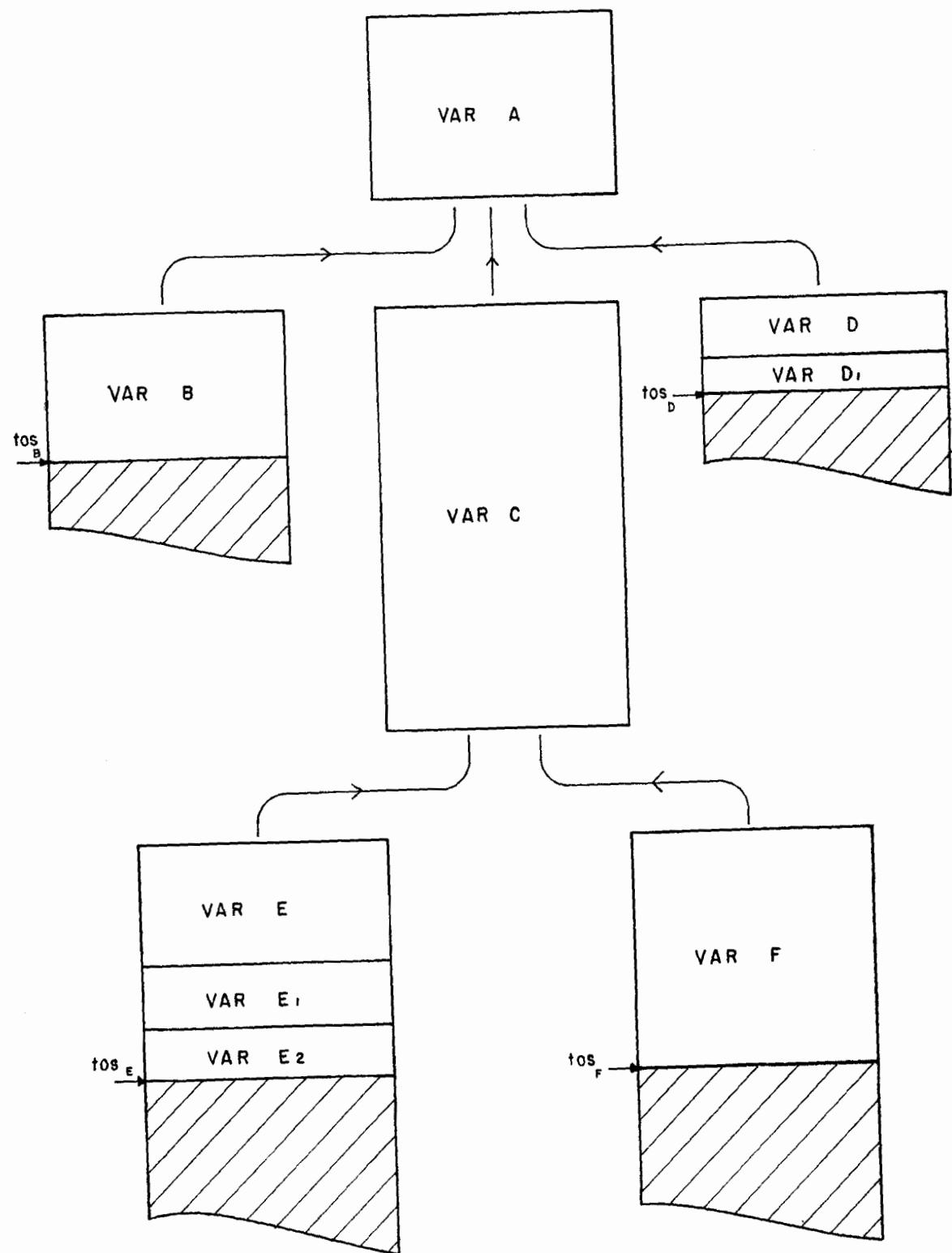

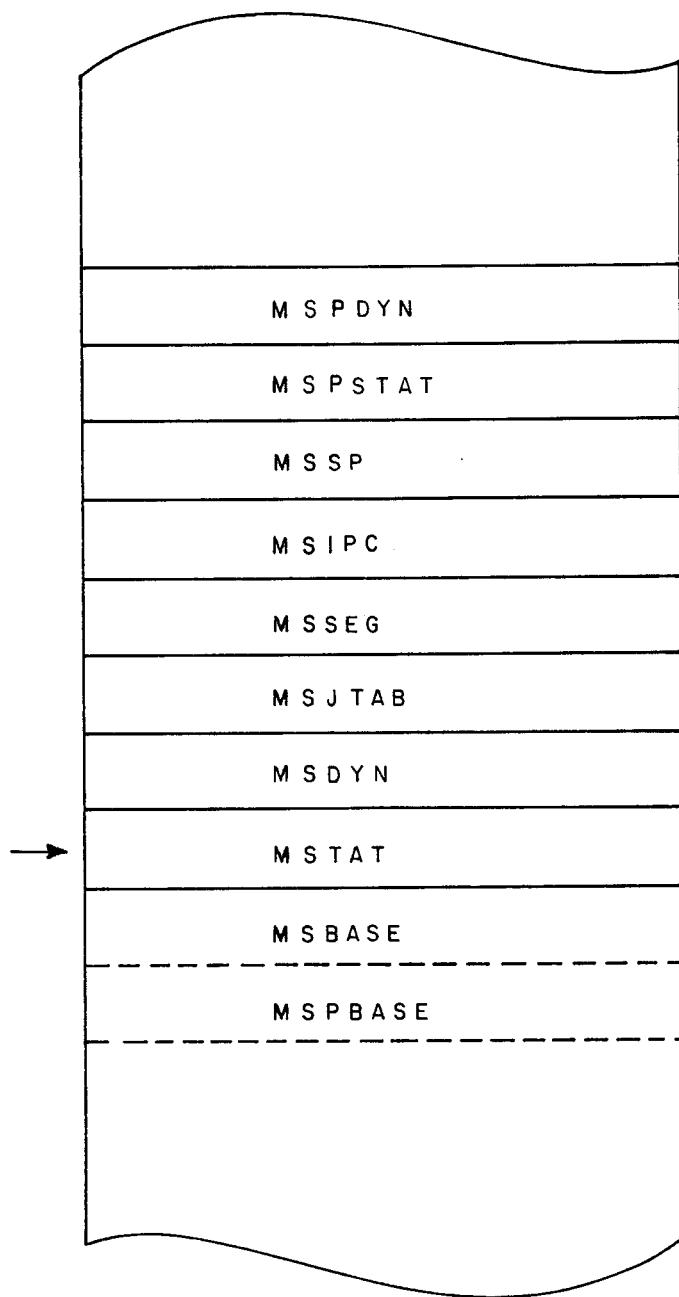

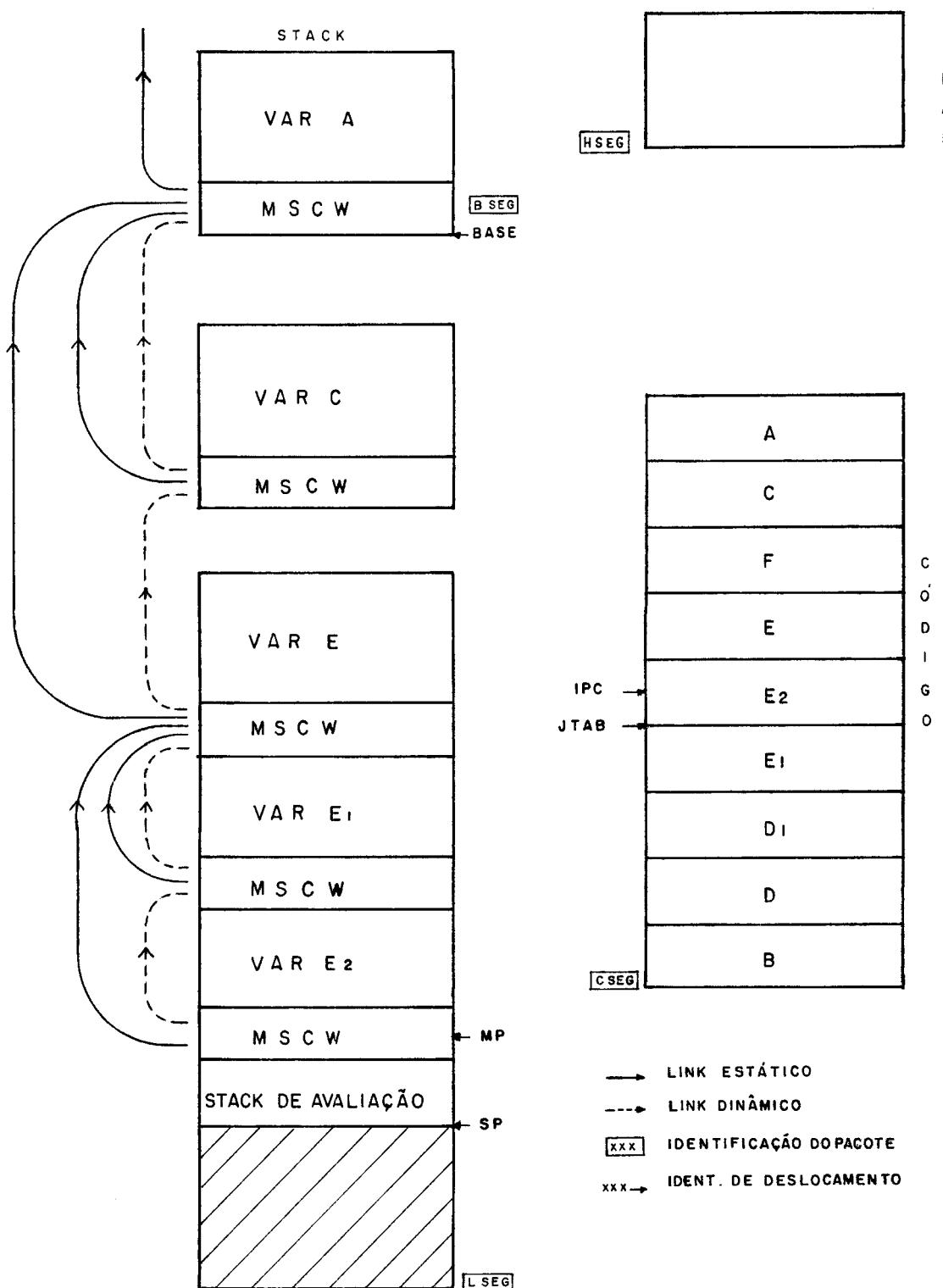

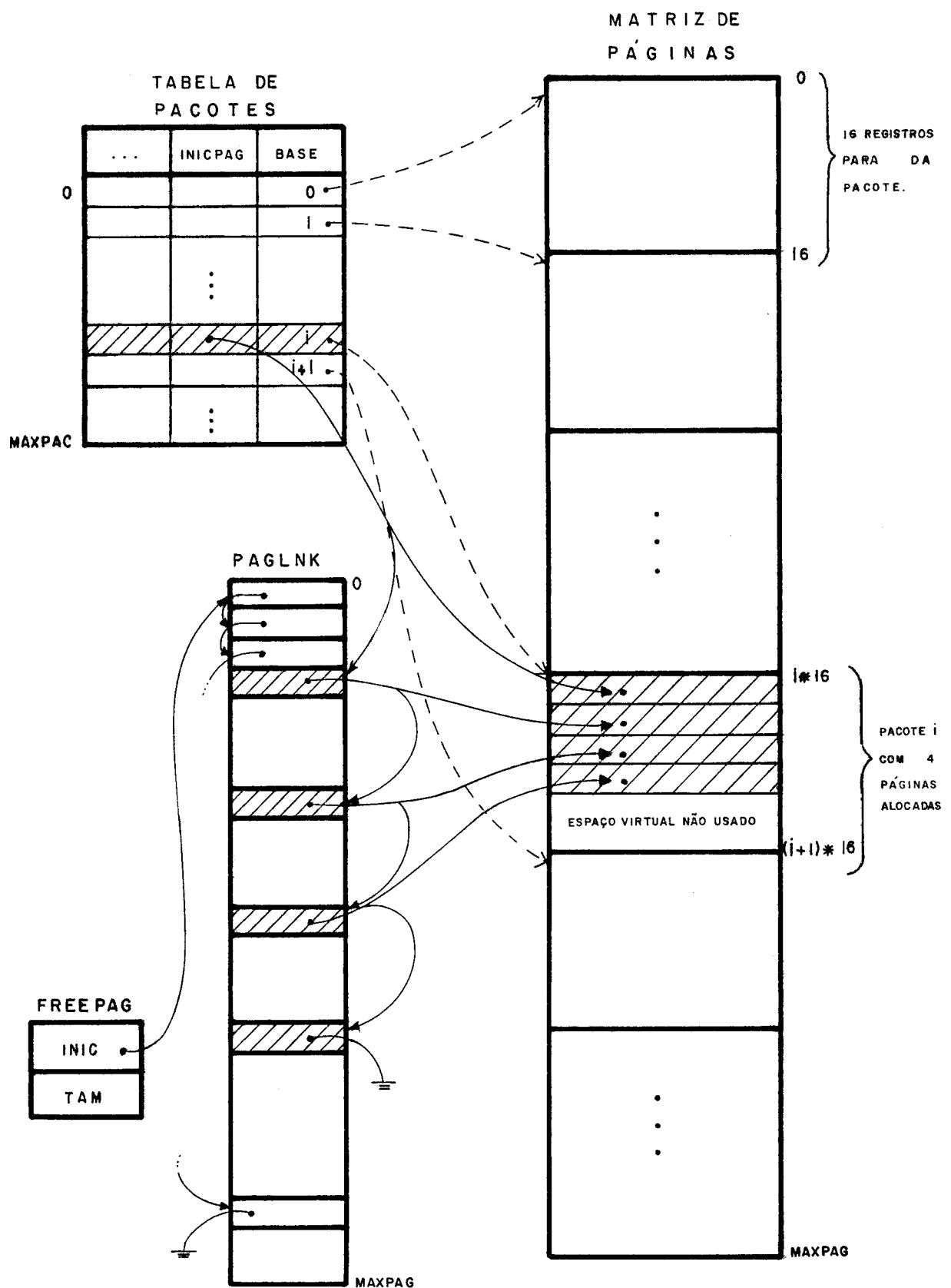

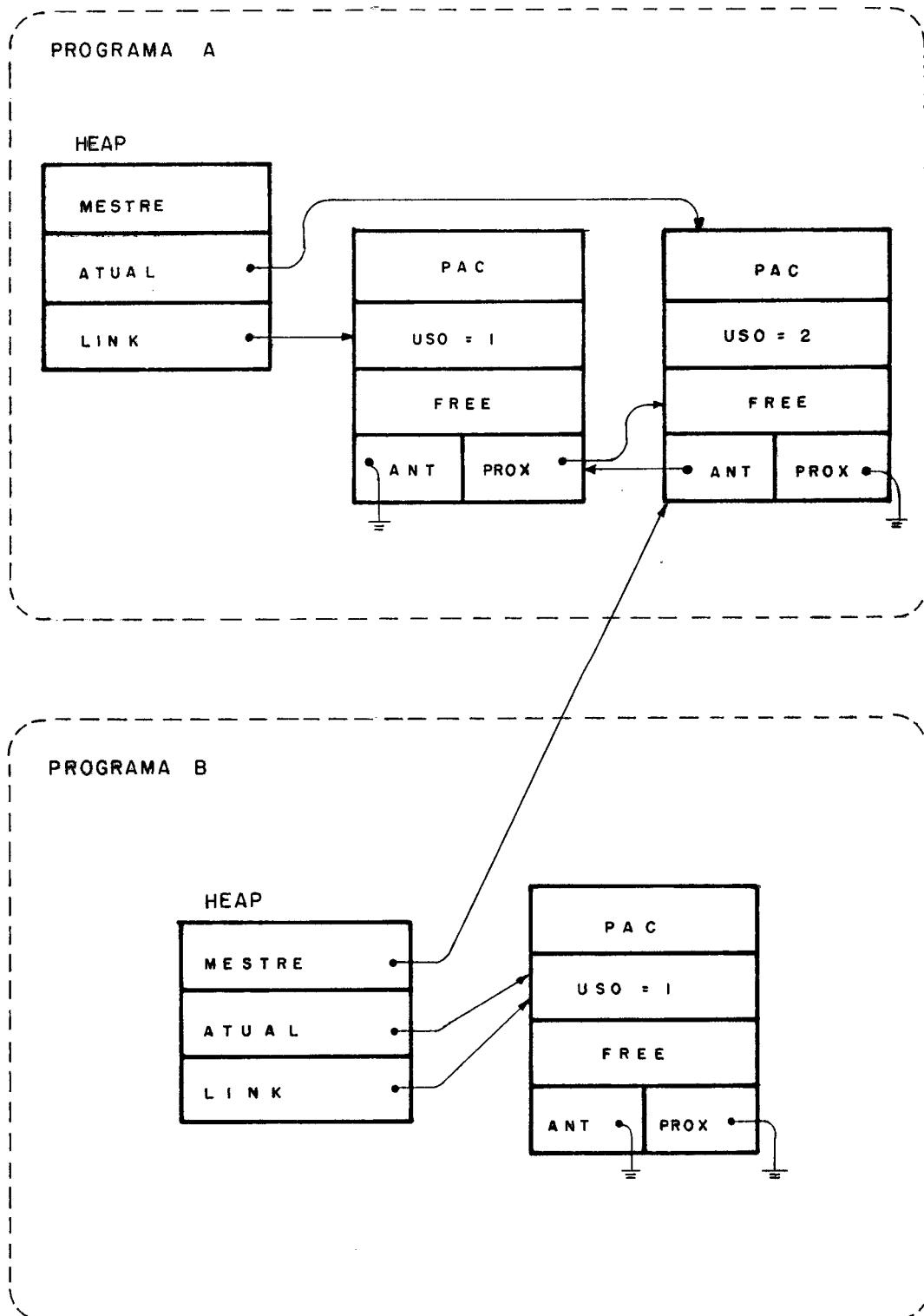

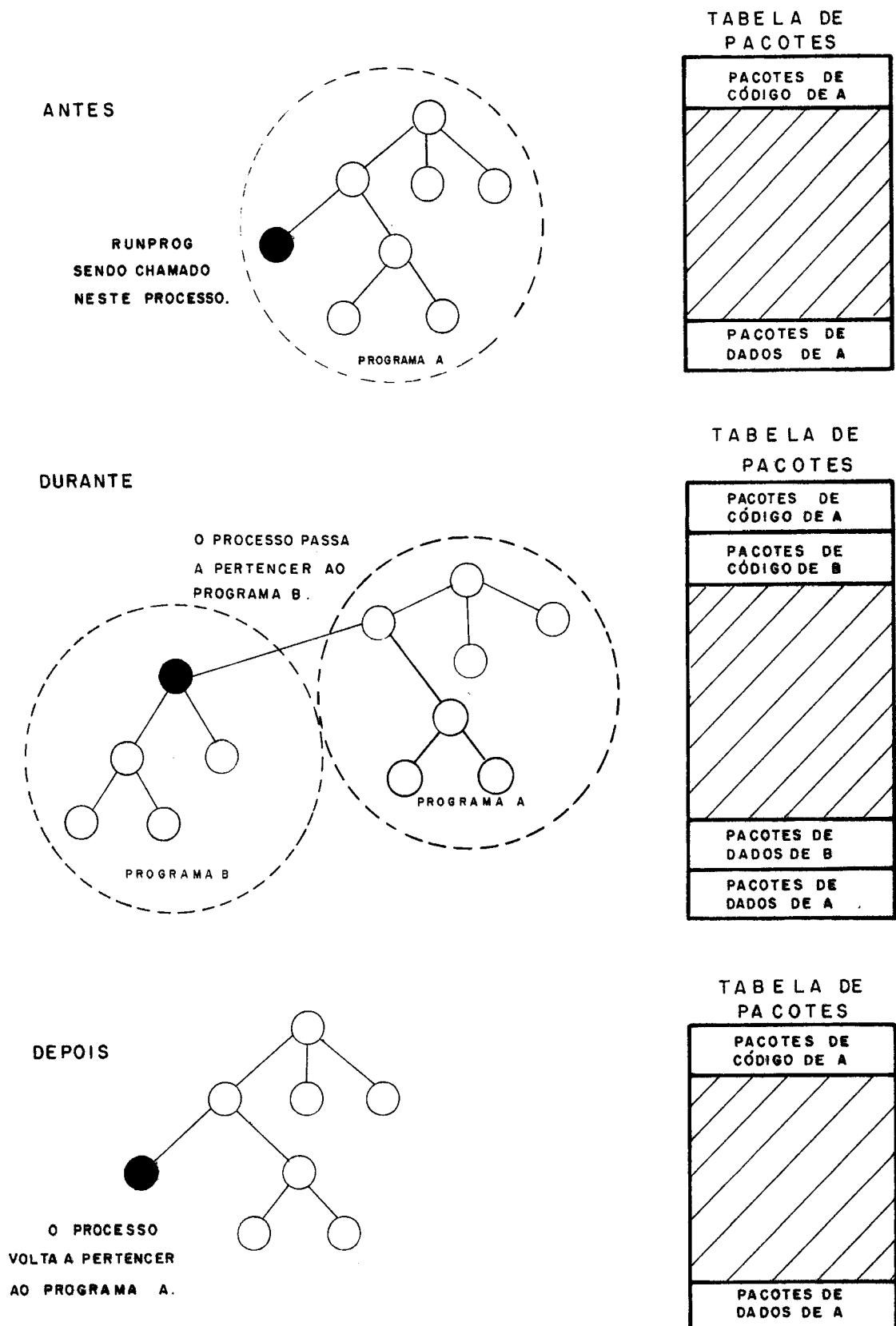

### III.1.2. ESTRUTURAS DE INTERCONEXÃO