MEMORIZAÇÃO E REUSO DINÂMICO DE TRAÇOS EM UMA

ARQUITETURA DE PROCESSADOR JAVA

Bruno Rodrigues Silva

DISSERTAÇÃO SUBMETIDA AO CORPO DOCENTE DA

COORDENAÇÃO DOS PROGRAMAS DE PÓS-GRADUAÇÃO DE

ENGENHARIA DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO

COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A

OBTENÇÃO DO GRAU DE MESTRE EM CIÊNCIAS EM

ENGENHARIA DE SISTEMAS E COMPUTAÇÃO.

Aprovada por:

Prof. Felipe Matia Galvão França, Ph.D.

Prof. Edil Severiano Tavares Fernandes, Ph.D.

Prof. Amarildo Teodoro da Costa, D.Sc.

Prof. Alberto Ferreira de Souza, Ph.D.

RIO DE JANEIRO, RJ - BRASIL

FEVEREIRO DE 2006

SILVA, BRUNO RODRIGUES

Memorização e Reuso Dinâmico de Traços em uma Arquitetura de Processador Java

[Rio de Janeiro] 2006

XVI, 106 p. 29,7 cm (COPPE/UFRJ,

M.Sc., Engenharia de Sistemas e Computação, 2006)

Dissertação - Universidade Federal do Rio de Janeiro, COPPE

1. Reuso Dinâmico de traços

2. Arquitetura Java

3. Sistemas Embarcados

I. COPPE/UFRJ II. Título (série)

*"Nunca ande pelo caminho traçado,

pois ele conduz somente até onde os outros foram".*

*Alexandre Graham Bell*

# Agradecimentos

Primeiramente a Deus que, com sua misericórdia infinita, sempre esteve ao meu lado, mesmo não sendo eu digno de tantas bênçãos. A cada dia vejo o quão pequeno sou diante de tanta magnitude e bondade do Pai, e a cada dia vejo que DEUS É FIEL!

Ao professor Felipe Maia Galvão França que, com seu humor inteligente e de forma tão simples e humilde, me acolheu como seu orientando e possibilitou que a minha experiência de viver dois anos em função do mestrado fosse a mais proveitosa possível. Agradeço pela sugestão do tema para o desenvolvimento dessa pesquisa e deixo claro que seus ensinamentos ficarão para sempre em minha memória. Sem você não teria conseguido.

À minha família que sempre acreditou no meu potencial e mesmo com todas as dificuldades sempre apoiou meus estudos no que pôde. Mãe, mais uma vez obrigado por ter me conscientizado da importância dos estudos.

Ao grande amigo Renato Afonso Conta Silva, eterno companheiro desde os tempos de graduação. No passado lutamos juntos por dias melhores e hoje somos gratos a Deus pois esses dias chegaram.

Às grandes amizades formadas durante os dois anos do mestrado: João Maurício, Bernardo, Patrícia, Raquel, Fernanda, Fabiano, Danilo, Eduardo Melione e aos

novatos do LAM: Ivomar, Leandro e Elias. Pessoas que jamais serão esquecidas.

À Universidade Federal do Rio de Janeiro, e em especial ao Programa de Engenharia de Sistemas e Computação da COPPE por ter contribuído para minha formação e ter tão bem recebido esse mineiro.

A todos os funcionários do Programa de Engenharia de Sistemas e Computação da COPPE, e em especial à Cláudia, Sônia, Adilson, Itamar, Solange, Lurdes e Mercedes. Vocês foram minha família nesses dois anos de luta.

Ao NACAD - Núcleo de Atendimento de Computação de Alto Desempenho da COPPE, pelo uso do Cluster Mercury, extremamente importante durante a execução dos experimentos.

Ao Depto. de Informática da UFRGS e em especial ao professor Luigi Carro e ao amigo Antônio Carlos Beck Filho pela grande atenção dispensada no início dessa pesquisa.

Ao professor Ulisses Leitão que desde os tempos de graduação sempre acreditou e apostou no meu potencial e sempre me apoiou nas decisões mais difíceis. Compartilho essa conquista com você, amigo.

Ao apoio financeiro da CAPES, CNPq e Instituto Doctum de Tecnologia.

Resumo da Dissertação apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Mestre em Ciências (M.Sc.)

## MEMORIZAÇÃO E REUSO DINÂMICO DE TRAÇOS EM UMA ARQUITETURA DE PROCESSADOR JAVA

Bruno Rodrigues Silva

Fevereiro / 2006

Orientador: Felipe Maia Galvão França

Programa: Engenharia de Sistemas e Computação

Esta pesquisa realiza uma análise do comportamento do mecanismo *DTM* (*Dynamic Trace Memoization*) implementado em uma arquitetura de processador Java. Tal mecanismo se propõe à memorizar e reusar dinamicamente traços redundantes, *i.e.*, sequências de instruções redundantes, buscando evitar a re-execução destes traços quando eles forem novamente alcançados com o mesmo conjunto de valores de entrada observados e registrados anteriormente durante a execução do programa. Para tanto, o mecanismo DTM foi modificado para se adaptar à arquitetura Java, dando origem ao mecanismo *JDTM* (*Java Dynamic Trace Memoization*). Foi avaliada a sua efetividade através de simulação dirigida à execução utilizando o simulador de um microprocessador *pipeline* escalar Java. De acordo com os resultados obtidos da execução de um conjunto de programas típicos de sistemas embarcados, alcançou-se a aceleração de 12% (média harmônica). Esta aceleração é justificada pela redução do número de instruções executadas e pela redução do número de bolhas inseridas no *pipeline* em vista das dependências de recursos, de dados e de controle.

Abstract of Dissertation presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Master of Science (M.Sc.)

DYNAMIC TRACE MEMOIZATION AND REUSE IN A JAVA PROCESSOR

ARCHITECTURE

Bruno Rodrigues Silva

February / 2006

Advisor: Felipe Maia Galvão França

Department: Computing and Systems Engineering

This research make an analysis of the behavior of DTM (Dynamic Trace Memoization) mechanism implemented in a Java processor architecture. Such mechanism dynamically memorize and reuse redundant traces, i.e., sequences of redundant instructions to prevent the re-execution of them when they are reached again with the same set of input values observed previously during the execution of a program. The DTM mechanism was modified for the Java architecture, originating the JDTM (Java Dynamic Trace Memoization) mechanism. Using a Java scalar pipelined microprocessor simulator was employed to evaluate the effectiveness of the mechanism. According to the results of the execution of a typical programs set of embedded systems, it reached 12% speedup (harmonic average). This speedup is justified by the reduction in the number of executed instructions and by the reduction in the number of inserted bubbles in pipeline because of the resources, data and control dependencies.

# Sumário

|          |                                                                                 |           |

|----------|---------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introdução</b>                                                               | <b>1</b>  |

| 1.1      | Motivação . . . . .                                                             | 3         |

| 1.2      | Trabalhos Relacionados . . . . .                                                | 6         |

| 1.2.1    | Explorando a redundância através de Reuso de valores . . . . .                  | 8         |

| 1.2.2    | Explorando a redundância através de Predição de valores . . . . .               | 9         |

| 1.2.3    | Semelhanças e diferenças entre Reuso de valores e Predição de valores . . . . . | 10        |

| 1.2.4    | Outros Trabalhos . . . . .                                                      | 11        |

| 1.3      | Objetivos e contribuições . . . . .                                             | 11        |

| 1.4      | Estrutura do Trabalho . . . . .                                                 | 13        |

| <b>2</b> | <b>Background</b>                                                               | <b>14</b> |

| 2.1      | Processador FemtoJava . . . . .                                                 | 14        |

| 2.1.1    | FemtoJava multiciclo 8 <i>bits</i> . . . . .                                    | 14        |

| 2.1.2    | Breve descrição de alguns <i>bytecodes</i> Java . . . . .                       | 16        |

| 2.1.3    | FemtoJava <i>Low Power 32 bits</i> . . . . .                                    | 25        |

|          |                                                                           |           |

|----------|---------------------------------------------------------------------------|-----------|

| 2.2      | Simulador CACO-PS . . . . .                                               | 29        |

| 2.2.1    | Descrição da arquitetura e simulação . . . . .                            | 30        |

| 2.3      | DTM - Dynamic Trace Memoization . . . . .                                 | 33        |

| 2.3.1    | Introdução . . . . .                                                      | 33        |

| 2.3.2    | Definições . . . . .                                                      | 35        |

| 2.3.3    | Memorização e identificação de instruções redundantes . . . . .           | 36        |

| 2.3.4    | Construção de traços com base em instruções redundantes . . . . .         | 37        |

| 2.3.5    | Reuso de traços redundantes . . . . .                                     | 40        |

| <b>3</b> | <b>JDTM - Java Dynamic Trace Memoization</b>                              | <b>44</b> |

| 3.1      | Introdução e definições . . . . .                                         | 44        |

| 3.2      | O domínio de <i>bytecodes</i> válidos . . . . .                           | 46        |

| 3.3      | Identificação de <i>bytecodes</i> redundantes . . . . .                   | 47        |

| 3.4      | Construção de traços redundantes . . . . .                                | 51        |

| 3.4.1    | Início e fim da construção dos traços . . . . .                           | 54        |

| 3.4.2    | Construção dos contextos de entrada e de saída . . . . .                  | 55        |

| 3.4.2.1  | Contexto de entrada/saída referente ao pool de variáveis locais . . . . . | 55        |

| 3.4.2.2  | Contexto de entrada/saída referente à pilha de operandos . . . . .        | 56        |

| 3.4.3    | Informações extras . . . . .                                              | 58        |

| 3.5      | Um exemplo de construção de traço redundante . . . . .                    | 59        |

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| 3.6 Reuso de traços . . . . .                                           | 62        |

| <b>4 Experimentos e Resultados</b>                                      | <b>65</b> |

| 4.1 Metodologia . . . . .                                               | 65        |

| 4.1.1 Ambiente de Simulação . . . . .                                   | 65        |

| 4.1.2 <i>Benchmarks</i> . . . . .                                       | 66        |

| 4.1.3 Parâmetros Arquiteturais . . . . .                                | 69        |

| 4.1.4 Métricas . . . . .                                                | 70        |

| 4.2 Resultados . . . . .                                                | 71        |

| 4.2.1 Reuso e Aceleração . . . . .                                      | 71        |

| 4.2.1.1 Remarcação dinâmica de <i>bytecodes</i> não redundantes         | 74        |

| 4.2.2 Custo e efetividade . . . . .                                     | 84        |

| 4.2.3 Caracterização dos <i>bytecodes</i> reusados . . . . .            | 88        |

| 4.2.4 Tamanho dos contexto de entrada e saída do traços reusados .      | 90        |

| 4.2.5 Número de <i>bytecodes</i> inclusos nos traços reusados . . . . . | 93        |

| 4.2.6 Número de desvios realizados inclusos nos traços reusados .       | 94        |

| 4.2.7 Caracterização do fim da construção dos traços memorizados .      | 96        |

| <b>5 Conclusões e Trabalhos Futuros</b>                                 | <b>98</b> |

| 5.1 Conclusão . . . . .                                                 | 98        |

| 5.2 Trabalhos Futuros . . . . .                                         | 101       |

# Listas de Figuras

|     |                                                                                                                                                                                                    |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

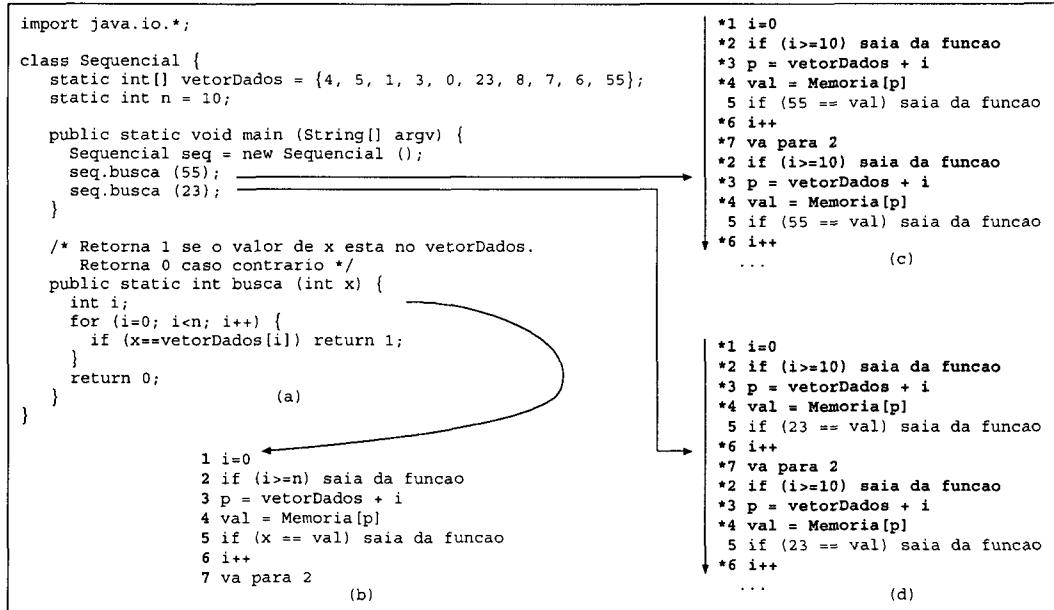

| 1.1 | Cenário ilustrando redundância em um programa Java. As instruções dinâmicas marcadas com '*' realizam a mesma computação para ambas as chamadas ao método <code>int busca (int x)</code> . . . . . | 5  |

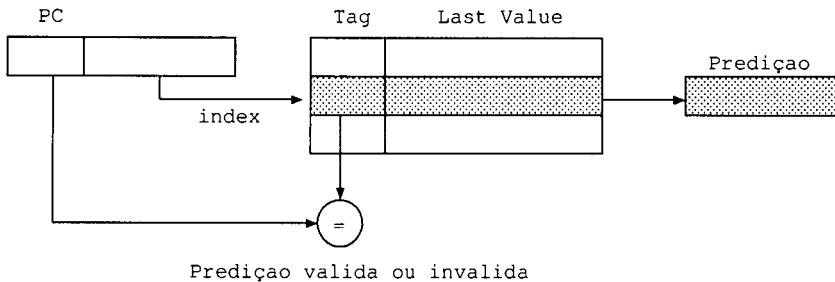

| 1.2 | Técnica de predição de valores - <i>Last Value Predictor</i> . . . . .                                                                                                                             | 7  |

| 1.3 | Técnica de predição de valores - <i>Stride Predictor</i> . . . . .                                                                                                                                 | 7  |

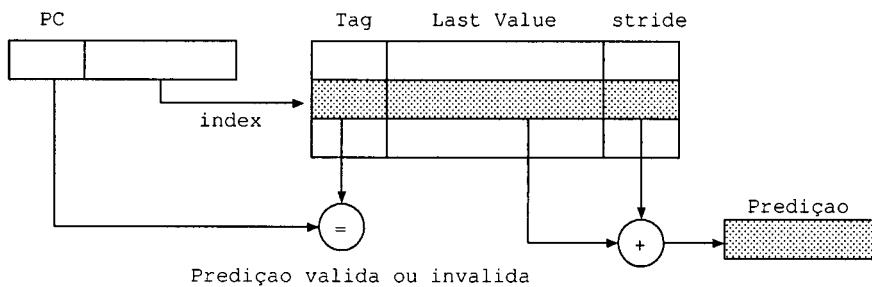

| 1.4 | Técnica de Reuso de valores. . . . .                                                                                                                                                               | 8  |

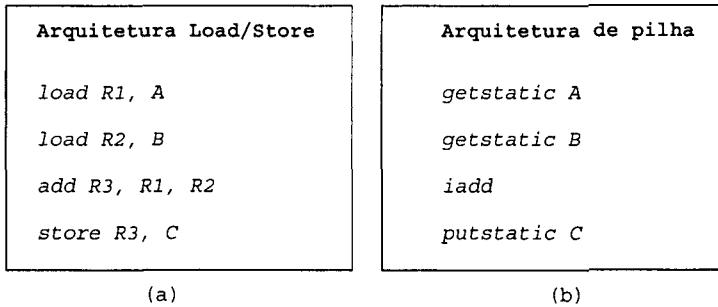

| 2.1 | Sequência de instruções para a operação $C = A + B$ em uma arquitetura <i>load/store(a)</i> e uma arquitetura de pilha (b). . . . .                                                                | 17 |

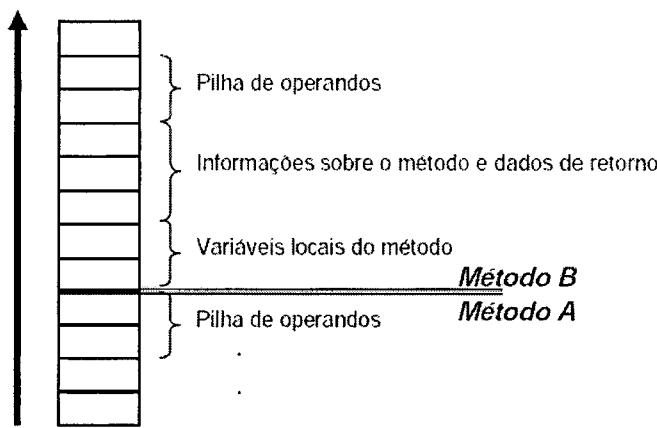

| 2.2 | Organização da pilha de um processador Java típico. . . . .                                                                                                                                        | 18 |

| 2.3 | Algoritmo de pesquisa sequencial implementado em Java. . . . .                                                                                                                                     | 21 |

| 2.4 | Memória de instruções do FemtoJava multiciclo 8 bits contendo os <i>bytecodes</i> do algoritmo de pesquisa sequencial mostrado na Figura 2.3. . . . .                                              | 22 |

| 2.5 | Memória de dados do FemtoJava contendo os dados estáticos do algoritmo de pesquisa sequencial mostrado na Figura 2.3. . . . .                                                                      | 23 |

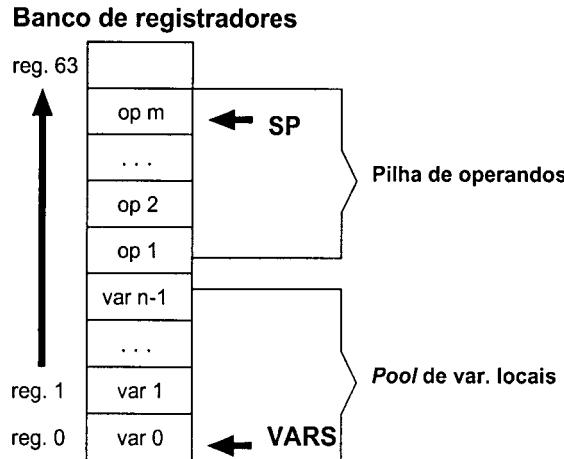

| 2.6 | Organização da pilha do processador FemtoJava <i>Low Power</i> . . . . .                                                                                                                           | 26 |

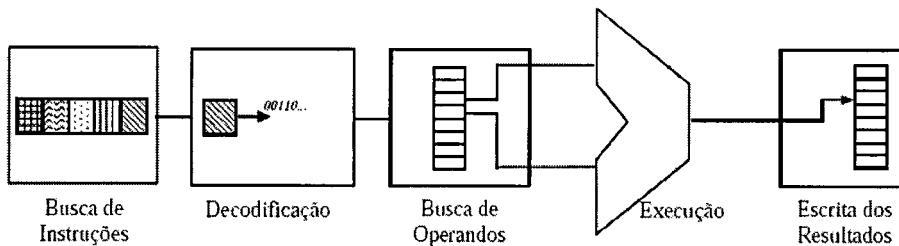

| 2.7 | Os cinco estágios do <i>pipeline</i> do FemtoJava <i>Low Power</i> . . . . .                                                                                                                       | 26 |

|      |                                                                                                                     |    |

|------|---------------------------------------------------------------------------------------------------------------------|----|

| 2.8  | Exemplo de uma microarquitetura alvo. . . . .                                                                       | 31 |

| 2.9  | Descrição de uma microarquitetura alvo na sintaxe do CACO-PS. . . .                                                 | 32 |

| 2.10 | Descrição do comportamento funcional de um registrador de 16 <i>bits</i> (de Beck Filho [5]). . . . .               | 32 |

| 2.11 | Procedimento utilizado para indexar quaisquer das tabelas de memorização. . . . .                                   | 34 |

| 2.12 | Formato de uma entrada de Memo_Table_G. . . . .                                                                     | 36 |

| 2.13 | Composição do buffer, bem como das entradas de Memo_Table_T. . . .                                                  | 38 |

| 2.14 | Construção e reuso de traços redundantes no DTM. . . . .                                                            | 41 |

| 3.1  | Tabela de memorização global (J_Memo_Table_G), utilizada para guardar instâncias de <i>bytecodes</i> . . . . .      | 51 |

| 3.2  | Identificando uma sequência de <i>bytecodes</i> redundantes. . . . .                                                | 52 |

| 3.3  | Formato de uma entrada da tabela J_Memo_Table_T e do <i>buffer</i> de construção. . . . .                           | 52 |

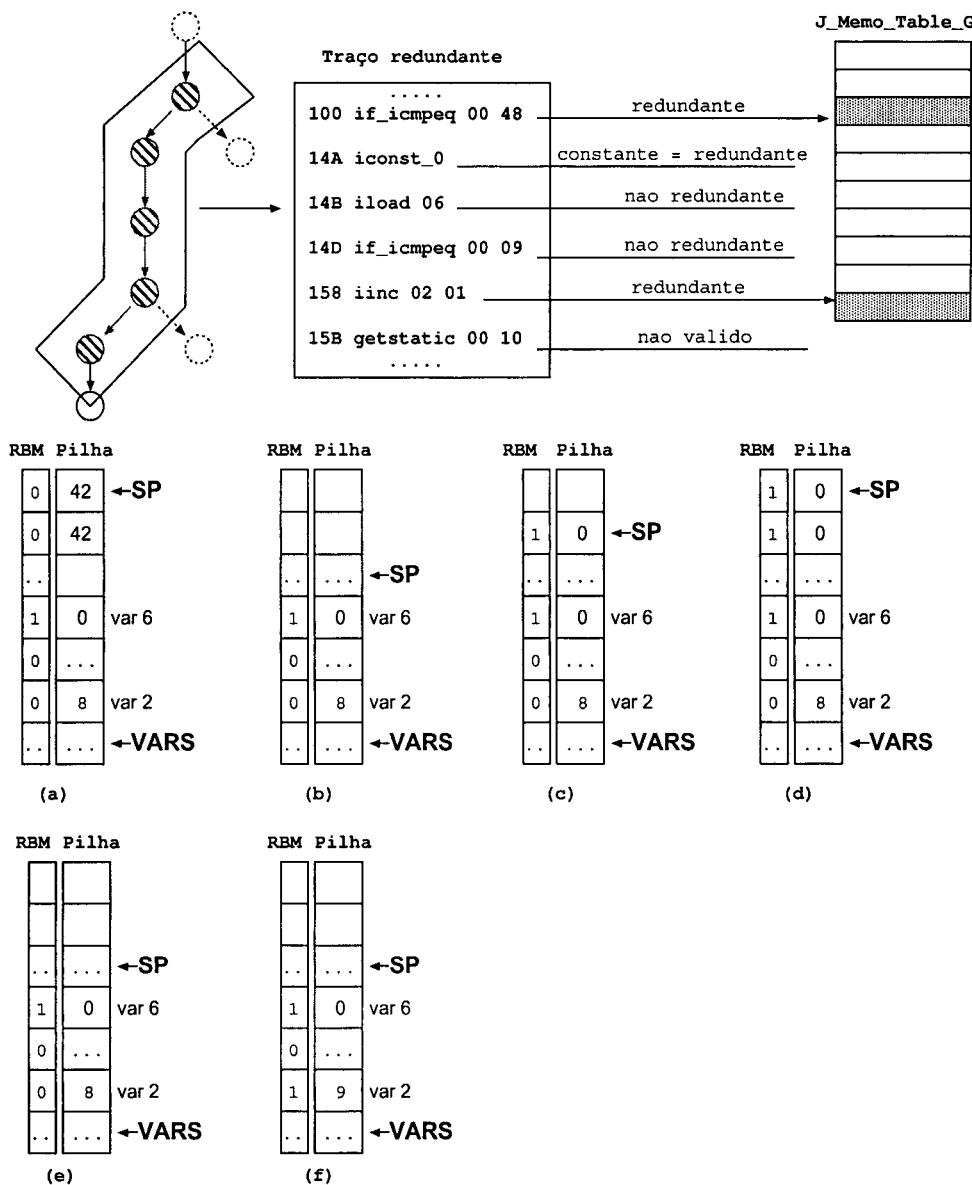

| 3.4  | Construção de um traço redundante identificado a partir de uma sequência de 5 <i>bytecodes</i> redundantes. . . . . | 60 |

| 3.5  | Identificação de oportunidade de reuso de um traço redundante. . . .                                                | 64 |

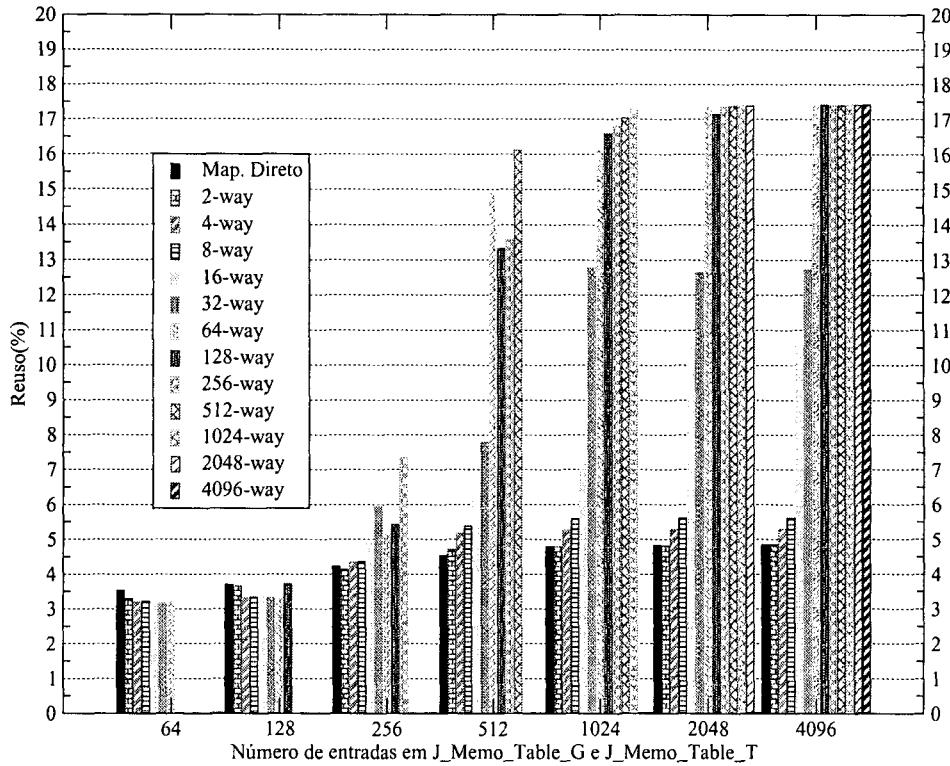

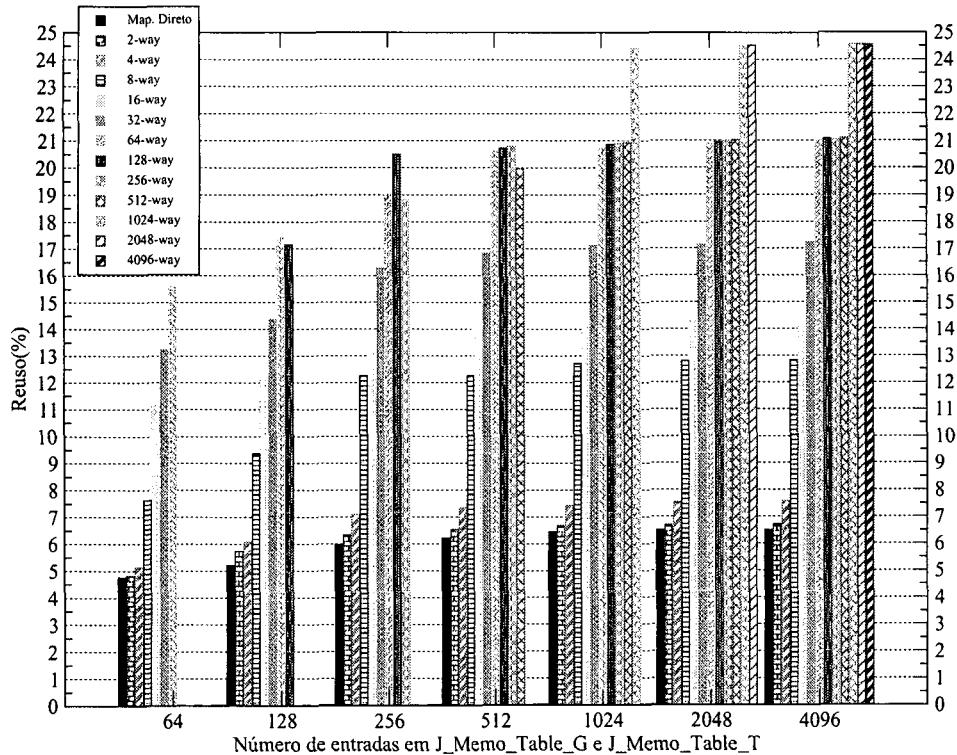

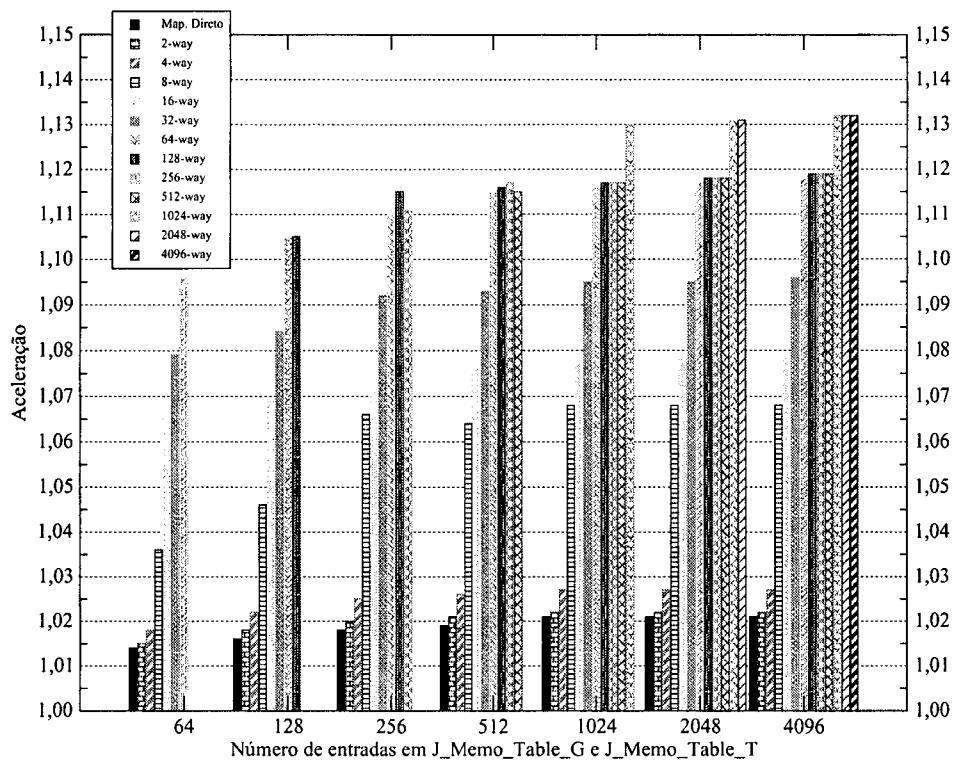

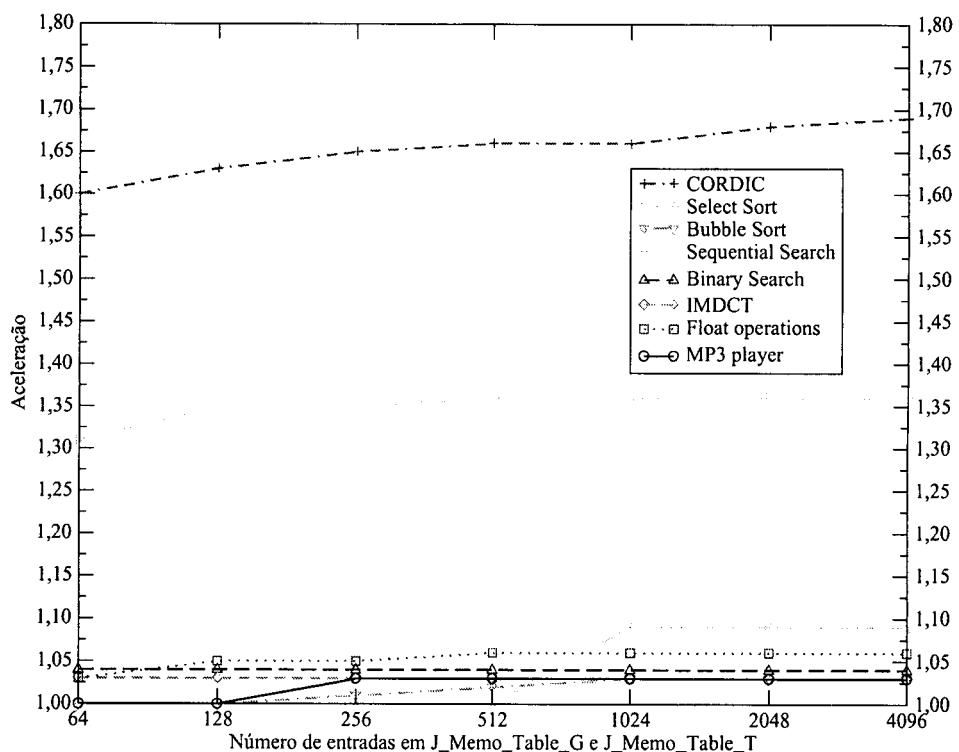

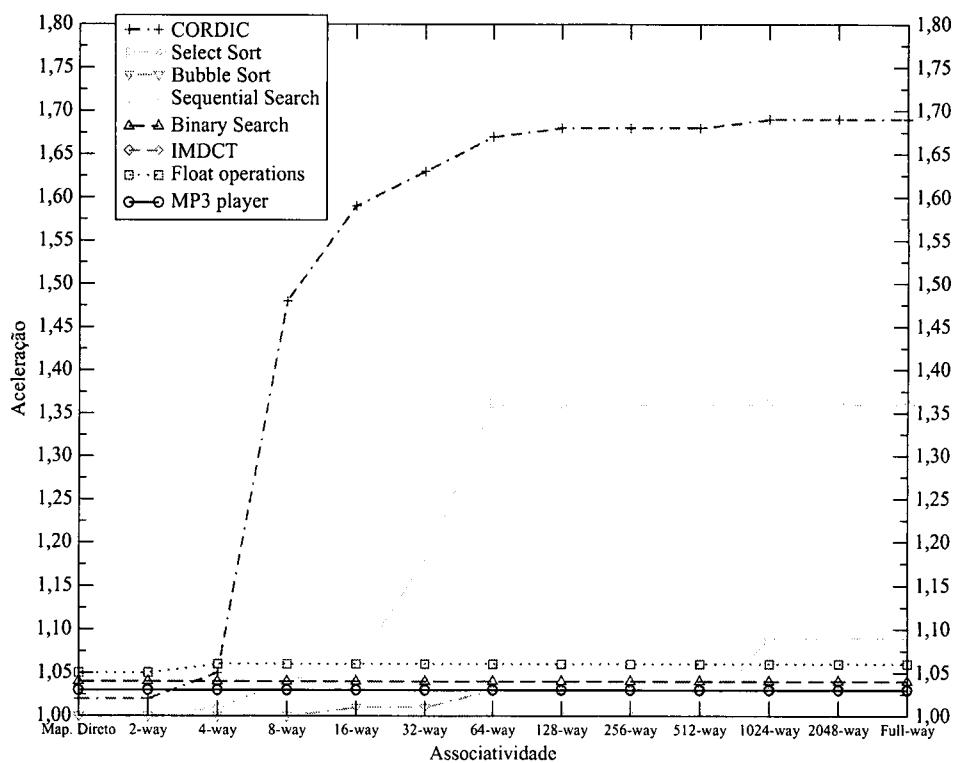

| 4.1  | Percentual de reuso obtido variando o tamanho e a associatividade de ambas as tabelas. . . . .                      | 72 |

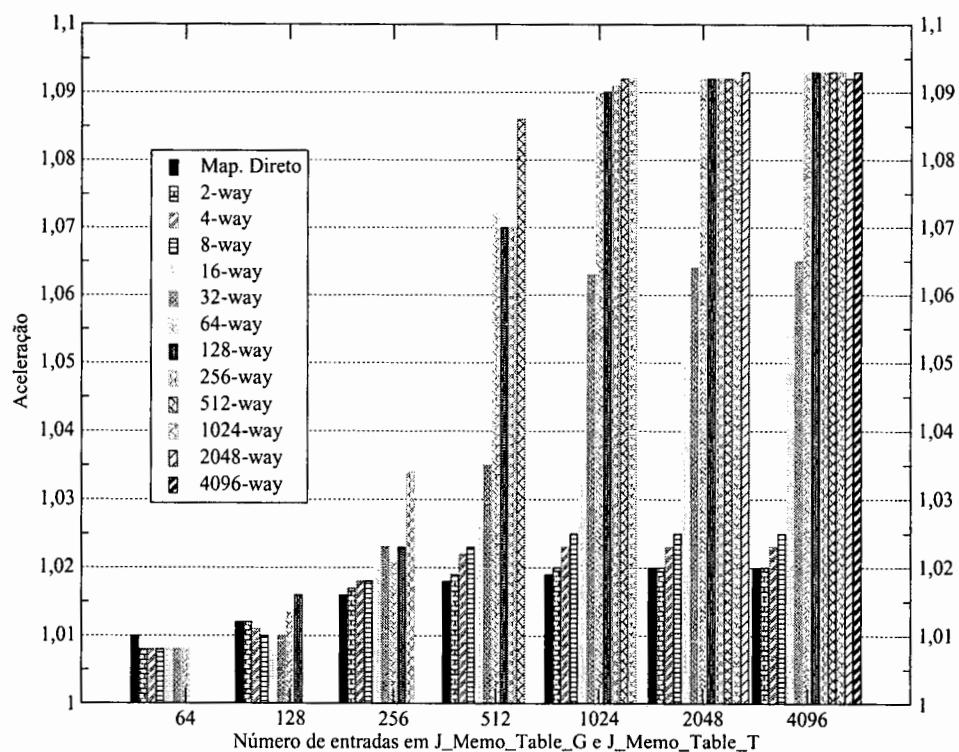

| 4.2  | Aceleração obtida variando o tamanho e a associatividade de ambas as tabelas. . . . .                               | 73 |

|                                                                                                                                                                                                 |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.3 Remarcação de <i>bytecodes</i> não redundante, com base na monitoração dos valores produzidos. . . . .                                                                                      | 77 |

| 4.4 Percentual de reuso obtido através do JDTM com remarcação de <i>bytecodes</i> não redundantes, variando o tamanho e a associatividade de ambas as tabelas. . . . .                          | 78 |

| 4.5 Aceleração obtida através do JDTM com remarcação de <i>bytecodes</i> não redundantes, variando o tamanho e a associatividade de ambas as tabelas. . . . .                                   | 79 |

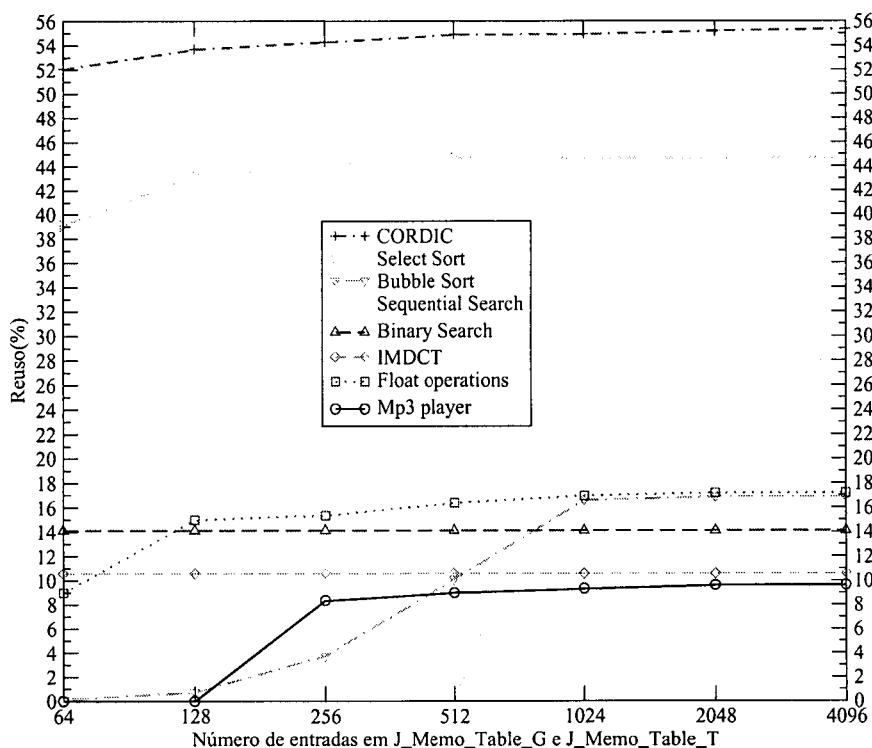

| 4.6 Percentual de reuso alcançado por cada <i>benchmark</i> , com associatividade fixada em <i>full-way</i> e variação do número de entradas de ambas as tabelas. . . . .                       | 80 |

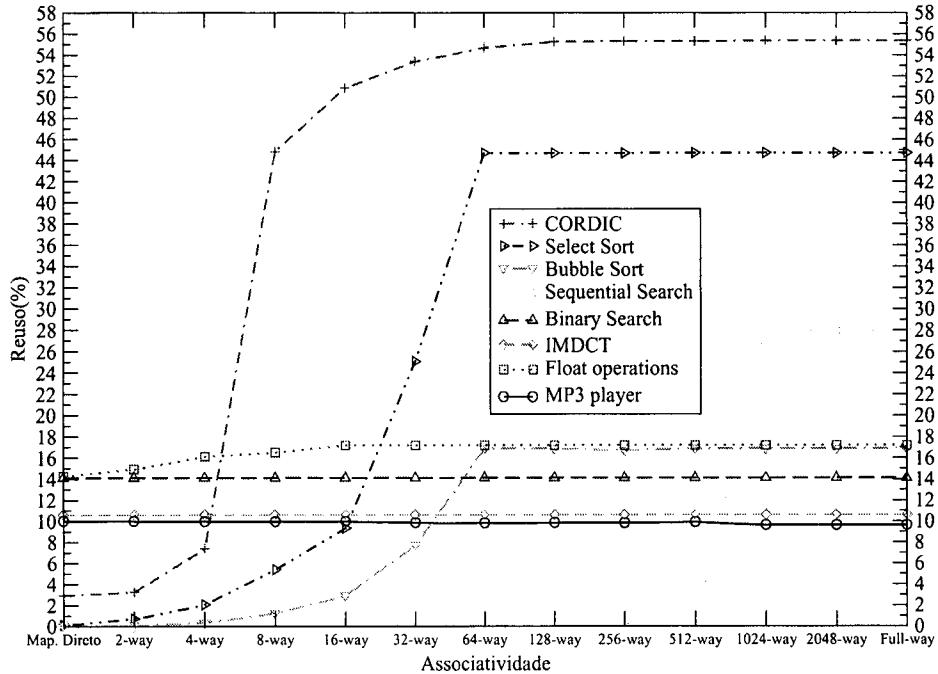

| 4.7 Percentual de reuso alcançado por cada <i>benchmark</i> , com o número de entradas fixado em 4K e variação da associatividade de ambas as tabelas. . . . .                                  | 81 |

| 4.8 Aceleração alcançada por cada <i>benchmark</i> , fixando a associatividade em <i>full-way</i> e variando o número de entradas de ambas as tabelas. . .                                      | 82 |

| 4.9 Aceleração alcançada por cada <i>benchmark</i> , fixado o número de entradas em 4K e variando a associatividade de ambas as tabelas. . . . .                                                | 83 |

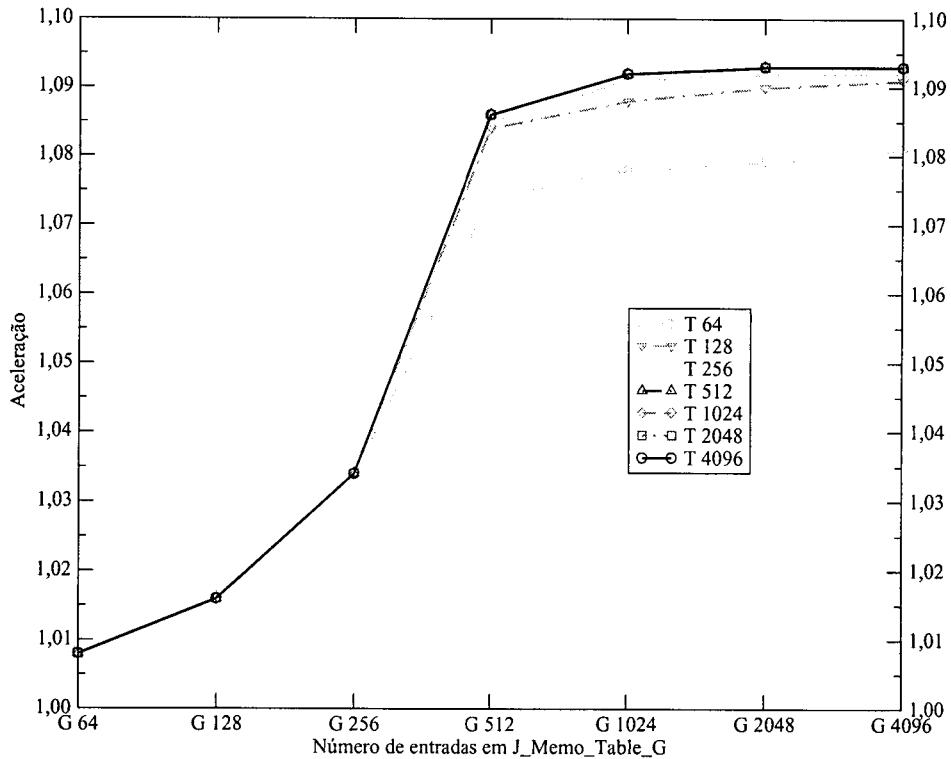

| 4.10 Aceleração obtida a partir do JDTM sem a remarcação de <i>bytecodes</i> não redundantes e todas as possíveis combinações de número de entradas de J_Memo_Table_G e J_Memo_Table_T. . . . . | 85 |

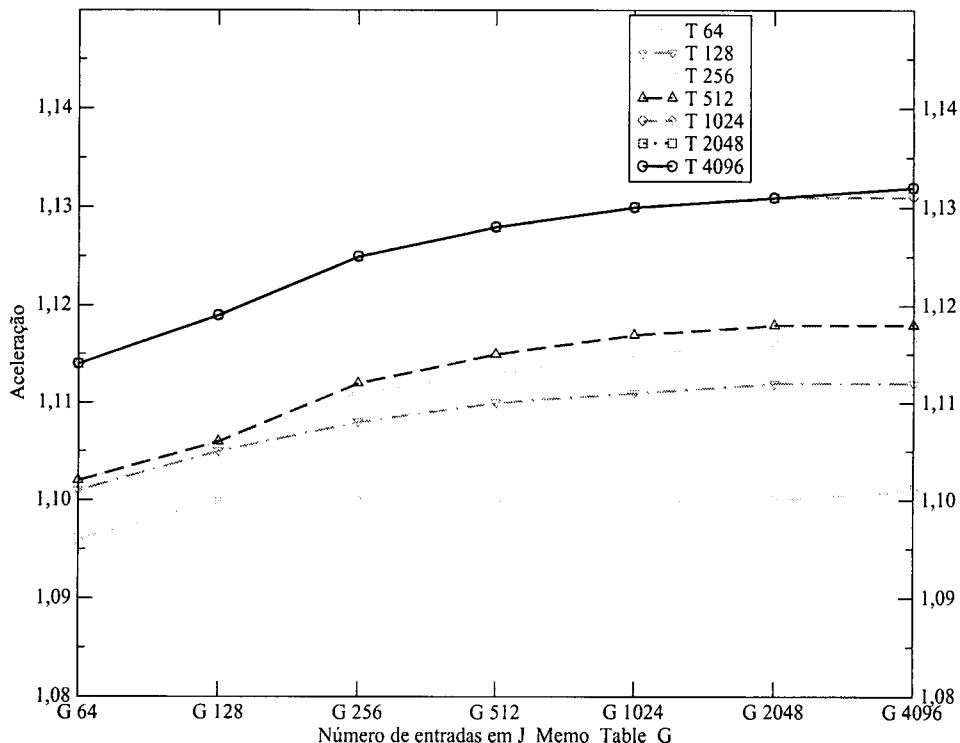

| 4.11 Aceleração obtida a partir do JDTM com a remarcação de <i>bytecodes</i> redundantes e todas as possíveis combinações de número de entradas de J_Memo_Table_G e J_Memo_Table_T. . . . .     | 86 |

|                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.12 Percentual de reuso obtido em cada <i>benchmark</i> utilizando J_Memo_Table_G com 256 entradas e J_Memo_Table_T com 1K entradas. . . . . | 87 |

| 4.13 Aceleração obtida em cada <i>benchmark</i> utilizando J_Memo_Table_G com 256 entradas e J_Memo_Table_T com 1K entradas. . . . .          | 88 |

| 4.14 Distribuição total de <i>bytecodes</i> reusados. . . . .                                                                                 | 89 |

| 4.15 Distribuição percentual do número de elementos no contexto de entrada para os traços reusados. . . . .                                   | 91 |

| 4.16 Distribuição percentual do número de elementos no contexto de saída para os traços reusados. . . . .                                     | 92 |

| 4.17 Distribuição percentual do número de <i>bytecodes</i> nos traços reusados. .                                                             | 93 |

| 4.18 Distribuição percentual do número de desvios realizados nos traços reusados. . . . .                                                     | 95 |

| 4.19 Distribuição percentual da forma de finalização da construção dos traços memorizados. . . . .                                            | 97 |

# Listas de Tabelas

|     |                                                                           |    |

|-----|---------------------------------------------------------------------------|----|

| 2.1 | Instruções suportadas pelo processador FemtoJava.                         | 19 |

| 3.1 | Domínio de <i>bytecodes</i> válidos para a construção de traços.          | 48 |

| 4.1 | Programas, típicos de aplicações embarcadas, utilizados nos experimentos. | 67 |

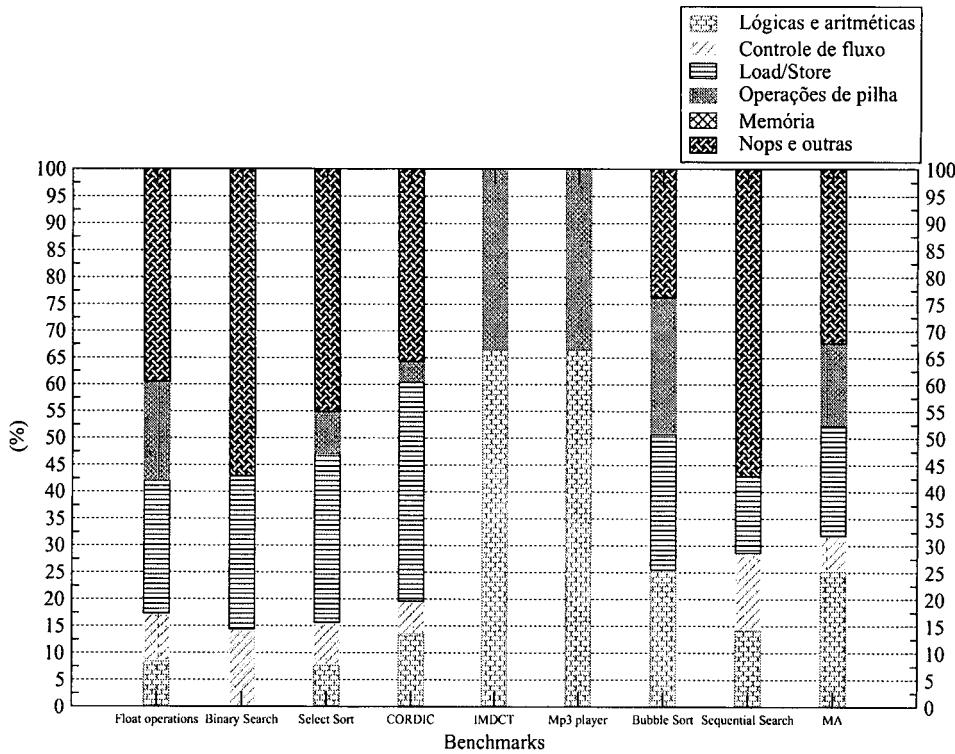

| 4.2 | Distribuição percentual dos <i>bytecodes</i> executados (por classe).     | 68 |

| 4.3 | Configuração do processador substrato.                                    | 69 |

| 4.4 | Parâmetros arquiteturais do mecanismo JDTM.                               | 69 |

# **Palavras-chave**

1. Reuso Dinâmico de Traços.

2. Arquitetura Java.

3. Sistemas Embarcados

# Capítulo 1

## Introdução

A demanda por processadores com maior capacidade de processamento e menor custo vem crescendo consideravelmente a medida que o aumento da complexidade do *software* se torna algo evidente e necessário. Como forma de atender a essa demanda, o projeto de computadores pode se apoiar em duas alternativas para aumento de desempenho:

1. Redução do tempo do ciclo de *clock*, principalmente através de melhorias na tecnologia de semicondutores.

2. Melhorias no nível arquitetural, com a concepção de novos mecanismos para permitir a execução de mais instruções por ciclo de *clock*.

A primeira alternativa é algo que se tornou momentaneamente insustentável para a Intel Corp, por exemplo. A companhia passará a adotar um conceito para seus processadores que não prioriza a velocidade do *clock* [15]. Tanto que recentemente desistiu do projeto Tejas (chip antes previsto para o segundo trimestre de 2005, que venceria a barreira de 4 GHz). Especula-se que a decisão ocorreu em meio a preocupações de que os novos processadores estavam sujeitos a superaquecimento devido a gasto excessivo de energia, e consequente obrigatoriedade de sistemas de

refrigeração sofisticados. No mercado de sistemas embarcados, altas freqüências de ciclo de *clock* são ainda mais preocupantes devido ao excessivo consumo de energia.

A segunda alternativa foca todo o esforço em melhorias na implementação da arquitetura do processador. Tais melhorias visam, entre outras coisas, explorar o paralelismo espacial/temporal no nível de instrução, aumentando assim o número de instruções executadas por unidade de tempo através da redução do *CPI - Ciclos por Instrução*.

Soluções voltadas ao processamento paralelo são alternativas arquiteturais a fim de melhorar o desempenho sem aumentar a frequência de operação do processador. Por exemplo, como solução ao problema de superaquecimento, a Intel Corp. passou a apostar nos *chips dual core*, que combinam dois processadores para aumentar o desempenho.

Pela equação de desempenho apresentada a seguir [10] (Equação 1.1), temos que o tempo de um processador para realizar uma tarefa pode ser definido por:

$$\text{Tempo da CPU} = IC * CPI * T \quad (1.1)$$

Onde:

- $IC$  é o número total de instruções executadas;

- $CPI$  é o número médio de ciclos por instrução, e

- $T$  é o tempo médio de um ciclo.

Analizando a Equação 1.1, observa-se que o tempo de execução de um processador pode ser melhorado pela redução do número de instruções necessárias ao cumprimento de uma determinada tarefa. Uma solução seria a concepção de me-

canismos que identifiquem e eliminem a redundância existente em um programa, o qual é objeto de investigação desta pesquisa.

## 1.1 Motivação

Pesquisas recentes vêm contribuindo com novas opções de implementação das arquiteturas existentes de forma a explorar a redundância implícita na execução de programas. Estes estudos sugerem que, durante a execução de um programa, muitas instruções (e grupos de instruções) são executadas repetidamente com as mesmas entradas gerando os mesmo resultados [20, 18]. Sodani e Sohi mostraram que em muitos *benchmarks*, cerca de 80% à 90% das instruções dinâmicas produzem resultados já computados [22]. Isto porque diferentes instâncias de uma mesma instrução estática produzem resultados repetidos se seus operandos são repetidos (no caso comum). Adicionalmente, o resultado de uma instrução pode ser repetido mesmo se seus operandos não o são (e.g. o resultado de uma instrução de comparação pode ser o mesmo com uma ampla variedade de valores de entrada). Entretanto, em alguns casos o resultado de uma instrução pode não ser repetido mesmo sendo verificada a repetição de seus operandos (e.g., uma instrução *load* que lê diferente valores do mesmo endereço de memória).

Sodani e Sohi realizaram uma análise empírica da repetição de resultados, onde foi constatado que, em vários programas a maior parte desta redundância se deve à um pequeno número de instruções estáticas. Utilizando diferentes conjuntos de entrada para a execução dos programas, eles observaram também que a repetição é uma característica de como a computação é expressa em um programa e não uma característica dos valores de entrada como se poderia imaginar [21].

Segundo Lipasti e Shen [14], este fenômeno, denominado *Localidade de Valores*, existe pela forma na qual programas são projetados. Eles observaram também que

em programas tais como ambientes de execução e sistemas operacionais existem várias penalidades de desempenho devido à natureza de propósito geral dessas aplicações. Isto é, programas são implementados para manipular não somente condições excepcionais e entradas inválidas que raramente são encontradas, mas também são freqüentemente projetados com reuso de código. Isto implica diretamente em redundância das instruções que compõem o código de tais programas, o que significa que a maioria das instruções estáticas exibem muito pouca variação nos valores que elas produzem durante o curso da execução de um programa.

Pode-se ilustrar essa situação através do exemplo da Figura 1.1. O método `int busca (int x)` procura pelo valor de um inteiro `x` (chave de busca) no `array vetorDados` de um tamanho `n` qualquer. O método `void main ()` realiza duas chamadas ao método `int busca ()`, pesquisando um elemento diferente no mesmo `array` à cada chamada. Quando o método `int busca (int x)` for chamado, ele acessa elemento por elemento do `array` até encontrar uma correspondência com o valor de `x` ou até que o final do `array` seja alcançado. A Figura 1.1(b) exibe as instruções estáticas em um nível intermediário, referente ao código do método `int busca (int x)`. A Figura 1.1(c) exibe as instruções dinâmicas desse código que são geradas pela primeira chamada ao método `int busca (int x)`. Em cada iteração do loop, a instrução 2 depende do parâmetro `n`, as instruções 3 e 4 dependem do `array vetorDados`, a instrução 5 depende do `array` assim como do valor a ser pesquisado, e a instrução 6 depende da variável de indução. Mesmo se o método `int busca (int x)` for chamado novamente (Figura 1.1(d)) com uma chave de busca diferente da execução anterior, ele pesquisará no mesmo `array` e logicamente no mesmo tamanho `n`. Logo, todas as diferentes instâncias das instruções de 1 à 4 e 6 produzem os mesmos resultados que foram produzidos previamente quando o método `int busca (int x)` foi chamado (um total de `n` instâncias das instruções 2,3,4 e 6). Somente as instâncias da instrução 5 produzem resultados diferentes da última execução do método. O método `int busca (int x)` foi escrito para operar sobre

Figura 1.1: Cenário ilustrando redundância em um programa Java. As instruções dinâmicas marcadas com '\*' realizam a mesma computação para ambas as chamadas ao método `int busca (int x)`

um *array* genérico, mas nesse caso apenas um dos parâmetros (chave de pesquisa) foi alterado entre uma chamada e outra, o que justifica a redundância dos resultados das instruções 1 à 4 e 6. Além disso, mesmo se todos os parâmetros fossem diferentes para a segunda chamada, ainda sim as  $\min(n_1, n_2)$  instâncias da instrução 6 na segunda chamada do método `int busca (int x)`, produziriam a mesma sequência de valores da chamada anterior.

Portanto, a exploração de toda essa computação redundante pode ser uma alternativa arquitetural viável a fim de aumentar o desempenho de novas gerações de processadores. A próxima subseção apresenta o estado da arte na concepção de mecanismo que exploram a computação redundante através do *Reuso de valores* e *Predição de valores*.

## 1.2 Trabalhos Relacionados

Existem dois fatores que limitam a quantidade de paralelismo no nível de instrução que pode ser extraído de programas seqüenciais: *Fluxo de Controle* e *Fluxo de Dados*. O Fluxo de Controle limita o paralelismo pela imposição de serialização nos pontos de desvio e retorno do grafo de fluxo de controle do programa. O Fluxo de Dados limita o paralelismo pela imposição de serialização em pares de instruções que são dependentes de dados (*i.e.* uma instrução necessita do resultado de outra antes de iniciar a execução).

Duas técnicas têm sido propostas para evitar a execução serial de instruções apresentando dependência de dados verdadeira ("RAW - Read After Write"):

- **Predição de valores:** É uma técnica *especulativa* que explora redundância em programas através da predição dos valores que serão produzidos ou usados pelas instruções. Os valores preditos podem ser de três tipos:

- **constant:** onde o mesmo valor ocorre novamente;

- **stride:** onde existe um intervalo fixo entre dois valores subseqüentes;

- **non-stride:** onde existe nenhuma ou uma complexa correlação entre dois valores subseqüentes;

A Figura 1.2 esboça uma simples implementação de predição de valores chamada *Last Value Predictor* [17], que é adequada para o predição de valores do tipo *constant*. Neste caso, o endereço da instrução é utilizado para acessar a tabela de predição, onde o valor da predição está armazenado.

No entanto, o uso do *Last Value Predictor* impede a predição de valores do tipo *stride*, *i.e.*, uma sequência de valores baseados em um valor inicial e com intervalo fixo, tais como: *1, 2, 3, 4, 5, 6, ... ou 1, 3, 5, 7, 9,...* Para efetuar a predição de valores deste tipo, pode-se utilizar o *Stride Predictor* (Figura

Figura 1.2: Técnica de predição de valores - *Last Value Predictor*.

Figura 1.3: Técnica de predição de valores - *Stride Predictor*.

1.3), o qual estende o *Last Value Predictor* pela adição do campo *stride* que contém a diferença, *i.e.*, o intervalo entre os valores da sequência. Uma predição é realizada somando-se o valor do campo *Last Value* com o valor do campo *stride*.

- **Reuso de valores:** É uma técnica *não especulativa* que explora o fato de que muitas instruções ou seqüências de instruções dinâmicas são repetidamente executadas e a maioria destas repetições possuem os mesmos valores de entrada e, assim, geram o mesmo resultado [21]. Técnicas de Reuso de valores exploram este fato através da “buferização” de valores de entradas e seus correspondentes resultados associados à uma instrução ou traço por exemplo. Quando uma instrução ou traço é encontrado novamente e seus valores de entrada atuais correspondem aos valores armazenados no *buffer*, a execução pode ser evitada pois o resultado pode ser obtido do próprio *buffer*. A Figura 1.4 esboça o

Figura 1.4: Técnica de Reuso de valores.

funcionamento da técnica de reuso de valores, onde  $f$ ,  $g$ ,  $h$  e  $i$  representam computações arbitrárias. Antes da execução de cada computação é realizada uma consulta à tabela de memorização utilizando um identificador qualquer da computação e o respectivo valor de entrada. Em caso de falha, a instância da computação é inserida. Caso contrário, o resultado é obtido da tabela e a computação deixa de ser executada.

### 1.2.1 Explorando a redundância através de Reuso de valores

Como forma de explorar a redundância através de Reuso de valores no nível de instruções, Sodani e Sohi [20] propuseram um mecanismo próprio para implementação em *hardware* denominado *Dynamic Instruction Reuse*, que memoriza instruções dinâmicas, *i.e.*, valores dos operandos de entrada e resultado, buscando oportunidades de reusar estes resultados. Além disso, eles também fizeram uma estimativa de qual a percentagem de redundância apresentada em programas que pode ser capturada pelo mecanismo *Dynamic Instruction Reuse* [22].

Utilizando outra abordagem, da Costa [2] e da Costa *et al.* [3] propõem o reuso no nível de traços de instruções, dando origem ao mecanismo *DTM - Dynamic Trace Memoization*, o qual busca memorizar e reusar traços de instruções redundantes em

uma arquitetura superescalar de 3 operandos do tipo RISC, reduzindo (i) o número de instruções executadas, (ii) desvios previstos incorretamente e (iii) os caminhos críticos determinados por dependências verdadeiras.

Gonzalez *et al.* apresentaram um estudo do potencial de reuso de instruções e traços. Para isso, eles definiram uma estrutura de memorização denominada *Reuse Trace Memory (RTM)*, que armazena informações sobre os traços selecionados idealmente para posterior reuso. Eles também apresentaram os limites superiores para redundância e aceleração que podem ser explorados pelo reuso de traços [9].

Todas as pesquisas relatadas têm como alvo uma arquitetura de 3 operandos do tipo RISC. Programas Java compilados para *bytecodes*<sup>1</sup> são diferentes de programas C compilados para uma arquitetura RISC porque (i) eles são altamente orientados à objetos com muitas chamadas de métodos ligados dinamicamente, e (ii) são compilados para uma arquitetura baseada em pilha. A fim de investigar o comportamento do mecanismo DTM sobre a arquitetura Java e avaliar seu impacto no desempenho devido ao item (ii), Silva *et al.* [19] propuseram uma variação do mecanismo DTM, dando origem ao mecanismo *JDTM - Java Dynamic Trace Memoization*, que memoriza e reusa dinamicamente traços de *bytecodes* Java compilados para uma arquitetura de processador Java que executa *bytecodes* nativamente.

### 1.2.2 Explorando a redundância através de Predição de valores

Lipasti e Shen [14], visando ultrapassar os limites do Fluxo de Dados devido à serialização de seqüências de instruções dependentes de dados, exploraram a Localidade de Valores no contexto de predição de valores através de execução especulativa. Desta forma, instruções dependentes podem iniciar a execução evitando aguardar que seus operandos de entrada sejam produzidos por instruções anteriores na sequê-

---

<sup>1</sup>Os termos instrução e bytecode serão usados indistintamente neste trabalho.

cia de execução.

### 1.2.3 Semelhanças e diferenças entre Reuso de valores e Predição de valores

Ambas as técnicas buscam reduzir o tempo de execução de programas pela redução das restrições impostas pelo Fluxo de Dados. Para isso, elas usam a redundância em programas para determinar especulativamente (Predição de valores) ou não-especulativamente (Reuso de valores) o resultado de instruções sem executá-las. A vantagem é que as instruções não precisam esperar pela conclusão das “instruções produtoras” para iniciarem a execução. Elas podem executar mais cedo usando os resultados obtidos pelas duas técnicas acima, reduzindo, assim, as restrições do fluxo de dados.

A abordagem de Reuso de valores não é especulativa e, portanto, é mais conservadora. Por exemplo, se os valores dos operandos de entrada de uma instrução ou traço não estiverem disponíveis a tempo do teste de reuso, tal instrução ou traço não será reusado; ou, uma instrução que produz o mesmo resultado mas com diferentes entradas (por exemplo, operações lógicas e *loads*), também não serão identificados por tal abordagem. Porém, Predição de valores pode fazer previsões corretas para cada caso, visto que essa técnica não depende dos valores de entrada estarem disponíveis, nem serem os mesmos da última execução. Logo, o Reuso de valores captura menos redundância em programas do que Predição de valores. Porém, o Reuso de valores não impõe penalidades devidas à previsões incorretas. Além do mais, na abordagem de Predição de valores, as instruções precisam de qualquer forma serem executadas para confirmar ou não a especulação. No caso do Reuso de valores, as instruções reusadas não necessitam ser executadas, reduzindo assim a demanda por recursos do processador e o número total de instruções executadas.

Uma abordagem híbrida tira proveito dos benefícios de ambas as técnicas. Esse

é o caso da abordagem de Pilla *et al.* [17], onde é proposto e avaliado um mecanismo implementado em *hardware* capaz de realizar predição de valores para reuso de traços através de especulação. *Reuse through Speculation on Traces (RST)* [16], como foi chamado, aumenta o reuso de traço e oculta dependências verdadeiras pela combinação de Predição de valores e Reuso de valores. RST possibilita que traços sejam *regularmente reusados*, quando todos os valores de entrada estão disponíveis e correspondem com os valores armazenados no *contexto de entrada do traço*, ou *especulativamente reusados* quando existem valores ainda não conhecidos no contexto de entrada de um traço. Além disso, traços que não poderiam ser reusados em outras abordagens podem ser reusados explorando sua previsibilidade e não somente sua redundância.

#### 1.2.4 Outros Trabalhos

RST, assim como DTM e JDTM não inclui instruções de acesso à memória nos traços construídos, evitando problemas de inconsistência com a memória de dados. Uma variação do mecanismo DTM foi apresentada por Viana [4], onde essa classe de instruções pode ser inclusa nos traços construídos e reusados. Da mesma forma, uma variação do mecanismo RST foi apresentada por Laurino *et al.* [13], onde instruções de leitura de dados da memória (*loads*) são inseridas no conjunto de instruções válidas para serem utilizadas na construção e consequente reuso especulativo dos traços.

## 1.3 Objetivos e contribuições

Este trabalho examina o reuso de computação redundante (Reuso de valores) no contexto de aplicações embarcadas Java através de um mecanismo implementado em *hardware* que memoriza e reusa dinamicamente traços de *bytecodes* Java.

Além do impacto no desempenho do processador que incorpora tal mecanismo, é objetivo dessa investigação identificar:

- O percentual de instruções reusadas. Ou seja, o percentual de reuso exposto pelo mecanismo;

- A distribuição percentual do número de instruções encapsuladas nos traços reusados;

- As melhores opções em termos de tamanho e associatividade das tabelas de memorização utilizadas pelo mecanismo;

- A distribuição percentual do número de valores no contexto de entrada e saída dos traços reusados;

- A distribuição do número de instruções de desvios realizados encapsulados nos traços reusados;

- As instruções que limitam o tamanho dos traços construídos;

- Trabalhos futuros a serem realizados no contexto de exploração de redundância em aplicações embarcadas Java.

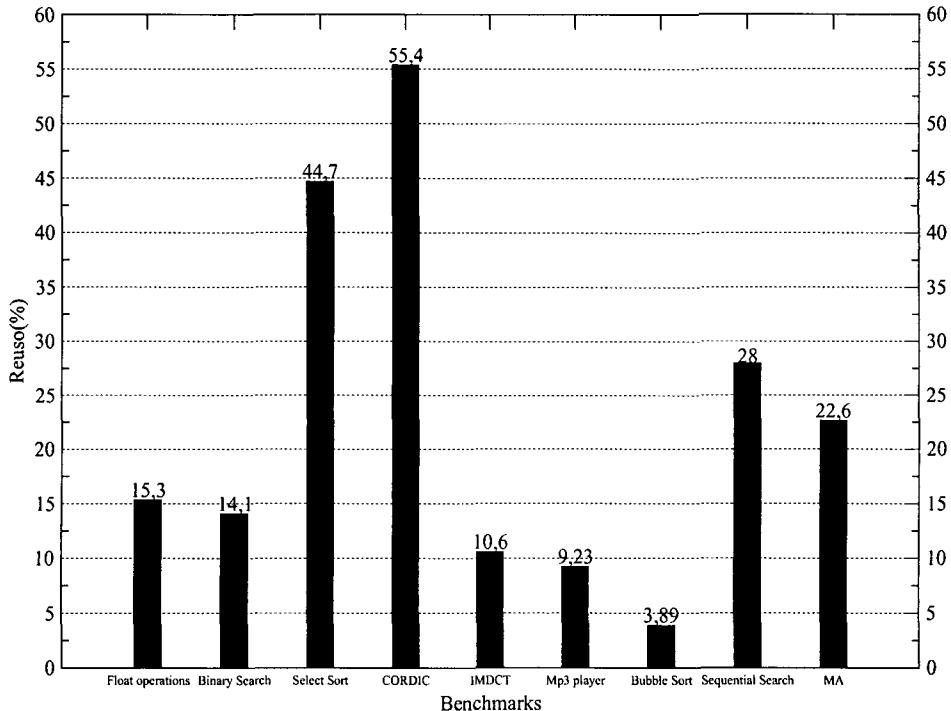

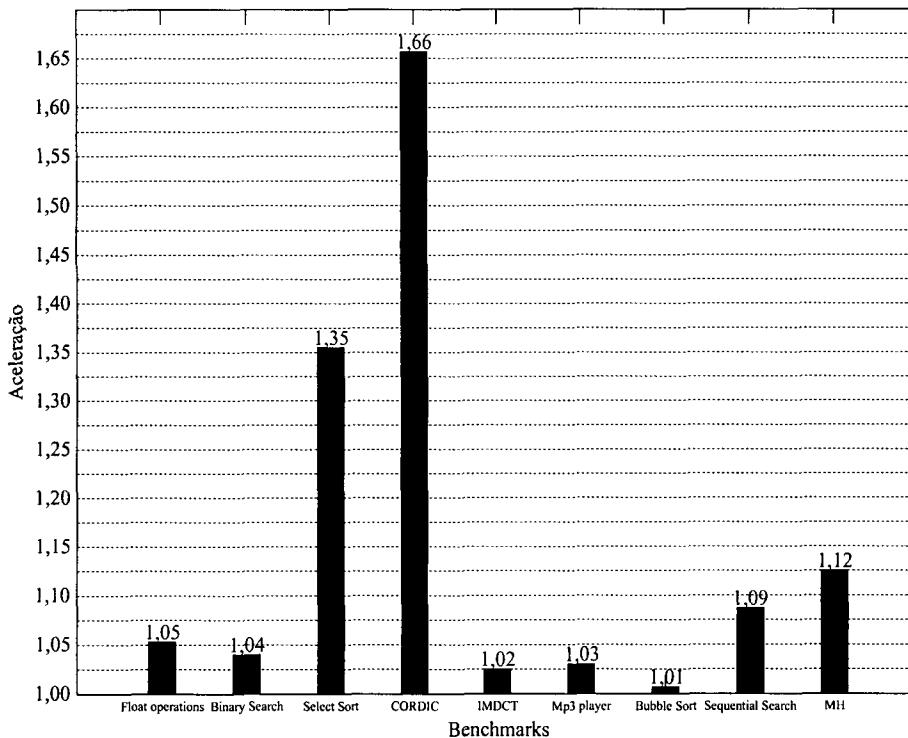

O mecanismo de memorização e reuso de traços de *bytecodes* proposto neste trabalho possibilitou, em média, um percentual de reuso de 22% dos *bytecodes* executados em 8 *benchmarks* típicos de sistemas embarcados, o que provocou um incremento, em média harmônica, de 12% no desempenho do processador substrato. Este trabalho realizou também um estudo sobre a sensibilidade do mecanismo à variações no tamanho e na associatividade das tabelas de memorização, bem como identificou a melhor relação custo/benefício em se tratando do número de entradas das duas tabelas de memorização utilizadas pelo mecanismo.

## 1.4 Estrutura do Trabalho

Este trabalho está dividido em 5 partes. A primeira parte compreende o presente capítulo introdutório com a motivação da pesquisa, trabalhos relacionados e objetivo. O Capítulo 2 apresenta o conhecimento de fundo, descrevendo de forma resumida (i) o mecanismo DTM como foi originalmente desenvolvido por da Costa [2], (ii) a arquitetura do processador utilizado como substrato para a implementação da solução proposta neste trabalho e (iii) o simulador ciclo-a-ciclo utilizado na realização dos experimentos. A terceira parte é composta pelo Capítulo 3, onde é apresentada a solução encontrada para memorização e reuso de traços de *bytecodes*. Neste, é apresentado o mecanismo *JDTM* (*Java Dynamic Trace Memoization*) e suas principais diferenças em relação ao mecanismo DTM. O Capítulo 4 descreve os experimentos e a análise dos resultados obtidos. Por fim, o último capítulo aborda as principais conclusões e os possíveis trabalhos futuros.

# Capítulo 2

## *Background*

O presente capítulo apresenta a base de conhecimento usada no desenvolvimento desta pesquisa. Para tanto é descrita a arquitetura do processador *FemtoJava Low Power 32 bits* [6] utilizado como processador substrato para a implementação do JDTM, bem como o simulador *CACO-PS* [7] utilizado nos experimentos. Também é apresentado o mecanismo *Dynamic Trace Memoization*, como foi originalmente desenvolvido para a arquitetura MIPS [10].

### 2.1 Processador FemtoJava

#### 2.1.1 FemtoJava multiciclo 8 bits

Nos dias atuais Java é uma das tecnologias mais populares no ambiente de aplicações embarcadas. A maioria dos aparelhos celulares modernos suportam Java, assim como outros sistemas embarcados (*personal digital assistants* e *pgers*, por exemplo).

Visando explorar o crescente mercado de sistemas embarcados, Ito *et al.* [12] apresentam uma nova estratégia de projeto para implementação de aplicações em-

barcadas descritas unicamente em Java, de forma à manter a compatibilidade de *software* durante todo o processo de projeto. Além disso, o *hardware* destino de tais aplicações é um único *chip FPGA* (*Field Programmable Gate Array*), devido ao seu baixo custo e fácil reconfiguração.

Esta nova estratégia baseia-se em um ambiente de projeto para aplicações específicas através da geração de processadores Java. Neste ambiente, denominado *SASHIMI* (*Systems As Software and Hardware In Microcontrollers*), o projetista fornece uma aplicação Java para ser analisada e otimizada para execução em um *ASIP* (*Application Specific Instruction Set Processor*), somado à um *ASIC* (*Application Specific Integrated Circuit*) opcional, ambos sintetizados em um único *chip FPGA*. Esta abordagem é também caracterizada pela alta integração de funções, ambiente de execução simplificado, nenhuma necessidade de um novo compilador e compatibilidade de *software*.

Para dar suporte ao SASHIMI no nível de *hardware*, foi projetado um processador Java *multiciclo de 8 bits* chamado *FemtoJava*, que executa *bytecodes* nativamente [11]. Este processador, destinado à execução de aplicações específicas do mercado de sistemas embarcados, possui uma arquitetura *Harvard* de pilha com conjunto de instruções reduzido e pequeno tamanho. A ferramenta SASHIMI realiza uma análise dos *bytecodes* de uma aplicação e gera a unidade de controle do FemtoJava, através de uma descrição em *VHDL* (*VHSIC Hardware Description Language*), suportando somente as instruções usadas pela aplicação. Conseqüentemente, o tamanho da unidade de controle é diretamente proporcional ao número de instruções diferentes usadas.

### Por que usar uma arquitetura de Pilha?

Máquinas de pilhas são conhecidas pelo seu mecanismo de execução simplificado. Estas máquinas não codificam informações dos operandos na palavra de instrução, resultando em um código mais compacto e portável visto que elas necessitam de uma

menor quantidade de *bits* para codificar uma instrução e não são tão dependentes da organização do banco de registradores. Vale mencionar que programas compilados para máquinas *RISC* (*Reduced Instruction Set Computer*) podem ser 1.5 à 2.5 vezes maiores que suas versões compiladas para máquinas *CISC* (*Complex Instruction Set Computer*) [11]. Além disso, o programa de uma máquina de pilha pode ser 2.5 à 8 vezes menor que o mesmo programa compilado para uma máquina *CISC* [11].

Atualmente várias soluções focadas em sistemas embarcados possuem excessivos recursos para atender: *RTOS* (*Real Time Operating System*); implementações específicas da *JVM* (*Java Virtual Machine*); suporte *multithreading* e *garbage collector*. Entretanto, para muitas aplicações embarcadas simples, estes mecanismos impõem grande *overhead*, relativo ao custo de implementação e potência. Para estas aplicações mais simples, é necessário desconsiderar possíveis críticas quanto ao desempenho da arquitetura de pilha e avaliar a sua capacidade em atender as necessidades de aplicações específicas.

Alguns benefícios, problemas e questões abertas no uso de processadores baseados em uma arquitetura de pilha para suportar execução nativa de *bytecodes* Java, são discutidos em por Ito *et al.* [11].

### 2.1.2 Breve descrição de alguns *bytecodes* Java

Ao contrário de máquinas *RISC* ou *CISC* que possuem uma arquitetura orientada a acumulador ou a registrador, Java possui uma arquitetura orientada a pilha. Logo, o modelo de programação é um pouco diferente de outros modelos presentes em processadores mais comuns como *MIPS*, *Intel x86* e outros que se baseiam em transferência de valores entre registradores. Esta subseção visa descrever de forma sucinta, através de um exemplo de código Java, alguns dos 201 *bytecodes* disponíveis no conjunto de instruções da arquitetura Java.

Na Figura 2.1 pode-se observar duas seqüências de instruções para a operação  $C = A + B$ , uma para uma arquitetura do tipo *load-store*, e outra para uma arquitetura de pilha, assumindo que os valores das variáveis  $C$ ,  $A$  e  $B$  estão inicialmente em memória.

Figura 2.1: Sequência de instruções para a operação  $C = A + B$  em uma arquitetura *load/store*(a) e uma arquitetura de pilha (b).

Como pode ser observado, na arquitetura *load/store* (Figura 2.1(a)), os valores das variáveis  $A$  e  $B$  precisam ser lidos da memória utilizando a instrução *load*, e armazenados em registradores temporários ( $R1$  e  $R2$  respectivamente). O resultado da instrução *add R3, R1, R2* precisa ser escrito de volta na memória, através da instrução *store*<sup>1</sup> que utiliza o registrado  $R3$  como fonte.

Na arquitetura de pilha (Figura 2.1(b)), os valores também precisam ser lidos da memória, porém o destino destes valores já está implícito na própria instrução *getstatic*. Este destino é o topo de uma pilha que pode, inclusive, ser mapeada em um banco de registradores. Em seguida, a instrução *add* desempilha os dois últimos valores empilhados, realiza uma operação de soma e empilha o resultado. Assim, como na arquitetura *load/store*, o resultado empilhado precisa ser escrito de volta na memória, para isso usa-se a instrução *putstatic*.

Esta pilha, na realidade, é chamada de pilha de operandos (do inglês *operand stack*).

<sup>1</sup>Na arquitetura *load/store*, instruções da classe aritméticas e lógicas não podem possuir operandos em memória.

*stack*). É necessário ressaltar a diferença do nome pois, além da pilha de operandos, o processador Java também faz uso da pilha para desempenhar outras funções, entre elas guardar<sup>2</sup> os valores das variáveis automáticas, isto é, das variáveis locais do método, além de guardar informações de retorno para os métodos que foram invocados, como também ocorre em outros processadores que não implementam uma pilha de operandos.

Como pode ser observado na Figura 2.2, que exibe uma pilha típica que pode ser implementada em um processador Java, a passagem de parâmetros de um método A para um método B é facilitada através da intercalação da pilha de operandos do método A com o início do *pool* de variáveis locais do método B. Ou seja, o método A pode passar parâmetros ao método B, simplesmente empilhando estes parâmetros em sua pilha de operandos e informando ao método B quantos parâmetros estão sendo passados. Assim, o método B pode iniciar seu pool de variáveis locais justamente em uma posição da pilha que inclua os valores empilhados pelo método A.

Figura 2.2: Organização da pilha de um processador Java típico.

A versão multiciclo do FemtoJava implementa a pilha na memória de dados, porém a versão *pipeline* do FemtoJava, que será descrita na próxima subseção, faz uso do banco de registrados para a implementação da pilha, mas a fim de reduzir a

<sup>2</sup>A área da pilha, reservada para essa função é chamada de *pool de variáveis locais*.

Tabela 2.1: Instruções suportadas pelo processador FemtoJava.

| Classe                      | <i>Bytecodes</i>                                                                                                                                                     |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aritméticas e lógicas       | iinc, iadd, isub, iand, ior, ixor, ineg, ishl, ishr, iushr, idiv, irem, imul                                                                                         |

| Controle de fluxo           | ifeq, ifne, iflt, ifge, ifgt, ifle, if_icmp eq, if_icmp ne, if_icmp lt, if_icmp ge, if_icmp gt, if_icmp le, return, ireturn, areturn, invokestatic, if_acmp ne, goto |

| <i>Load/Store</i>           | iload, iload_0, iload_1, iload_2, iload_3, istore, istore_0, istore_1, istore_2, istore_3, aload, aload_0, aload_1, aload_2, aload_3                                 |

| Operações de Pilha          | iconst_m1, iconst_0, iconst_1, iconst_2, iconst_3, iconst_4, iconst_5, bipush, sipush, pop, pop2, dup, dup2, dup_x2                                                  |

| Acesso à Memória            | iaload, aaload, baload, caload, saload, arraylength, ldc, ldc_w, getstatic, putstatic, bastore, iastore                                                              |

| Nops e operações estendidas | nop, load_idx, store_idx, sleep                                                                                                                                      |

área do processador, ele continua guardando na memória de dados as informações de retorno de métodos, pois essas são pouco requisitadas e portanto o acesso a elas não impõem uma redução muito alta do desempenho e um aumento do consumo de potência.

A unidade de controle da versão *pipeline* do FemtoJava implementa um subconjunto de 76 instruções Java. Neste subconjunto encontram-se instruções necessárias para operações lógicas e aritméticas de inteiros, desvios condicionais e incondicionais, execução de métodos estáticos, *load/store* de variáveis locais, operações básicas de pilha, acesso à memória, e operações estendidas (não inclusas na ISA original do Java). Este subconjunto pode ser observado na Tabela 2.1. Os *bytecodes* estendidos são necessários para executar instruções de E/S, programação de interrupções e também para colocar o processador em modo suspenso. O processador FemtoJava só pode executar código de classes (isto é, não pode alocar objetos dinamicamente) porque seu conjunto de instruções apenas suporta os *bytecodes* `invokestatic`, `return`, `areturn` e `ireturn` como instruções para manipulação de métodos.

### Um exemplo

Na Figura 2.3 pode-se observar o código Java de um algoritmo de pesquisa sequencial que verifica se um valor de entrada *x* está presente em um vetor de entrada *v*, retornando a posição deste valor no vetor ou -1 caso *x* não seja encontrado. A Classe *sequencial* possui 3 campos estáticos: *vetorDados*, *n* e *posicao*, correspondendo respectivamente à um *array* de 10 posições, um inteiro que possui o tamanho do *array* e o último sendo um campo que armazenará o resultado da pesquisa. A classe possui três métodos estáticos:

1. **void main ()**: método principal necessário para a execução de um aplicativo Java. Este método instancia um objeto da classe *sequencial* e realiza uma chamada ao método **void initSystem()**.

2. **void initSystem ()**: este método realiza uma pesquisa no vetor através de uma chamada ao método **int busca(int x)**, passando o valor 55 como argumento. O valor de retorno do método **int busca(int x)** será armazenado no campo *posicao*.

3. **int busca(int x)**: é neste método que está localizado o algoritmo de pesquisa sequencial que utiliza uma estrutura de repetição para acessar todas as posições do vetor, a fim de verificar se pelo menos um dos valores armazenados neste *array* corresponde ao valor do argumento (valor da variável local *x*). O algoritmo retorna a primeira posição (valor da variável local *i*) do vetor que corresponde ao valor procurado ou retorna -1 caso não seja encontrada correspondência.

Como resultado da compilação deste código Java, é gerado um arquivo *.class* contendo o código de máquina que pode ser executado por uma JVM. Visto que o processador FemtoJava necessita que este código possua um formato específico, este arquivo compilado precisa ser analisado e adaptado para posteriormente ser

```

1 class Sequencial {

2     static int vetorDados[] = {4, 5, 1, 3, 0, 23, 8, 7, 6, 55};

3     static int n = 10;

4     static int posicao;

5

6     public static int busca (int x) {

7         int i;

8         for (i=0; i<n; i++) {

9             if (x==vetorDados[i]) return i;

10        }

11        return -1;

12    }

13    public static void initSystem() {

14        posicao = busca(55);

15    }

16    public static void main(String[] argv) {

17        Sequencial seq = new Sequencial();

18        Sequencial.initSystem();

19    }

20 }

```

Figura 2.3: Algoritmo de pesquisa sequencial implementado em Java.

utilizado como programa de entrada para o processador FemtoJava. A fim de automatizar este processo, a ferramenta SASHIMI, utilizando como entrada o programa compilado (arquivo *.class*), realiza um análise sobre os *bytecodes* certificando-se que todas as instruções pertencem à ISA do processador. Caso a análise identifique que o programa utiliza apenas as instruções inclusas na ISA, ou seja, não utiliza instruções de alocação dinâmica de memória e nem instruções de ponto flutuante, o SASHIMI fornece como saída, dois arquivos no formato<sup>3</sup> *MIF (Memory Initialization File)*. Estes arquivos possuem respectivamente o conteúdo da memória de instruções (*ROM - Read Only Memory*) e de dados (*RAM - Random Access Memory*).

A Figura 2.4 exibe o conteúdo do arquivo MIF de memória de instruções, que neste caso possui os *bytecodes* do programa Java da Figura 2.3. Este arquivo utiliza o sistema de numeração hexadecimal e possui basicamente um conjunto de linhas no seguinte formato:

---

<sup>3</sup>Aceito pelo ambiente *Maxplus-II* da Altera Corporation [1].

endereço : opcode; - mnemônico

Vale mencionar que a memória de instruções é endereçada por *bytes* e cada palavra de dado possui 1 *byte* no caso do FemtoJava multiciclo 8 *bits* ou 4 *bytes* no caso do FemtoJava *Low Power 32 bits*.

```

-- MAX+plus II - Memory Initialization File - generated by SASHIMI CAD Tool

-----+

| WIDTH = 8;

| DEPTH = 128;

| ADDRESS_RADIX = HEX;

| DATA_RADIX = HEX;

CONTENT BEGIN

0 : b8; -- invokestatic

1 : 00; --

2 : 49; --

. . . .

. . . .

. . . .

2b : 01; -- Sequencial.busca.(I)I.2

2c : 01; --

2d : 03; -- iconst_0

2e : 3c; -- istore_1

2f : 1b; -- iload_1

30 : b2; -- getstatic

31 : 00; --

32 : 10; --

33 : a2; -- if_icmpge

34 : 00; --

35 : 12; --

36 : 1a; -- iload_0

37 : b2; -- getstatic

38 : 00; --

39 : 11; --

-----+

| 3a : 1b; -- iload_1

| 3b : 2e; -- iaload

| 3c : a0; -- if_icmpne

| 3d : 00; --

| 3e : 03; --

| 3f : 1b; -- iload_1

| 40 : ac; -- ireturn

| 41 : 84; -- iinc

| 42 : 01; --

| 43 : 01; --

| 44 : a7; -- goto

| 45 : ff; --

| 46 : e9; --

| 47 : 02; -- iconst_m1

| 48 : ac; -- ireturn

| 49 : 00; -- Sequencial.initSystem.()V.0

| 4a : 00; --

| 4b : 10; -- bipush

| 4c : 37; --

| 4d : b8; -- invokestatic

| 4e : 00; --

| 4f : 2b; --

| 50 : b3; -- putstatic

| 51 : 00; --

| 52 : 1e; --

| 53 : b1; -- return

-----+

```

Figura 2.4: Memória de instruções do FemtoJava multiciclo 8 *bits* contendo os *bytewcodes* do algoritmo de pesquisa sequencial mostrado na Figura 2.3.

A Figura 2.5 exibe o conteúdo do arquivo MIF de memória de dados, que neste caso possui os dados estáticos do programa Java da Figura 2.3. Este arquivo também utiliza o sistema de numeração hexadecimal e possui um conjunto de linhas no seguinte formato:

endereço : dados; - comentário

A memória de dados do FemtoJava é endereçada por palavra, onde cada palavra possui 4 bytes de informação.

```

-- MAX+plus II - Memory Initialization File -

generated by SASHIMI CAD Tool

WIDTH = 16;

DEPTH = 32;

ADDRESS_RADIX = HEX;

DATA_RADIX = HEX;

CONTENT BEGIN

0 : 00; -- reserved

. . .

f : 00; -- reserved

10 : 0a; -- Sequencial.n

11 : 12; -- Sequencial.vetorDados

12 : 0a; -- Sequencial.vetorDados.length

13 : 04; -- Sequencial.vetorDados[0]

14 : 05; -- Sequencial.vetorDados[1]

15 : 01; -- Sequencial.vetorDados[2]

16 : 03; -- Sequencial.vetorDados[3]

17 : 00; -- Sequencial.vetorDados[4]

18 : 17; -- Sequencial.vetorDados[5]

19 : 08; -- Sequencial.vetorDados[6]

1a : 07; -- Sequencial.vetorDados[7]

1b : 06; -- Sequencial.vetorDados[8]

1c : 37; -- Sequencial.vetorDados[9]

1d : 00; --

1e : 00; -- Sequencial.posicao

1f : 00; -- no value

END;

```

Figura 2.5: Memória de dados do FemtoJava contendo os dados estáticos do algoritmo de pesquisa sequencial mostrado na Figura 2.3.

Pode-se observar que o programa da Figura 2.4 possui 21 *bytecodes*, dos quais 16 são distintos. A função de cada um destes *bytecodes* é descrita abaixo:

1. **invokestatic indexbyte1 indexbyte2**: Realiza uma chamada à um método estático endereçado por  $sign\_ext16((indexbyte1 \ll 8) | indexbyte2)$ . Onde  $sign\_ext16$  significa extensão de sinal em um número de 16 bits.

2. **iconst\_0**: Empilha a constante 0 na pilha de operandos.

3. **istore\_1**: Desempilha um valor do topo da pilha de operandos e o armazena na variável local 1.

4. **iload\_1**: Carrega o valor da variável local 1 e o empilha na pilha de operandos.

5. **getstatic indexbyte1 indexbyte2**: Carrega o valor de uma posição da memória de dados, endereçada por  $sign\_ext16((indexbyte1 \ll 8) | indexbyte2)$ , e o empilha na pilha de operandos.

6. **if\_icmpge offsetbyte1 offsetbyte2**: Desempilha dois valores da pilha de operandos. Se o sub-topo é maior ou igual ao topo, faz um desvio relativo ao PC para endereço  $sign\_ext16((offsetbyte1 \ll 8) | offsetbyte2)$  da memória de instruções.

7. **iload\_0**: Carrega o valor da variável local 0 e o empilha na pilha de operandos.

8. **iaload**: Desempilha dois valores da pilha de operandos e carrega o valor de uma posição da memória de dados, endereçada por  $sub-topo + topo$ , empilhando este valor na pilha de operandos.

9. **if\_icmpne offsetbyte1 offsetbyte2**: Desempilha dois valores da pilha de operandos. Se o valor do sub-topo é diferente do valor do topo, faz um desvio relativo ao PC para endereço  $sign\_ext16((offsetbyte1 \ll 8) | offsetbyte2)$  da memória de instruções.

10. **ireturn**: Retorno de método. Desempilha um valor da pilha de operandos do método atual e o empilha na pilha de operandos do método invocador. Sai do contexto do método atual através da recuperação das informações de retorno de métodos, armazenadas na memória de dados.

11. **iinc index const**: Incrementa o valor da variável local  $index$  somando  $const$  ao seu valor.

12. **goto offsetbyte1 offsetbyte2**: Realiza um desvio incondicional para a instrução endereçada por  $PC + sign\_ext16((offsetbyte1 \ll 8) | offsetbyte2)$ .

13. **iconst\_m1**: Empilha a constante -1 na pilha de operandos.

14. **bipush byte**: Empilha o imediato  $byte$  na pilha de operandos.

15. **putstatic** *indexbyte1 indexbyte2*: Desempilha um valor da pilha de operandos e o armazena em uma posição, endereçada por  $sign\_ext16((indexbyte1 \ll 8) | indexbyte2)$ , da memória de dados.

16. **return**: Retorno de método. Sai do contexto do método atual através da recuperação das informações de retorno de métodos armazenadas na memória de dados.

### 2.1.3 FemtoJava *Low Power 32 bits*

Como mencionado, para suportar a execução nativa de um subconjunto das instruções da arquitetura Java, Ito *et al.* [11] desenvolveram um processador multiciclo de 8 *bits* chamado FemtoJava. Entretanto, visto que a pilha deste processador é implementada em memória, acessos à pilha são acompanhados de um grande consumo de potência. Visando reduzir este consumo, Beck Filho e Carro [6] propõem uma nova versão do processador FemtoJava, denominada FemtoJava *Low Power*, e Gomes *et al.* [8] apresentaram uma implementação deste processador em VHDL.

FemtoJava *Low Power* é um processador *pipeline* de 32 *bits* que executa *bytecodes* Java nativamente e possui a pilha de operandos e o *pool* de variáveis locais mapeados em um banco de registradores, ao contrário do FemtoJava multiciclo que utiliza a memória de dados como meio de armazenamento dessas estruturas.

A Figura 2.6 exibe a pilha do processador FemtoJava *Low Power* implementada em um banco de 64 registradores, que armazena a pilha de operandos e o *pool* de variáveis locais. Vale mencionar que nenhum cuidado é tomado pelo processador ou compilador em se tratando de um possível estouro de pilha. Entretanto, para os *benchmarks* considerados e suas respectivas entradas utilizadas neste trabalho não houve estouro de pilha.

Com um *pipeline* de cinco estágios, este processador alcança maior desempenho

Figura 2.6: Organização da pilha do processador FemtoJava *Low Power*.

e menor consumo de potência, com um pequeno *overhead* de área ocupada, se comparado à versão multiciclo.

Na Figura 2.7 pode-se observar a sequência dos 5 estágios do *pipeline*, que serão detalhados abaixo:

Figura 2.7: Os cinco estágios do *pipeline* do FemtoJava *Low Power*.

1. IF - *Instruction Fetch* ou Busca de Instruções: Este estágio é composto por uma fila de instruções de 9 registradores de 1 byte cada (fila de *prefetch*), um registrador para endereçar a memória de instruções (IMAR) e um somador para gerar o endereço da próxima instrução sequencial. Se um endereço não sequencial precisar ser carregado, um multiplexador copia o valor armazenado

no registrador contador de programa (PC) para o registrador IMAR e todas as instruções na fila são desconsideradas. Quando pelo menos 4 posições da fila estiverem livres, uma palavra de 32 bits é buscada da memória de instruções<sup>4</sup>.

2. **ID** - *Instruction Decode* ou Decodificação de instrução: Neste estágio é realizada a geração da palavra de controle para a instrução que está na primeira posição da fila e informa o tamanho desta instrução ao estágio IF, de forma que a próxima instrução seja deslocada para a primeira posição da fila. Isto é necessário visto que as instruções possuem tamanho variado: elas podem ter 0, 1 ou dois operandos imediatos.

3. **OF** - *Operand Fetch* ou Busca de operandos: Neste estágio é realizada a busca dos valores dos operandos em um banco de registradores de tamanho variável, definido *a priori* nos primeiros estágios do projeto do ASIP. A pilha de operandos e o *pool* de variáveis locais dos métodos estão disponíveis no banco de registradores. Além disso, existem dois registradores reservados: SP e VARS. Eles apontam para o topo da pilha de operandos e para o início do *pool* de variáveis locais respectivamente. Dependendo da instrução, um deles é usado como base para a busca de operandos. Uma vez que os operandos são buscados, eles são enviados ao quarto estágio, onde serão usados pela instrução na devida unidade funcional.

4. **EX** - *Execution* ou Execução: Compreende 5 unidades funcionais a saber: 1 unidade de cálculo de endereços de memória (*load/store*), 1 unidade de multiplicação de inteiros, 1 unidade lógica e aritmética de inteiros, 1 unidade de desvios e 1 unidade de deslocamento. Operações de ponto flutuante são executadas por *software* através de bibliotecas aritméticas, pois o processador FemtoJava não possui unidades de ponto flutuante visto que destina-se à sistemas embarcados. Não existe predição dinâmica de desvios, portanto todos os

---

<sup>4</sup>O processador FemtoJava não possui *memória cache*.

desvios condicionais são previstos como não realizados. Se é constatado neste estágio que o desvio deveria ter sido realizado, todas as entradas da fila de instruções são removidas e as instruções nos estágios anteriores desconsideradas, resultando em uma penalidade de 3 ciclos de *clock*.

5. **WB - Write Back** ou Escrita de resultados: Este estágio armazena no banco de registradores, se necessário, o resultado do estágio de execução usando o registrador SP ou o registrador VARS como base. O banco de registradores não pode ser simultaneamente lido e escrito, logo, uma bolha é inserida no *Pipe* caso uma instrução no quinto estágio tente escrever enquanto outra no terceiro espera ler.

FemtoJava *Low Power* explora o paralelismo temporal no nível de instruções através da técnica de *pipeline*, o que lhe garante um melhor uso de seus recursos de *hardware*. Pois sem a execução em *pipeline*, partes de seu *datapath* não seriam utilizadas em um certo ciclo de *clock*. Entretanto, problemas de dependências verdadeiras (*RAW - Read After Write*) são encontrados quando uma instrução no estágio EX possui o resultado necessário à uma instrução seguinte no estágio OF. FemtoJava trata esse problema através da técnica de *forwarding*, passando diretamente o resultado do estágio EX para o estágio OF. Em processadores baseados em pilha, o uso de tal técnica é mais vantajoso do que em arquiteturas *load-store*, visto que em instruções que manipulam a pilha de operandos, o operando recebido por *forwarding* não será mais necessário. Como consequência, uma vez que o valor foi passado por *forwarding* à instrução dependente, não existe a necessidade da instrução que produziu tal operando escrevê-lo na pilha. A instrução *dup* que duplica o valor do topo da pilha de operandos é uma exceção, pois mesmo que seu operando seja obtido por *forwarding*, a instrução que o produz deve armazená-lo na pilha, visto que a instrução *dup* não destrói o operando por ela utilizado.

Dois tipos de *forwarding* podem ocorrer: quando a instrução no estágio OF

precisa buscar 1 operando do topo da pilha (como *istore* que armazena o topo da pilha em algum lugar do *pool* de variáveis locais); ou quando a instrução necessita de dois operandos da pilha (como operações aritméticas: *iadd*, *isub*, *ior*). No primeiro caso, o operando é obtido do estágio EX. No segundo caso, o segundo operando é obtido do estágio WB.

A técnica de *forwarding* também é válida para escritas no *pool* de variáveis locais. Ou seja, se uma instrução no estágio EX produz o valor de uma variável do *pool* e outra no estágio de OF necessita ler a mesma variável, o operando da última é obtido por *forwarding* do estágio EX. Do mesmo modo, se uma instrução em WB irá escrever (no próximo ciclo) em uma variável do *pool* e uma instrução em OF necessita obter o valor dessa mesma variável, tal valor é obtido por *forwarding* do estágio WB.

Devido à técnica de *forwarding* houve uma melhor utilização das unidades funcionais por causa de redução das paradas do *pipeline* que ocorrem em consequência de dependências verdadeiras, além de um redução significativa do número de escritas no banco de registradores. Logo, esta implementação do FemtoJava alcançou redução no consumo de potência por ciclo além de melhor desempenho quando comparada à versão multiciclo. O consumo de potência total gasto na execução de uma aplicação também foi reduzido, visto que o número de ciclos total é menor na execução em *pipeline* [5].

## 2.2 Simulador CACO-PS

A fim de validar a técnica JDTM, este trabalho fez uso do simulador CACO-PS [7, 5] que pode ser instrumentado para fornecer informações quantitativas a respeito da descrição de uma arquitetura alvo. Neste trabalho, foi simulada a arquitetura do processador FemtoJava *Low Power 32 bits*, com e sem o mecanismo JDTM.

CACO-PS é um simulador configurável de código compilado, que estima a potência de uma arquitetura baseado em ciclos de *clock*. Apesar de ser um simulador de código compilado, ele oferece a possibilidade da descrição estrutural de qualquer arquitetura em diferentes níveis de abstração.

Basicamente, três arquivos são necessários para uma descrição completa da arquitetura:

1. Descrição da arquitetura em uma sintaxe definida pelo simulador;

2. Descrição em linguagem C dos componentes funcionais;

3. Descrição em linguagem C de um modelo de cálculo de potência para cada componente funcional instanciado na descrição da arquitetura.

A arquitetura é descrita por um conjunto de declarações de componentes, onde cada um contém sinais de entrada, comportamento funcional e sinais de saída. O componente recebe os sinais de entrada, executa seu comportamento funcional sobre esses sinais e retorna o resultado nos sinais de saída.

Os componentes podem ter qualquer granularidade, como por exemplo: multiplexadores, portas lógicas, ULA (Unidade Lógica e Aritmética), transistores, memórias ou até mesmo processadores inteiros. O nível de abstração é definido pelo projetista da arquitetura. Os componentes podem ter seu comportamento funcional e modelo de potência descritos em linguagem C. Vale mencionar que, uma vez especificado o comportamento funcional e o modelo de potência de um componente, estes podem ser reusados na descrição de outra arquitetura.

### 2.2.1 Descrição da arquitetura e simulação

Uma arquitetura deve ser descrita em um arquivo texto, que possua um conjunto de linhas no seguinte formato:

```

Input1,...,InputN -> component id (x,y,..., z:control) -> Output1,...,OutputN

```

Onde `Input1`, ..., `InputN` são os sinais que serão usados como entrada para o componente. Para cada componente, um identificador (`id`) é necessário. Considerando que um componente pode ser instanciado mais que uma vez, o `id` é usado para diferenciar uma instância de outra. Finalmente, o componente é controlado pelos sinais de controle `x`, `y` e `z`, se necessário. O resultado final retornado pelo componente é propagado para `Output1`, ..., `OutputN`.

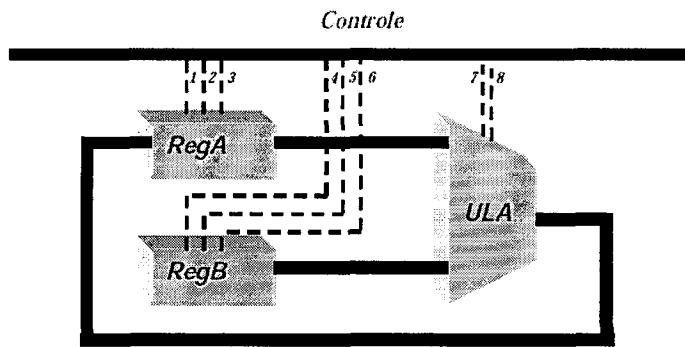

A Figura 2.8 exibe 3 componentes (`RegA`, `RegB` e `ULA`). O sinal de controle possui 8 bits. Os bits 0, 1 e 2 controlam o registrador `RegA`. Os bits 3, 4 e 5 controlam o registrador `RegB`. Finalmente, os bits 6 e 7 controlam a `ULA` [5].

Figura 2.8: Exemplo de uma microarquitetura alvo.

Os bits que controlam os registradores são usados para acionar os comandos de `enable`, `set` e `reset` do registrador, respectivamente. Os bits de controle da `ULA` indicam as operações: 00 - soma, 01 - subtração, 10 - *and*, 11 - *or*. A Figura 2.9 exibe o exemplo da Figura 2.8 na sintaxe do CACO-PS [5].

Para o exemplo da Figura 2.8 é necessário descrever o comportamento funcional de dois componentes (Registrador e ULA). Pode-se observar na Figura 2.10 a descrição em linguagem C de um registrador de 16 bits onde, a cada borda de subida do `clock` (linha 5), é verificado se o sinal de controle `enable` está habilitado (linha 6).

|                   |                               |             |

|-------------------|-------------------------------|-------------|

| regA_out,regB_out | -> ula exemplo (6,7:controle) | -> regA_in  |

| regA_in           | -> reg A (0,1,2:controle)     | -> regA_out |

| regB_in           | -> reg B (3,4,5:controle)     | -> regB_out |

Figura 2.9: Descrição de uma microarquitetura alvo na sintaxe do CACO-PS.

Caso positivo, a função `ADICIONA_VALOR` grava o valor do sinal de entrada (linha 7). De forma assíncrona, as linhas 10 e 11 verificam se os sinais de controle *set* e *reset* estão desabilitados (lógica inversa) respectivamente. A linha 12 fornece o valor do registrador no ciclo atual.

```

1. COMPONENTE("reg") {

2.   // enable = controle[0];

3.   // set = controle[1];

4.   // reset = controle[2];

5.   if (clock_event == 1) {

6.     if (controle_atual[0] == 1) {

7.       ADICIONA_VALOR(input_atual[0]&MASK);

8.     }

9.   }

10. if (controle[1] == 0) ADICIONA_VALOR(0xffffffff);

11. if (controle[2] == 0) ADICIONA_VALOR(0x0000);

12. output[0] = (PEGA_VALOR & MASK);

13. }

```

Figura 2.10: Descrição do comportamento funcional de um registrador de 16 bits (de Beck Filho [5]).

Quando o projetista constrói o comportamento de um componente, existe uma abstração dos sinais de entrada e saída. Quando o componente é instanciado na descrição da arquitetura, o simulador efetua a ligação dos sinais de entrada e saída da instância do componente aos sinais conectados como entrada e saída para aquele componente.

Cada componente pode possuir um modelo de cálculo de potência baseado na frequência de chaveamento do *bits* do sinal de entrada. Para uma descrição razoável desse modelo é necessário uma descrição VHDL no nível de portas do componente em questão. Entretanto, é importante mencionar que este trabalho não incorpora

resultados de estimativas de potência do JDTM.

Para executar a simulação de uma arquitetura qualquer, quatro arquivos são necessários: Descrição do comportamento funcional dos componentes, arquivo de descrição da arquitetura, e o conteúdo das memórias ROM e RAM em formato MIF (opcionais).

## 2.3 DTM - Dynamic Trace Memoization

### 2.3.1 Introdução

O mecanismo de memorização e reuso dinâmico de traços de *bytecodes* Java, que será apresentado no próximo capítulo, baseia-se no mecanismo *DTM (Dynamic Trace Memoization)*, o qual pode ser definido como uma técnica [2] que busca memorizar seqüências de instruções dinâmicas, *i.e.*, traços de instruções e realizar o reuso do conjunto de resultados produzidos por estes traços quando possível.

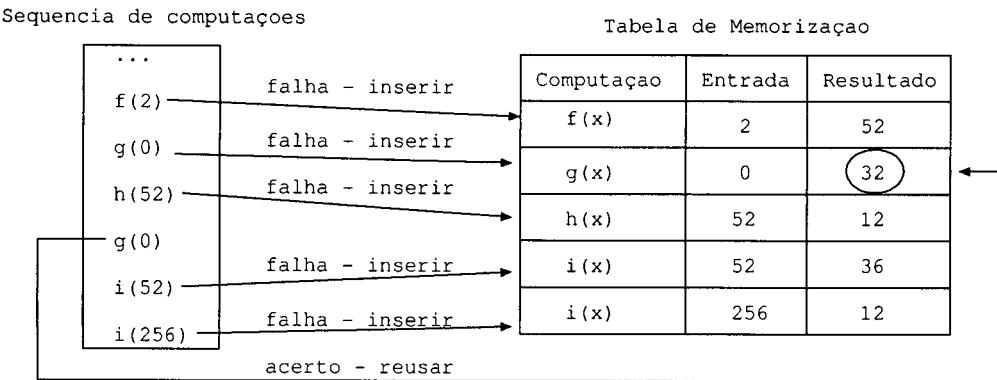

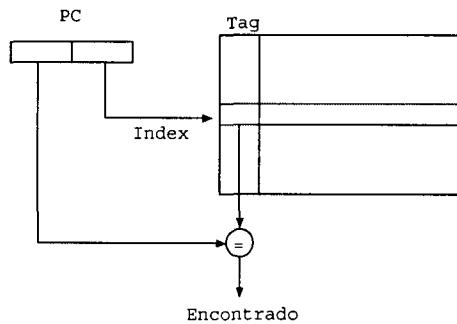

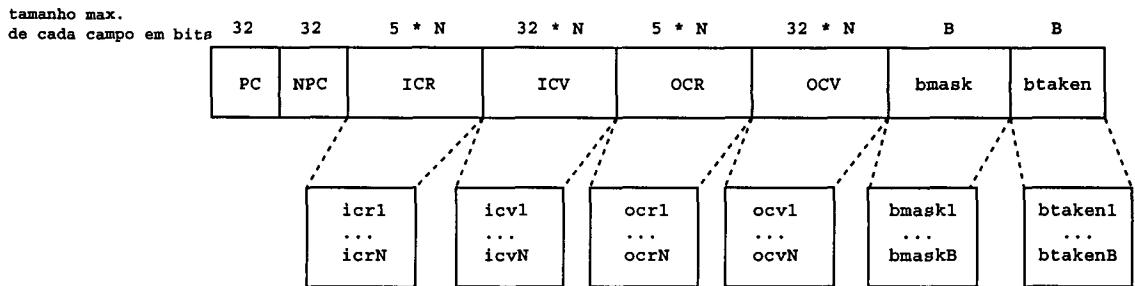

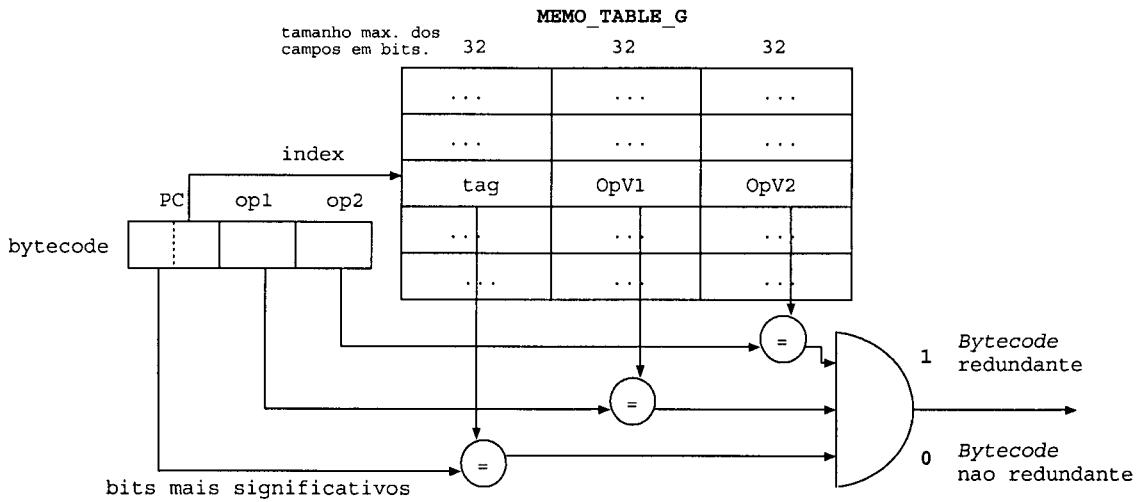

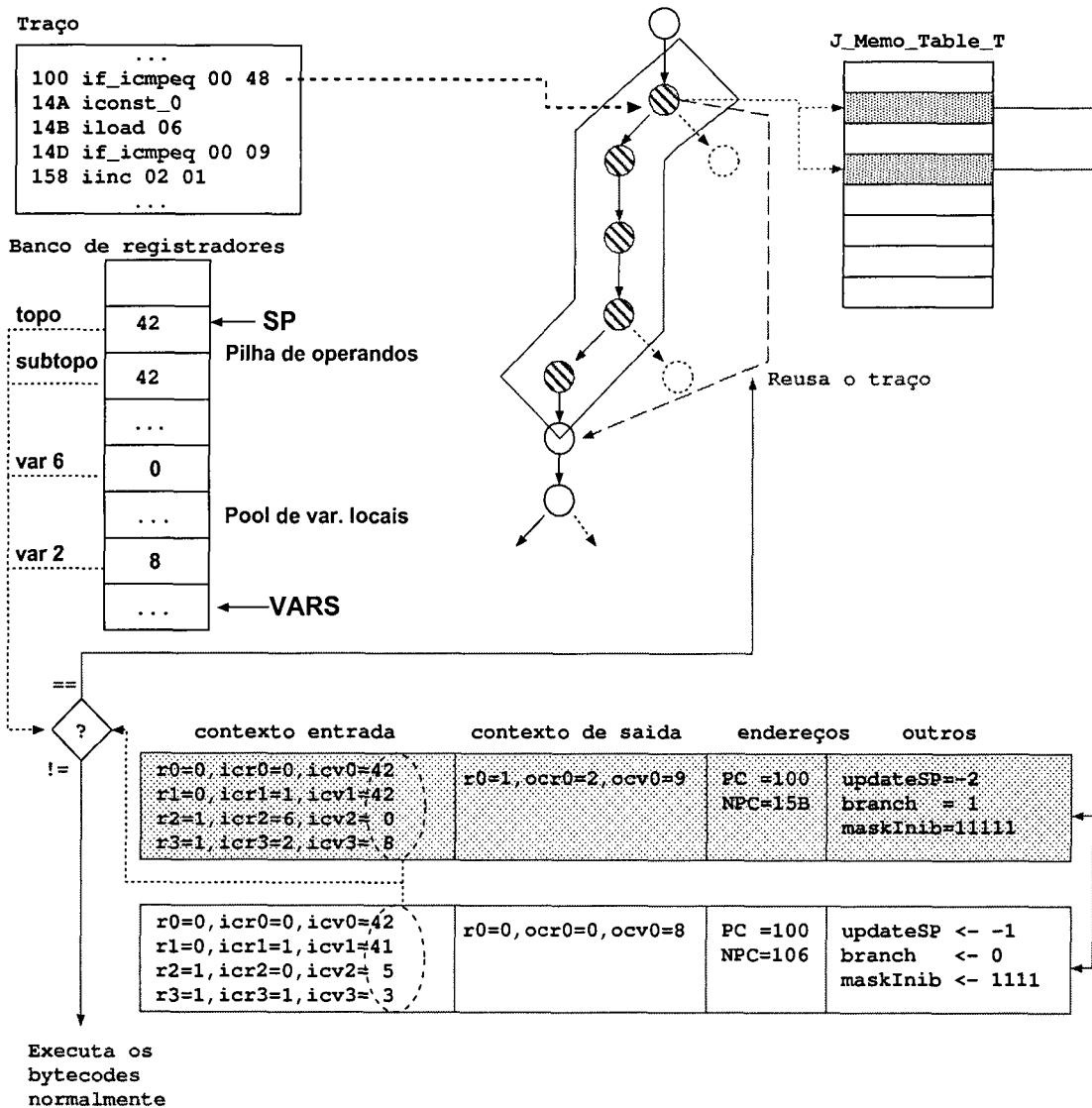

Este mecanismo faz uso de duas tabelas de memorização, implementadas em *hardware* e indexadas pelo valor do registrador PC (Figura 2.11): *Memo\_Table\_G - Tabela de Memorização Global* e *Memo\_Table\_T - Tabela de Memorização de Traços*. O uso de duas tabelas fornece ao mecanismo dois níveis de reuso, o primeiro nível é utilizado no reuso de instruções simples e na construção de traços de instruções, enquanto o outro é responsável pelo reuso de traços de instruções.

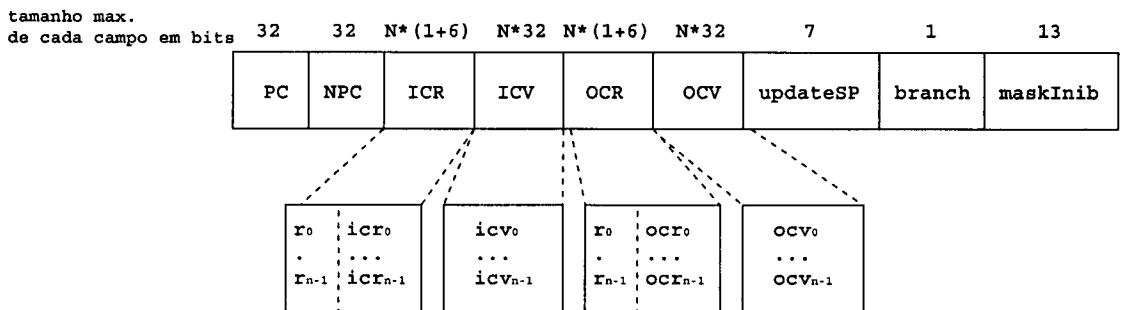

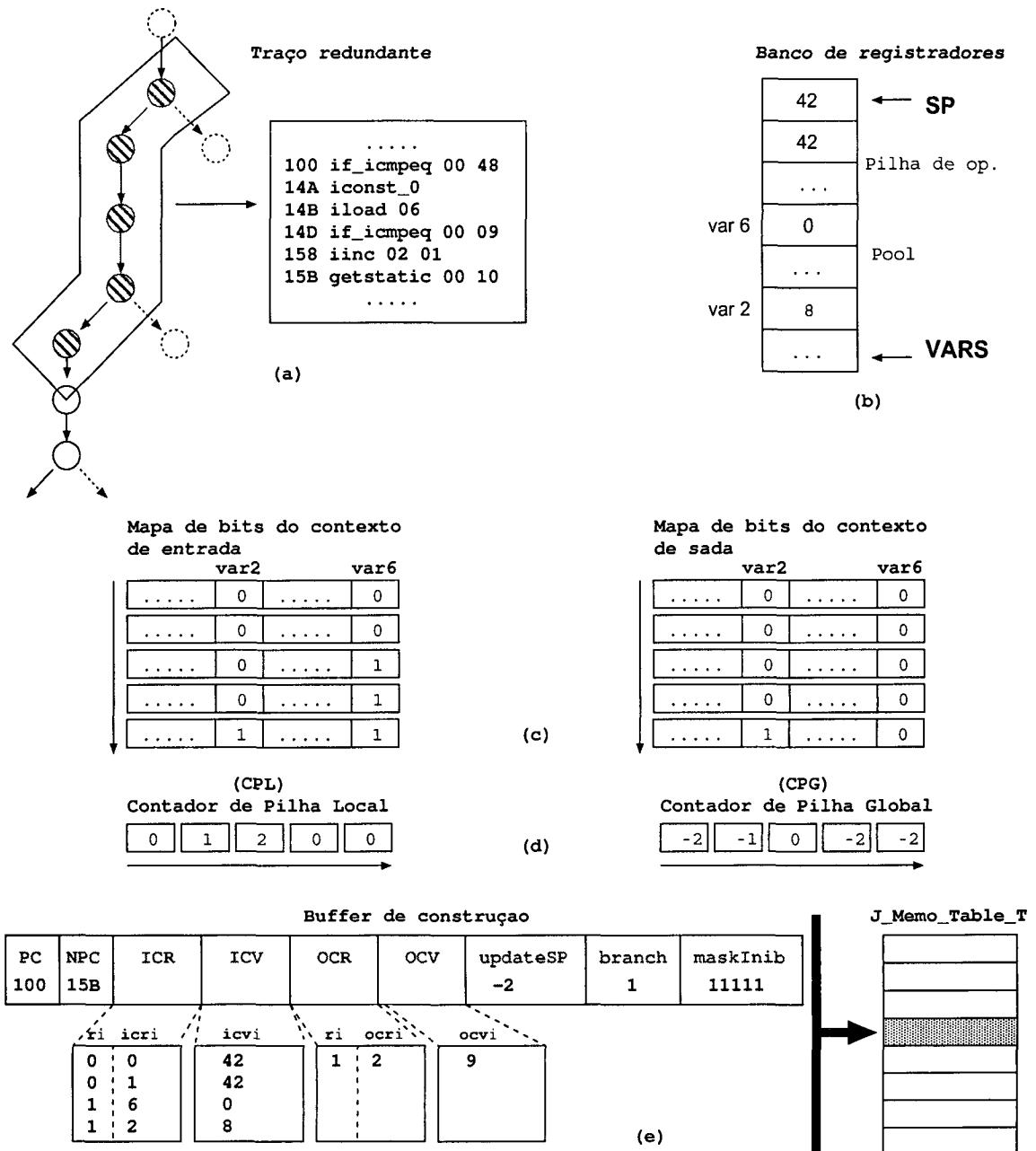

A tabela *Memo\_Table\_G* basicamente armazena em cada entrada: (i) parte do endereço de memória de uma instrução dinâmica; (ii) os operandos fontes e os valores a eles instanciados e (iii) o resultado produzido pela execução da instrução. A tabela *Memo\_Table\_T* basicamente armazena em cada entrada: (i) parte do endereço de memória da primeira instrução de um traço construído dinamicamente, *i.e.*, em tempo de execução; (ii) o endereço de memória da próxima instrução a ser executada

Figura 2.11: Procedimento utilizado para indexar quaisquer das tabelas de memoização.

para o caso em que o traço seja futuramente reusado; (iii) o conjunto de operandos fontes e valores a eles instanciados que foram utilizados como operandos de entrada para as instruções que compõem o traço e (iv) o conjunto de operandos de destino e seus respectivos valores produzidos pelas instruções pertencentes ao traço.

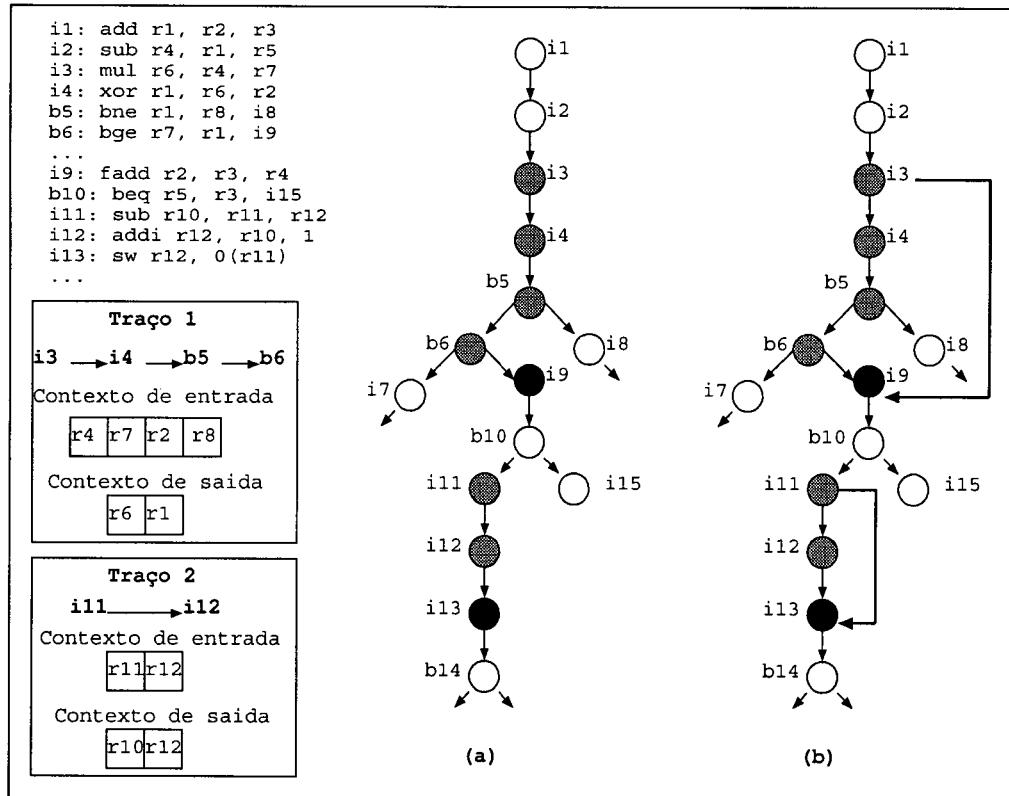

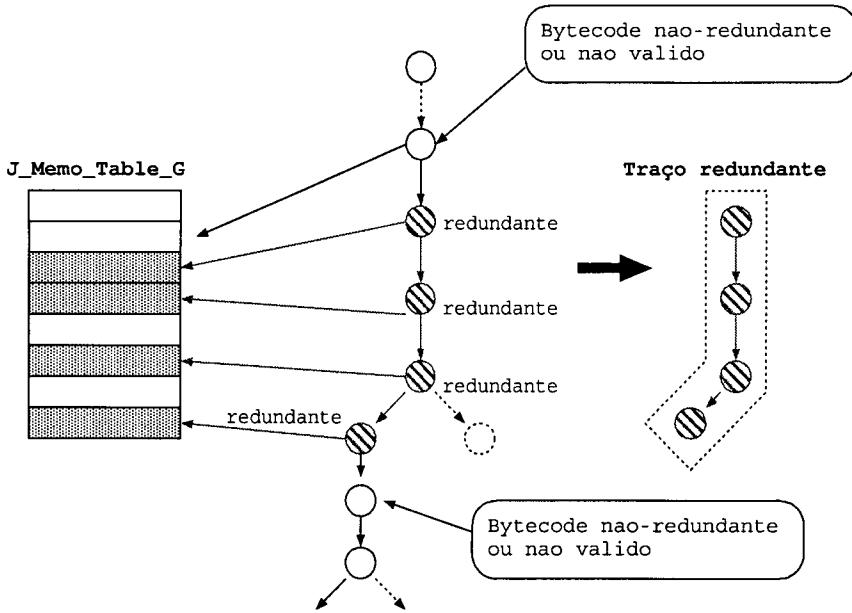

A construção dos traços que serão memorizados é realizada com base na identificação de *instruções redundantes* simples, que são instruções dinâmicas instanciadas com os mesmos valores de seus operandos de entrada observados em uma execução anterior desta instrução, o que portanto faz com que estas instruções, se executadas, produzam o mesmo resultado observado na execução anterior. A identificação de uma instrução redundante é feita por uma consulta à tabela Memo\_Table\_G, em busca de uma entrada desta tabela que corresponda à instância desta instrução.

Instruções cujas instâncias sejam encontradas na tabela Memo\_Table\_G, não serão executadas, visto que o resultado destas instruções já está disponível na tabela, bastando apenas *reusá-lo*. Para isso, faz-se necessário atualizar o estado do processador através da escrita deste resultado no banco de registradores, bem como o repasse para possíveis instruções que estão a espera deste resultado (instruções dependentes). A instância de uma instrução que não é encontrada em Memo\_Table\_G, será memorizada nesta tabela na esperança de que a próxima vez que tal instrução seja executada, sua nova instância corresponda à instância memorizada e consequen-

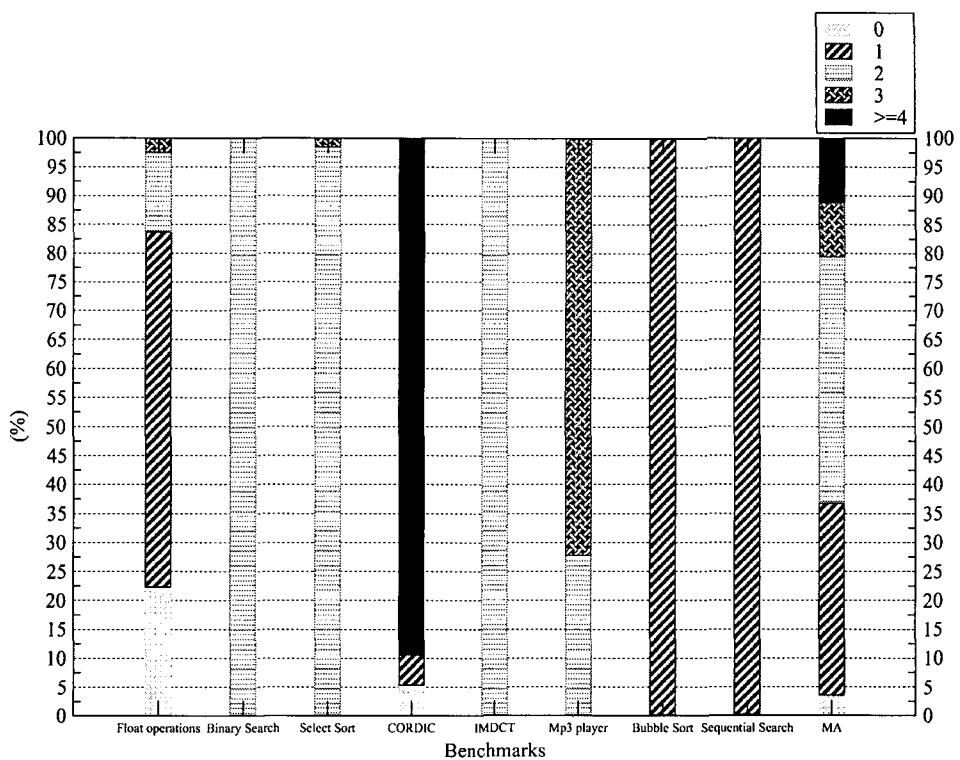

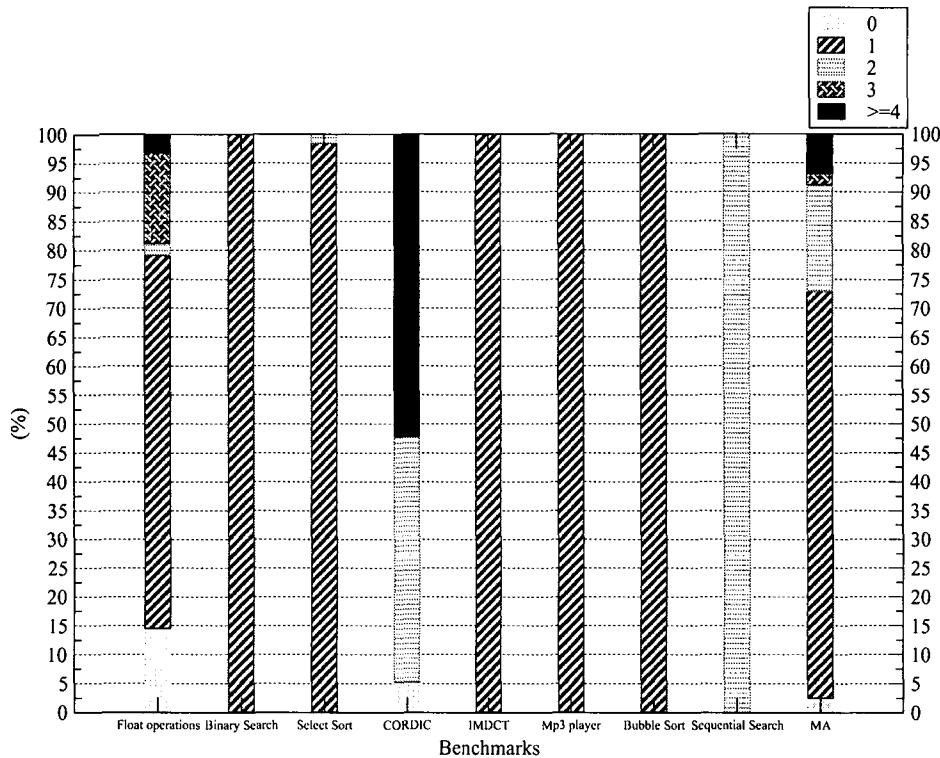

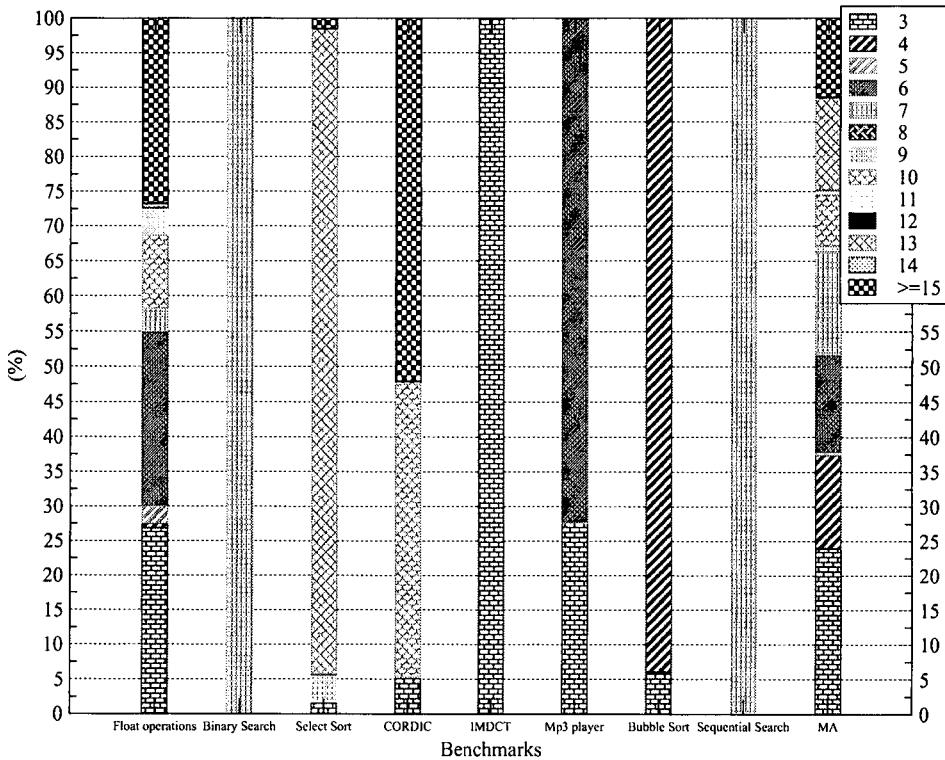

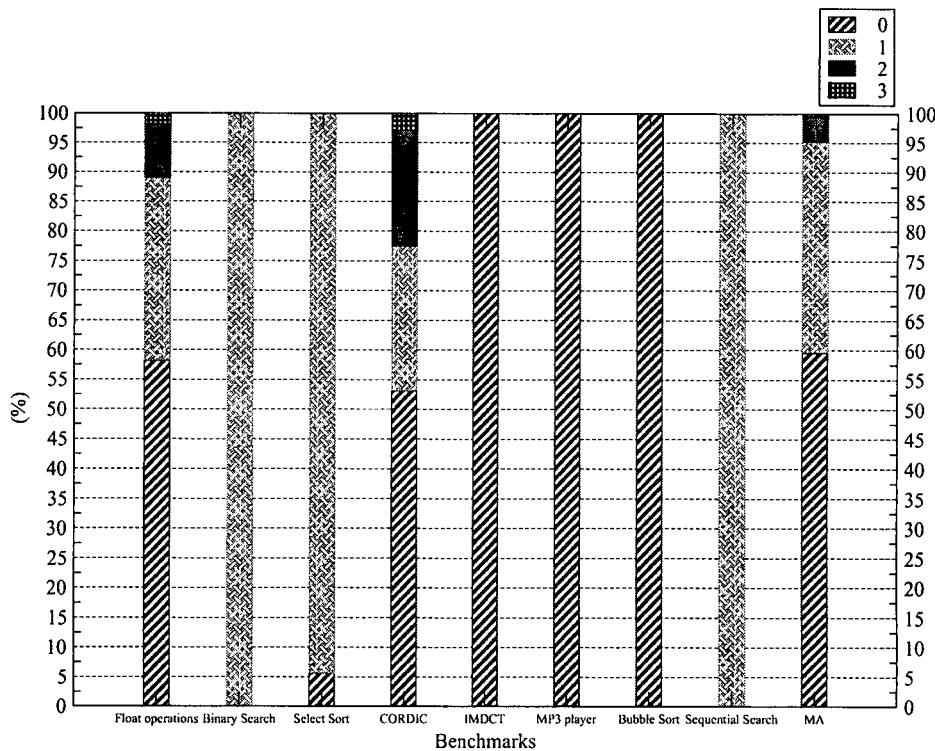

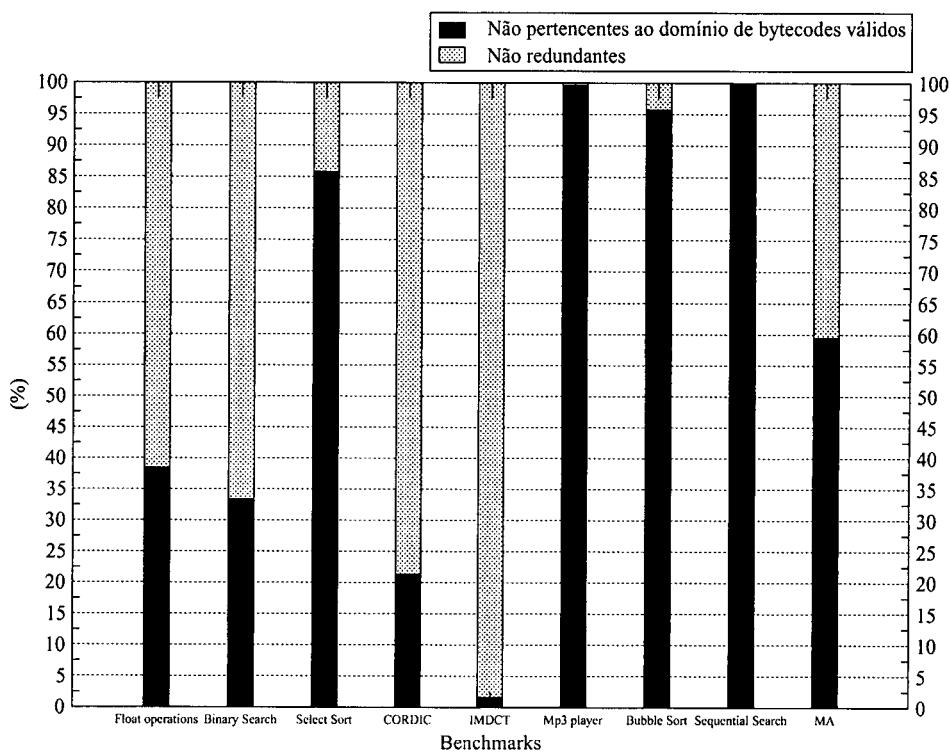

temente seja identificado um resultado redundante.