UM ESTUDO DOS PROTOCOLOS DE COERÊNCIA PARA SISTEMAS

LÓGICOS PARALELOS

Eduardo Pereira Gaspar de Oliveira

TESE SUBMETIDA AO CORPO DOCENTE DA COORDENAÇÃO

DOS PROGRAMAS DE PÓS-GRADUAÇÃO DE ENGENHARIA DA

UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS

REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE MESTRE

EM CIÊNCIAS EM ENGENHARIA DE SISTEMAS E COMPUTAÇÃO.

Aprovada por:

---

Prof. Inês de Castro Dutra, Ph.D.

Prof. Maria Clicia Stelling de Castro, D.Sc.

---

Prof. Cláudio Luis de Amorim, Ph.D.

---

Prof. Anna Dolejsi Santos, D.Sc.

---

Prof. Cristiana Bentes, D.Sc.

RIO DE JANEIRO, RJ - BRASIL

FEVEREIRO DE 2005

OLIVEIRA, EDUARDO PEREIRA

GASPAR DE OLIVEIRA

Um Estudo dos Protocolos de Coerência

para Sistemas Lógicos Paralelos [Rio de

Janeiro] 2005

XII, 70 p. 29,7 cm (COPPE/UFRJ, M.Sc.,

Engenharia de Sistemas e Computação, 2005)

Tese – Universidade Federal do Rio de

Janeiro, COPPE

- 1 - Protocolos de coerência

- 2 - Memória compartilhada distribuída

- 3 - Hardware DSM

- 4 - DASH

I. COPPE/UFRJ II. Título (série)

*À minha querida mãe e meu querido irmão*

# Agradecimentos

Agradeço a minha mãe Luci, presente nos momentos difíceis a me confortar, aconselhar e auxiliar. Perante os problemas apresentados na vida continuou lutando arduamente para o meu bem estar e sucesso, assim como o do meu irmão. Não estariamos aqui sem sua mão a nos guiar. Pelo carinho, força e determinação dedicada a nós e que nos inspira só tenho a agradecer de ter nascido seu filho.

Agradeço ao meu irmão Alberto, que primeiro trilhou as estradas e assegurou-me caminhos mais tranquilos. Com a perda de nosso pai se fez responsável por parte de meu desenvolvimento. Só tenho a agradecer de ter um irmão, padrinho e amigo, cada qual de forma singular, em uma só pessoa que está ao meu lado desde o meu nascimento.

Agradeço a minha namorada Luana pelo apoio, inspiração e compreensão às minhas faltas, tanto necessárias ao desenvolvimento deste trabalho.

Agradeço a minha orientadora Inês, que me apresentou novos caminhos na ciência, indicando os passos necessários a percorrê-los. Agradeço por escutar-me e instruir-me diante das idéias, algumas destas mirabolantes, a serem executadas.

Agradeço a minha co-orientadora Maria Clícia que junto a Inês integrou-se na tarefa de orientar-me.

Agradeço ao meu pai, avós e entes queridos hoje presentes em outro plano, mas prontos a nos auxiliar.

Agradeço a Paulo Rezende, Celso Rossi e demais integrantes da equipe Infomarket pelo apoio oferecido ao desenvolvimento deste trabalho.

Agradeço ao Antônio Branco, Doris Ferraz de Aragon (in memorian), Luiz Cláudio da Silva Leão e demais integrantes do ILTC que auxiliaram no início desta conquista.

Agradeço a Deus por deixar participar de meu caminho todas as pessoas citadas anteriormente e pelos auxílios dispensados para efetuar este percurso.

Resumo da Tese apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Mestre em Ciências (M.Sc)

## UM ESTUDO DOS PROTOCOLOS DE COERÊNCIA PARA SISTEMAS LÓGICOS PARALELOS

Eduardo Pereira Gaspar de Oliveira

Fevereiro/2005

Orientadores: Inês de Castro Dutra

Maria Clicia Stelling de Castro

Programa: Engenharia de Sistemas e Computação

Modelos de programação lógica têm características que o tornam a solução mais adequada para determinados problemas. Alguns destes ligados a áreas de grande importância, por exemplo, a de Biotecnologia, que muitas vezes exigem alto poder computacional.

Este modelo também tem a vantagem de permitir que suas aplicações sejam executadas em arquiteturas paralelas de forma implícita ao desenvolvedor, isto é, sem alterações no código fonte, ao contrário de aplicações desenvolvidas em outros modelos como o de programação funcional ou imperativa. Este paralelismo implícito é aproveitado através de *frameworks* que administram os recursos da arquitetura paralela.

Arquiteturas paralelas, entretanto, têm uma série de parâmetros estruturais que influenciam o desempenho das aplicações executadas sobre ela. O protocolo de coerência de memória é um dos fatores mais significativos.

Este trabalho avalia o comportamento de algumas aplicações lógicas em arquiteturas paralelas de acordo com os protocolos de coerência de memória, complementando trabalhos anteriores e sendo mais uma referência no assunto.

Nossos resultados mostram que protocolos híbridos melhoram o desempenho de sistemas paralelos de programação lógica em até 80%, produzindo *speedups* de até 11,6 em 16 processadores, quando comparados com protocolos de invalidação, normalmente utilizados nos processadores atuais.

Abstract of Thesis presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Master of Science (M.Sc.)

A STUDY OF HYBRID COHERENCE PROTOCOLS FOR PARALLEL LOGIC PROGRAMMING SYSTEMS

Eduardo Pereira Gaspar de Oliveira

February/2005

Advisors: Inês de Castro Dutra

Maria Clicia Stelling de Castro

Department: Computing and Systems Engineering

The logic programming model has characteristics that are suitable to solve problems in some areas of great importance, such as Biotechnology. In these areas, finding a solution requires, in general, a high computational power.

This model brings the advantage of being declarative, which makes the control not completely explicit, and allows for implicit parallelisation. This implicit parallelism is captured by frameworks that extract the available parallelism and manage the resources of a parallel architecture.

Parallel architectures have various parameters that can affect the performance of the applications. One of the most important, specially in modern architectures, is the memory coherence protocol.

This work evaluates the behaviour of applications in parallel logic programming systems running on a scalable architecture, and study different cache coherence protocols. Our results show that hybrid protocols can improve the performance of parallel logic programming systems by 80%, achieving speedups of 11.6, with 16 processors, over invalidate-based protocols commonly used in current multiprocessors.

# Sumário

|          |                                                          |           |

|----------|----------------------------------------------------------|-----------|

| <b>1</b> | <b>Introdução</b>                                        | <b>1</b>  |

| <b>2</b> | <b>Arquiteturas Paralelas</b>                            | <b>6</b>  |

| 2.1      | Arquiteturas de computadores . . . . .                   | 6         |

| 2.2      | Modelos de consistência . . . . .                        | 12        |

| 2.3      | Modelos de programação . . . . .                         | 14        |

| 2.4      | Problemas associados a multiprocessadores . . . . .      | 16        |

| 2.5      | Classes de coerência de memória . . . . .                | 17        |

| 2.6      | Protocolos de coerência de memória . . . . .             | 18        |

| 2.6.1    | Invalidação ( <i>invalidate</i> ) . . . . .              | 18        |

| 2.6.2    | Atualização ( <i>update</i> ) . . . . .                  | 19        |

| 2.6.3    | Híbrido ( <i>competitive update</i> ) . . . . .          | 19        |

| 2.7      | Tipos de <i>miss</i> . . . . .                           | 19        |

| 2.7.1    | <i>False miss</i> . . . . .                              | 20        |

| 2.7.2    | <i>True miss</i> . . . . .                               | 20        |

| 2.7.3    | <i>Eviction miss</i> . . . . .                           | 20        |

| 2.7.4    | <i>Cold start miss</i> . . . . .                         | 20        |

| 2.7.5    | <i>Drop miss</i> . . . . .                               | 21        |

| <b>3</b> | <b>Programação Lógica-Paralela</b>                       | <b>22</b> |

| 3.1      | Conceitos Básicos . . . . .                              | 22        |

| 3.2      | Andorra-I . . . . .                                      | 25        |

| <b>4</b> | <b>Metodologia de Avaliação</b>                          | <b>28</b> |

| 4.1      | Simulador MINT . . . . .                                 | 28        |

| 4.2      | Aplicações e suas características . . . . .              | 31        |

| 4.2.1    | Problema do caixeiro viajante (tsp) . . . . .            | 31        |

| 4.2.2    | Gerenciamento de redes da British Telecom (bt) . . . . . | 31        |

|                  |                                                              |           |

|------------------|--------------------------------------------------------------|-----------|

| 4.2.3            | Sistema de pergunta-resposta usando linguagem natural (chat) | 31        |

| 4.2.4            | Sistema de alocação de recursos Pandora (pan2)               | 31        |

| <b>5</b>         | <b>Resultados</b>                                            | <b>34</b> |

| 5.1              | Aplicação BT                                                 | 35        |

| 5.2              | Aplicação CHAT                                               | 39        |

| 5.3              | Aplicação PAN2                                               | 42        |

| 5.4              | Aplicação TSP                                                | 46        |

| 5.5              | Discussão                                                    | 47        |

| <b>6</b>         | <b>Conclusões e Trabalhos Futuros</b>                        | <b>60</b> |

| <b>Apêndices</b> |                                                              | <b>62</b> |

| <b>A</b>         | <b>Parâmetros do backend do simulador</b>                    | <b>63</b> |

| <b>B</b>         | <b>Parâmetros do frontend do simulador</b>                   | <b>64</b> |

# Listas de Figuras

|     |                                                                                                                                            |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Exemplo de programa prolog . . . . .                                                                                                       | 1  |

| 2.1 | Arquitetura SISD . . . . .                                                                                                                 | 7  |

| 2.2 | Arquitetura SIMD . . . . .                                                                                                                 | 7  |

| 2.3 | Arquitetura MISD . . . . .                                                                                                                 | 8  |

| 2.4 | Arquitetura MIMD . . . . .                                                                                                                 | 9  |

| 2.5 | Divisões das arquitetura MIMD . . . . .                                                                                                    | 9  |

| 2.6 | UMA - <i>Uniform Memory Access</i> . . . . .                                                                                               | 10 |

| 2.7 | NUMA - <i>NON Uniform Memory Access</i> . . . . .                                                                                          | 11 |

| 2.8 | CC-NUMA - <i>Cache Coherente - NON Uniform Memory Access</i> . . . . .                                                                     | 11 |

| 3.1 | Exemplo de algoritmo de programação lógica - definição de tio . . . . .                                                                    | 23 |

| 3.2 | Exemplo de algoritmo de programação lógica - definição de irmão . . . . .                                                                  | 23 |

| 3.3 | Exemplo de algoritmo de programação lógica - <i>quicksort</i> . . . . .                                                                    | 24 |

| 3.4 | Exemplo de árvores de tarefas - <i>E</i> e - <i>OU</i> . . . . .                                                                           | 25 |

| 3.5 | Estrutura do sistema Andorra-I . . . . .                                                                                                   | 26 |

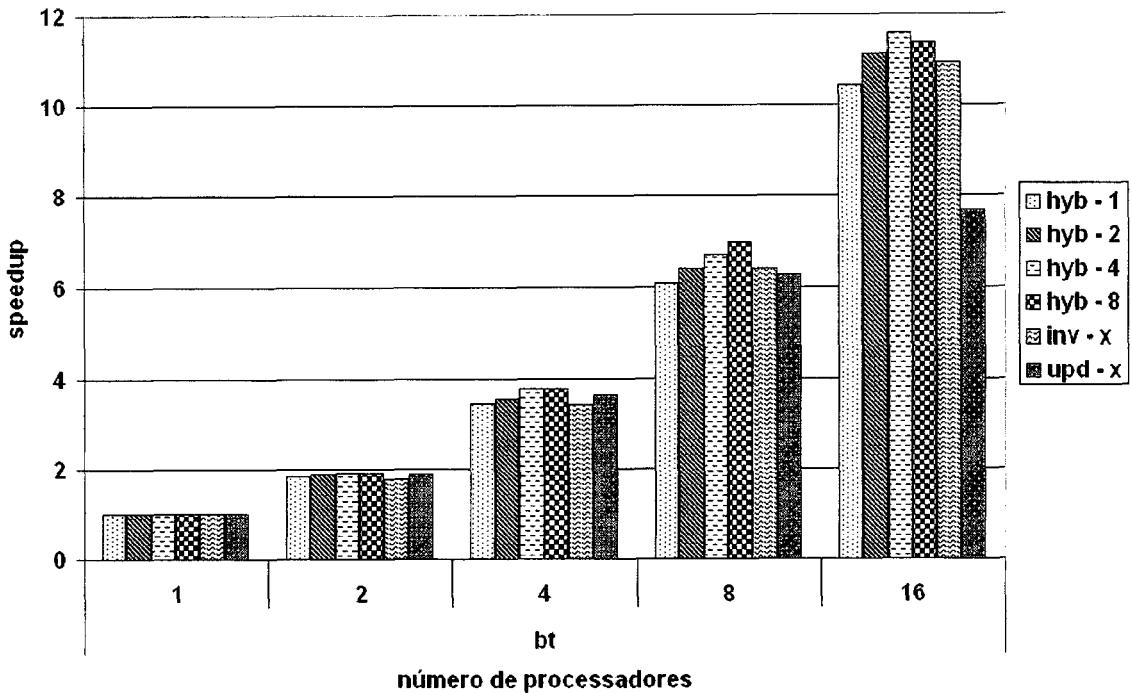

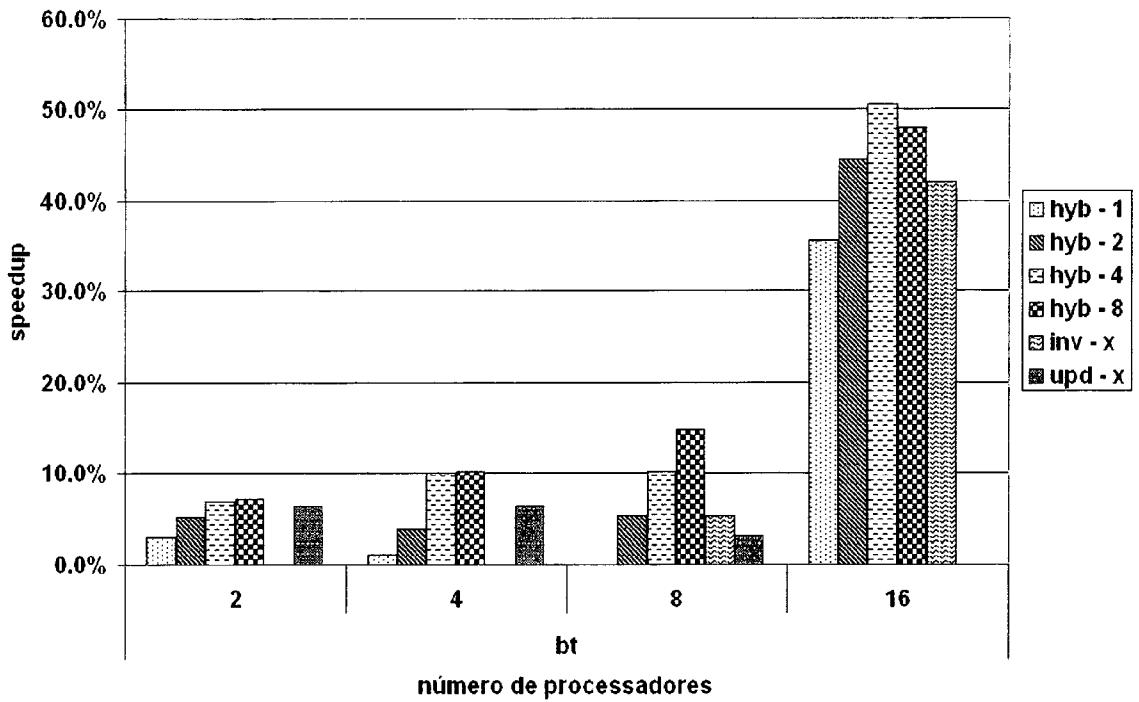

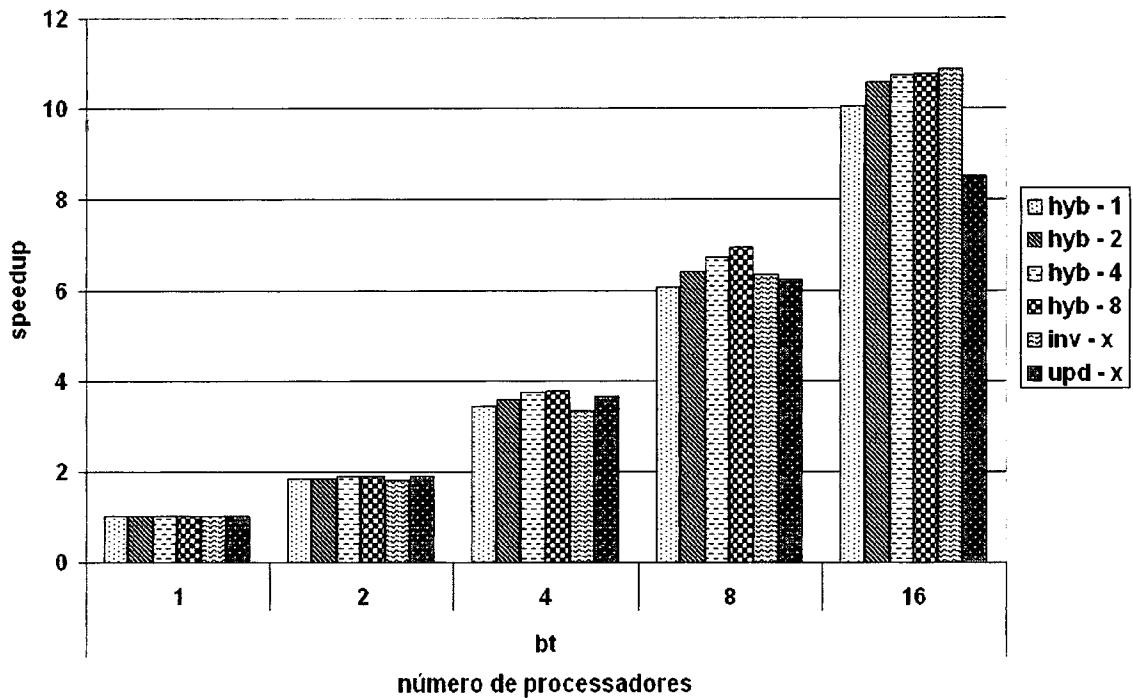

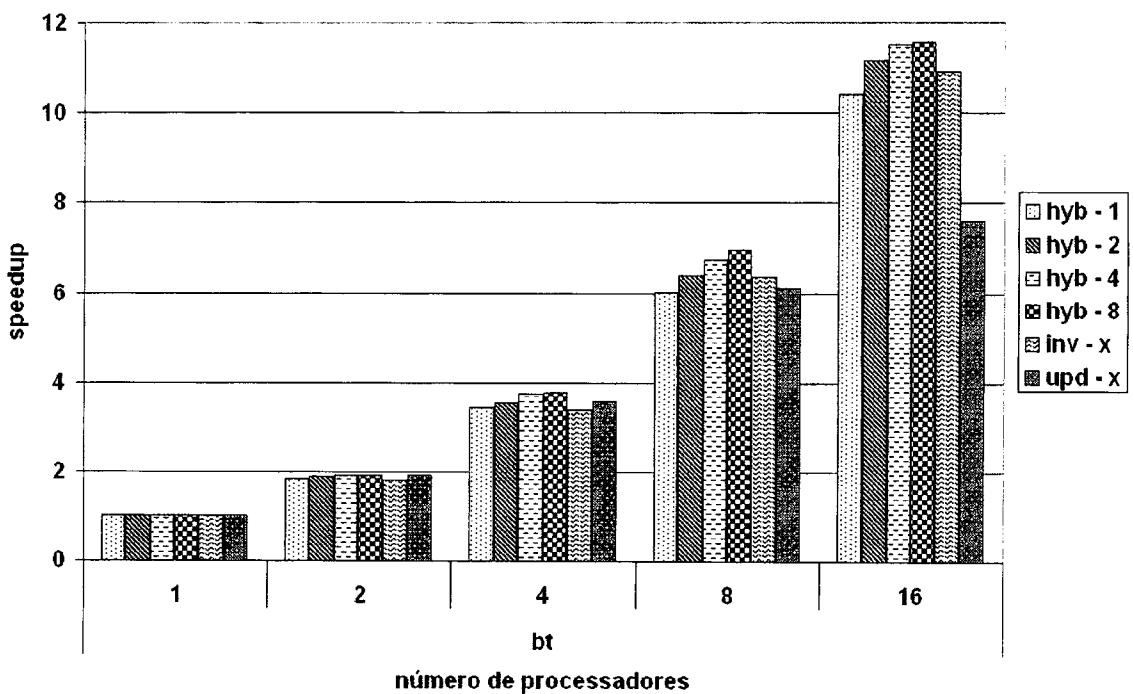

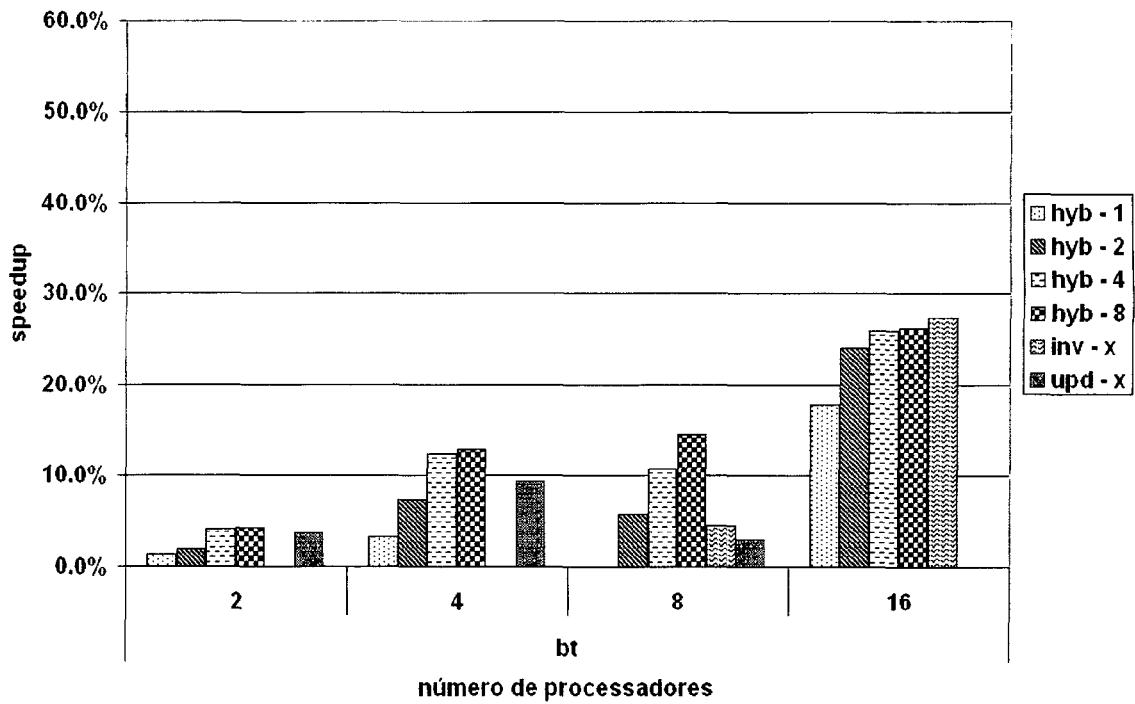

| 5.1 | <i>Speedup</i> da aplicação BT, <i>cache</i> de 512 Kbytes . . . . .                                                                       | 35 |

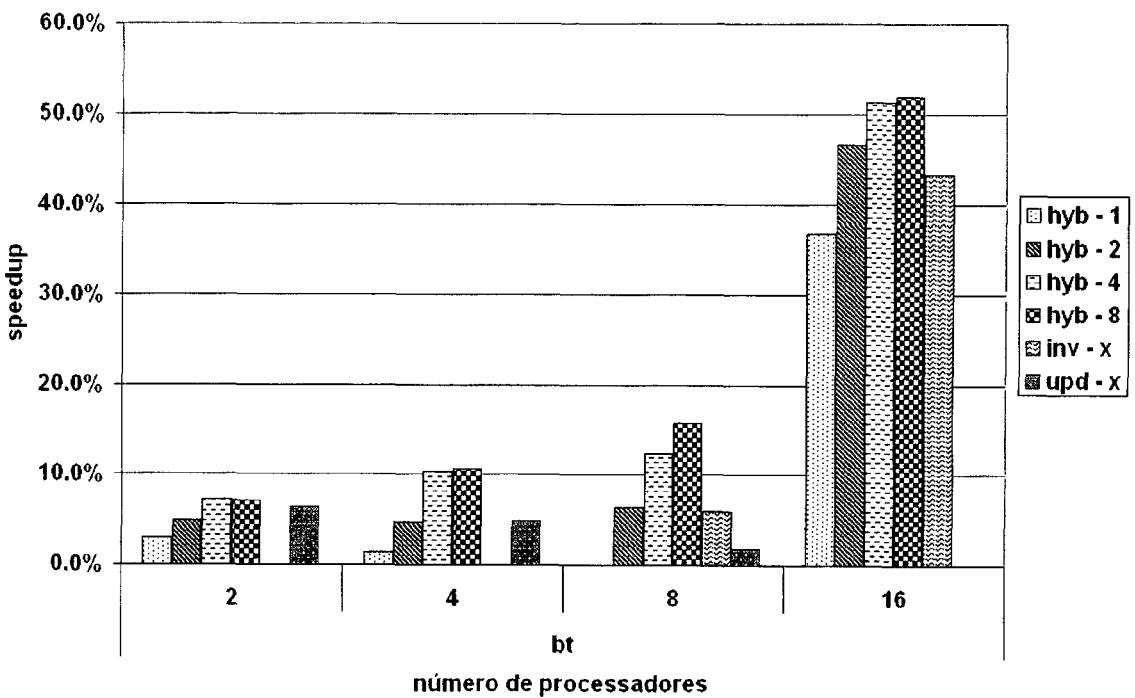

| 5.2 | Comparativo de ganhos percentuais da aplicação BT em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 512 Kbytes . . . . .   | 36 |

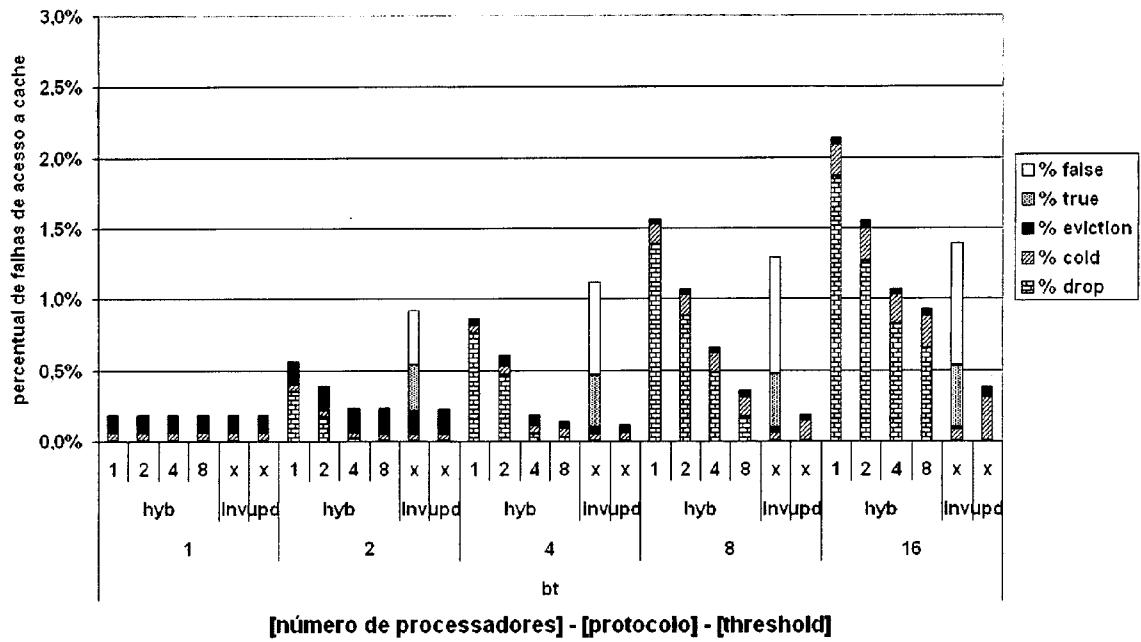

| 5.3 | Número de <i>misses</i> da aplicação BT por número de processadores . . . . .                                                              | 37 |

| 5.4 | Número de <i>useless updates</i> da aplicação BT por número de processadores . . . . .                                                     | 37 |

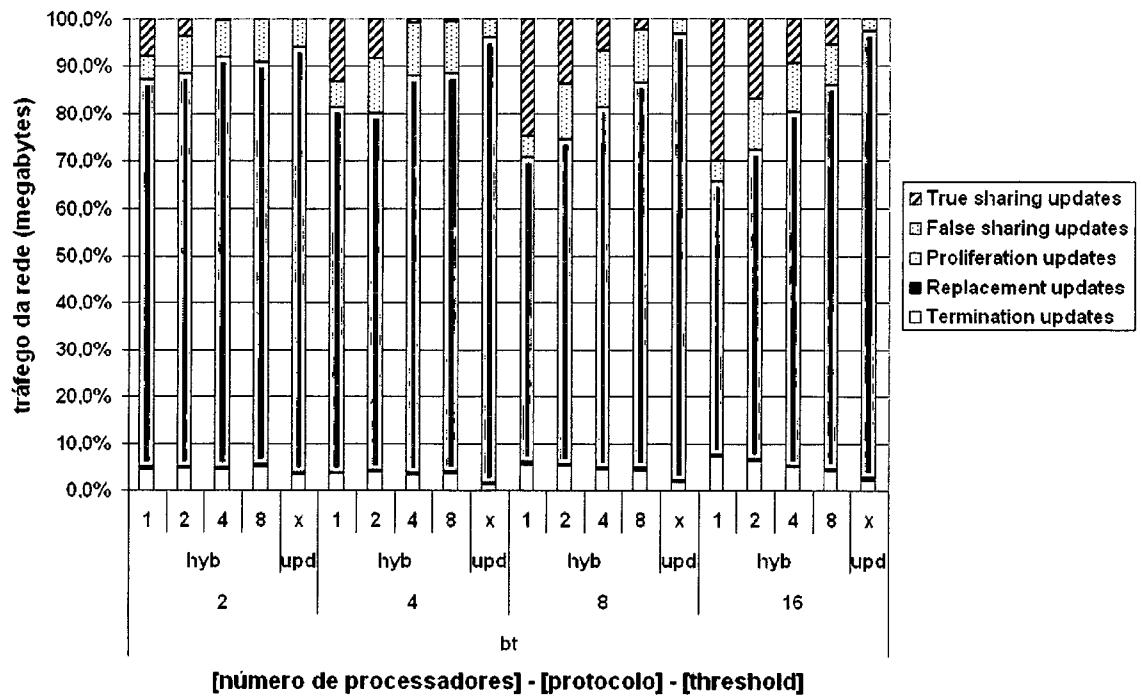

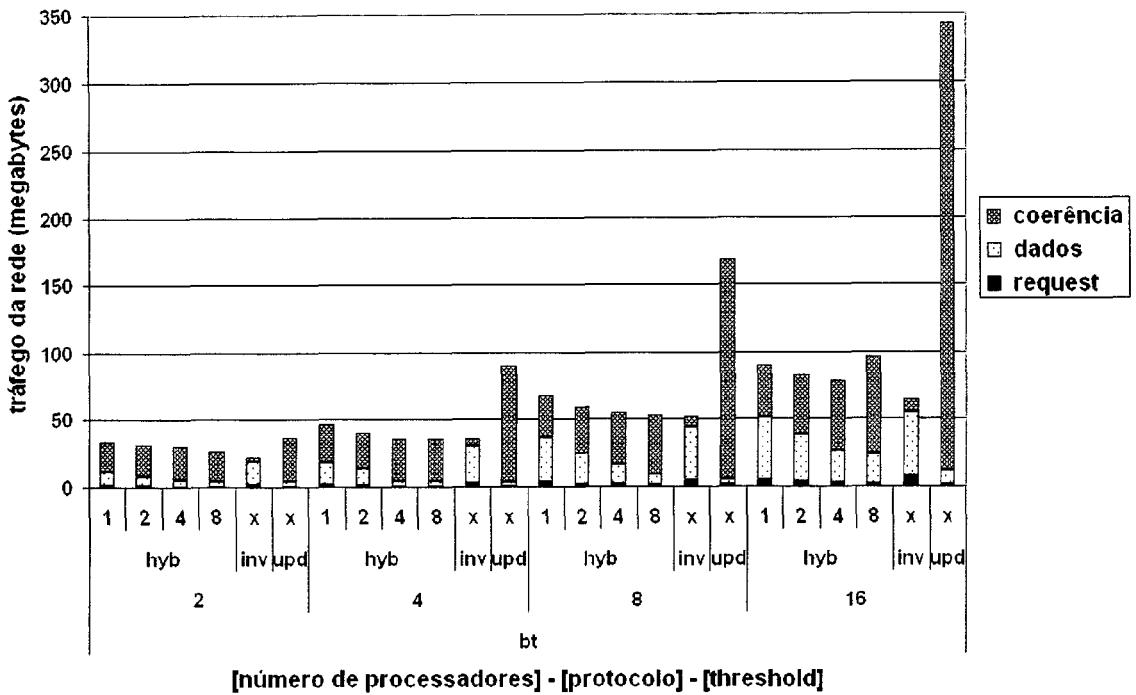

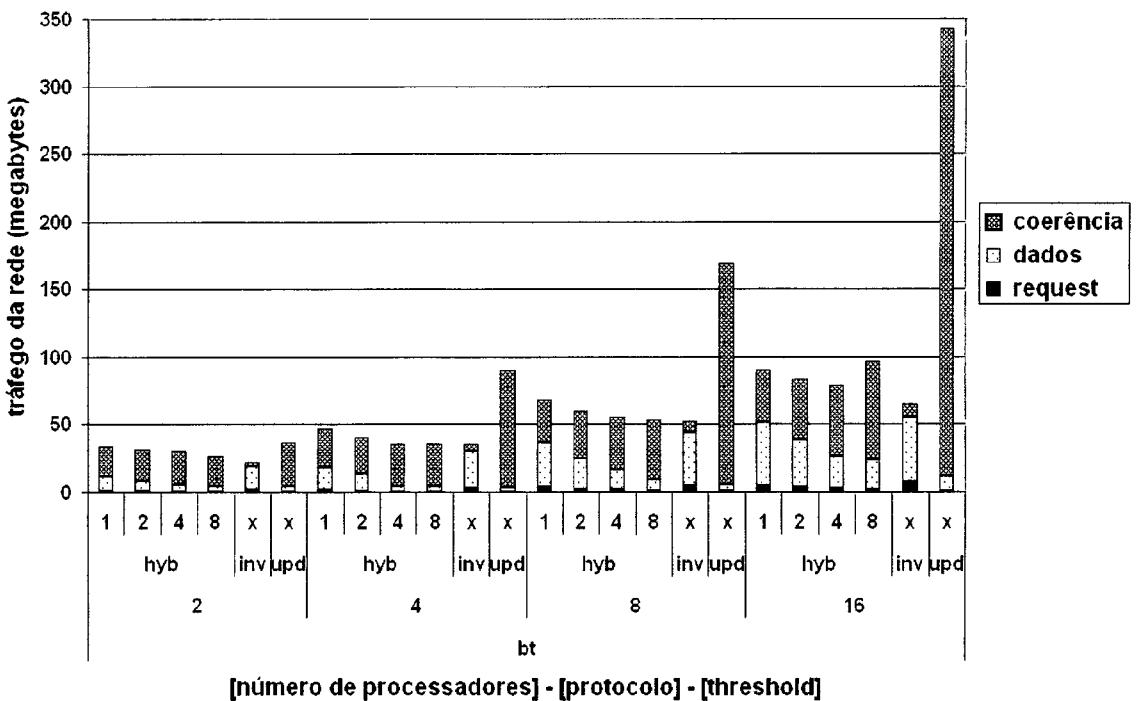

| 5.5 | Comportamento da rede da aplicação BT por número de processadores                                                                          | 38 |

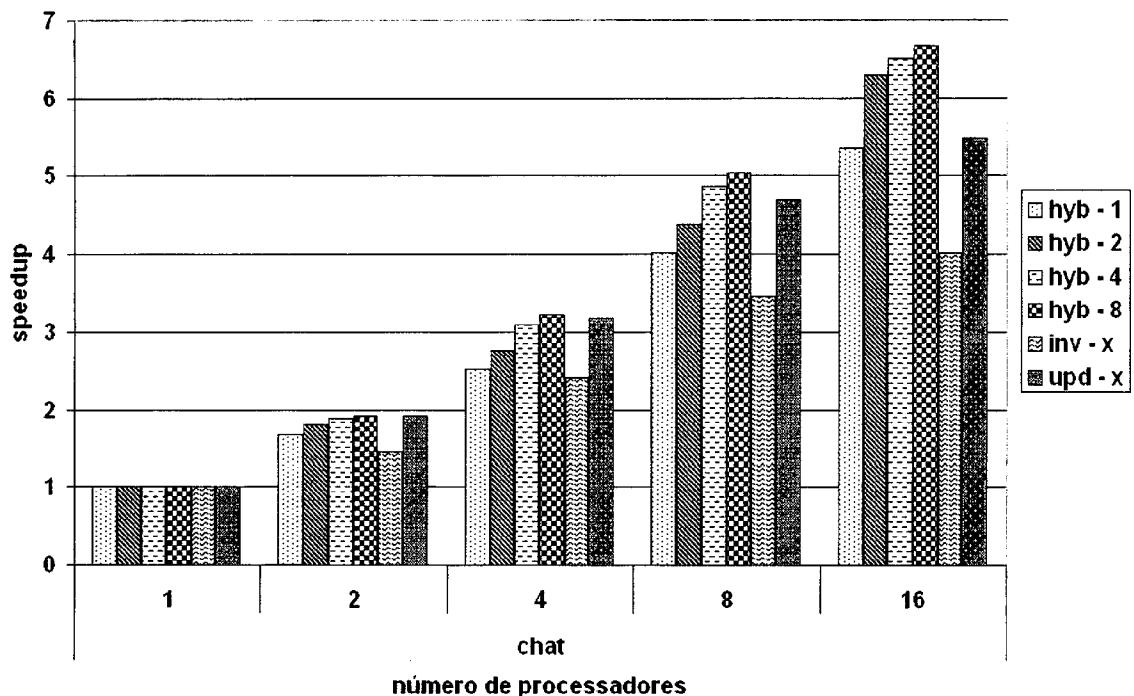

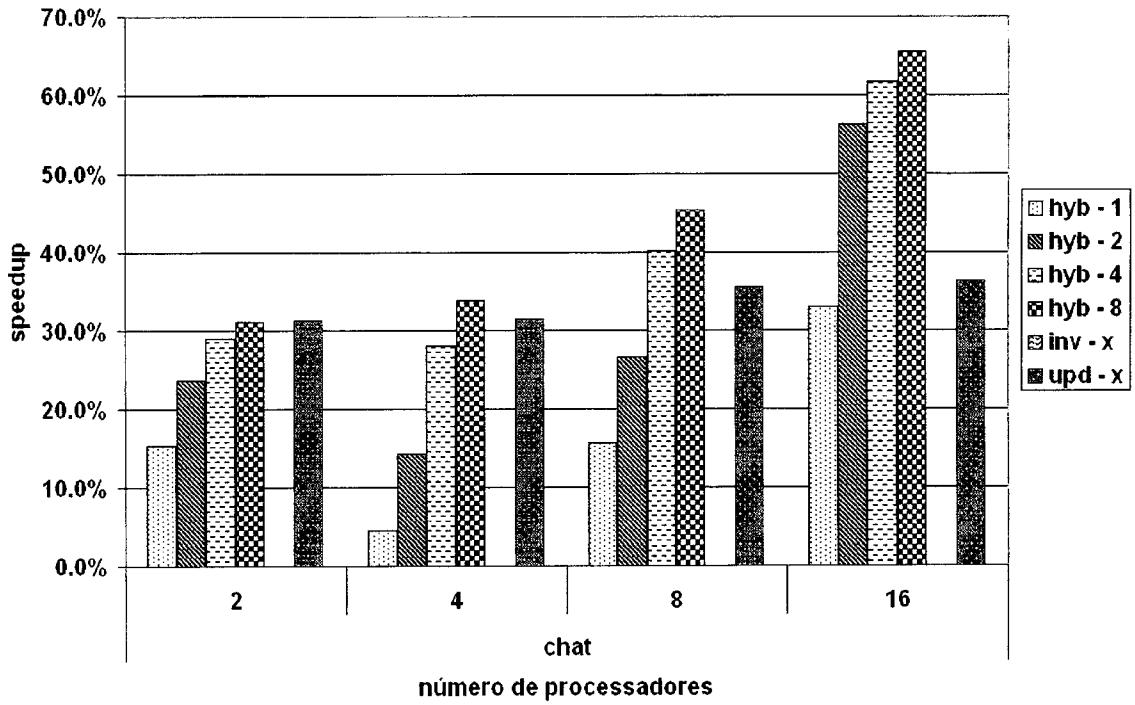

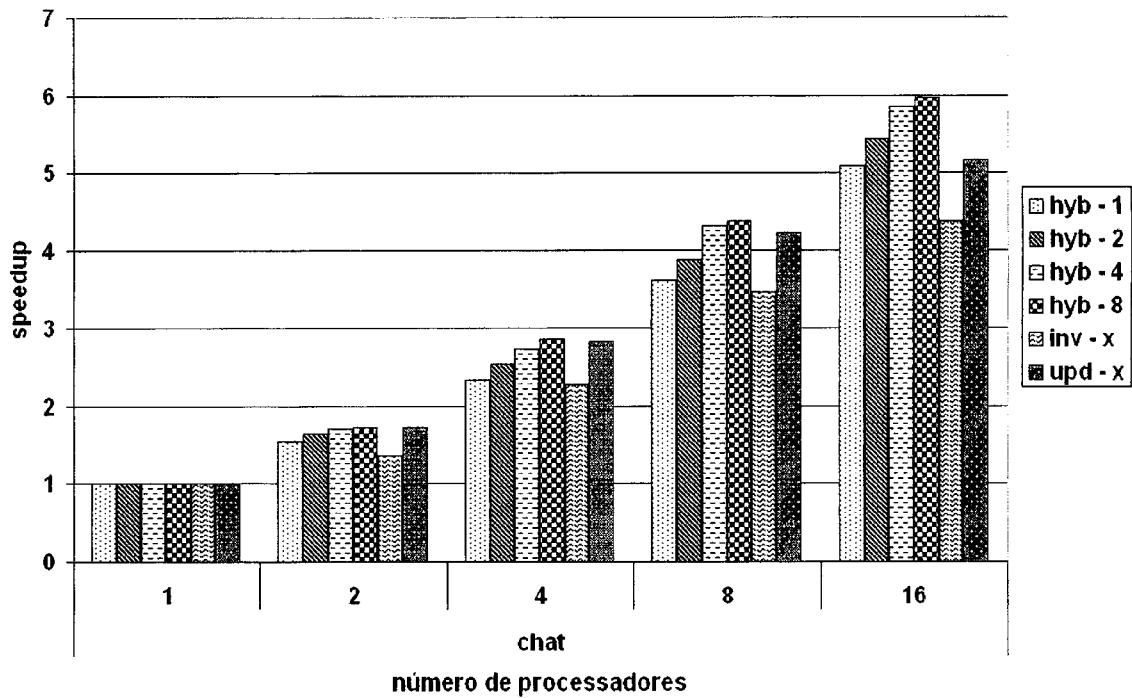

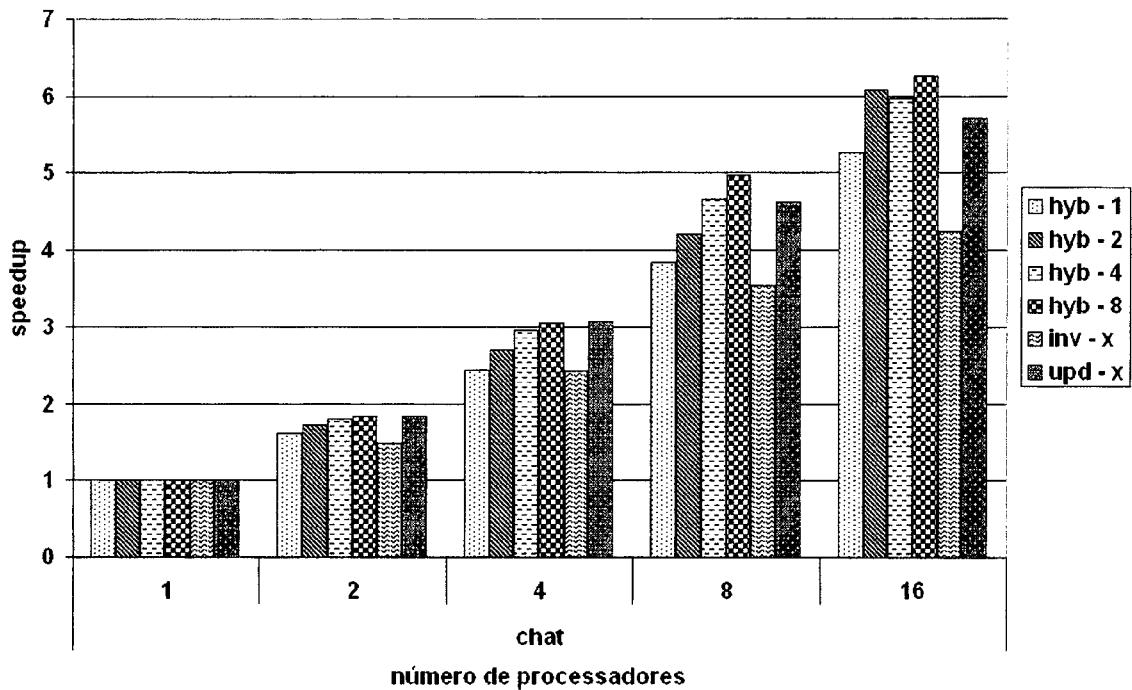

| 5.6 | <i>Speedup</i> da aplicação CHAT, <i>cache</i> de 512 Kbytes . . . . .                                                                     | 39 |

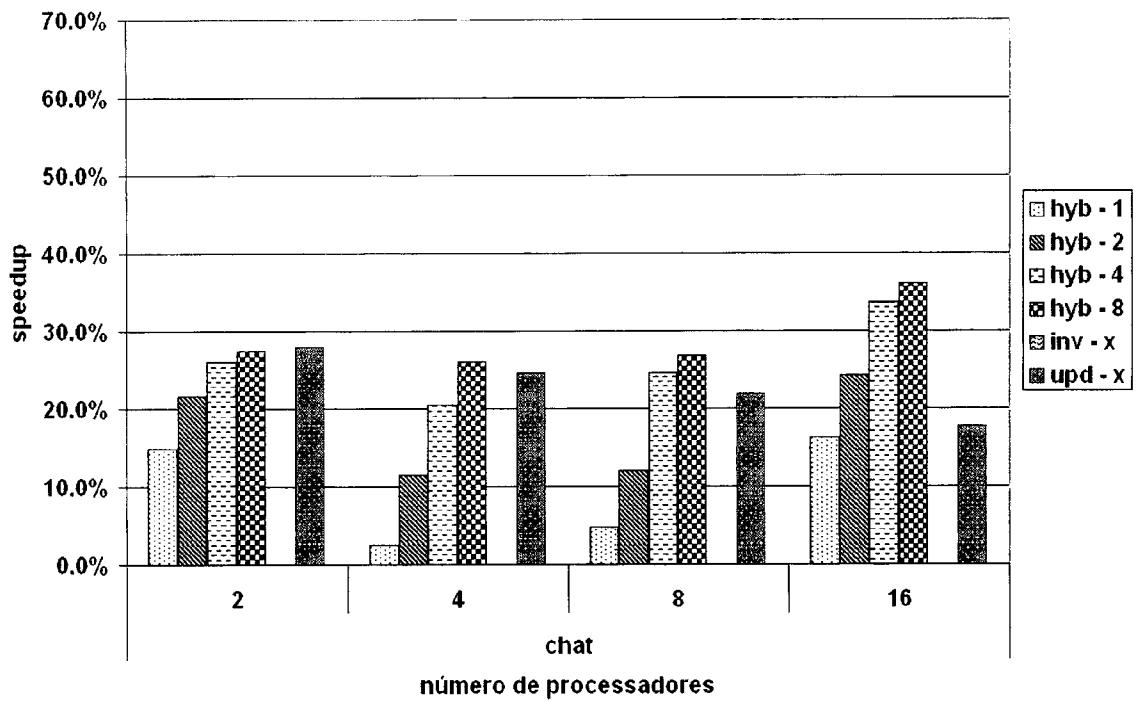

| 5.7 | Comparativo de ganhos percentuais da aplicação CHAT em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 512 Kbytes . . . . . | 40 |

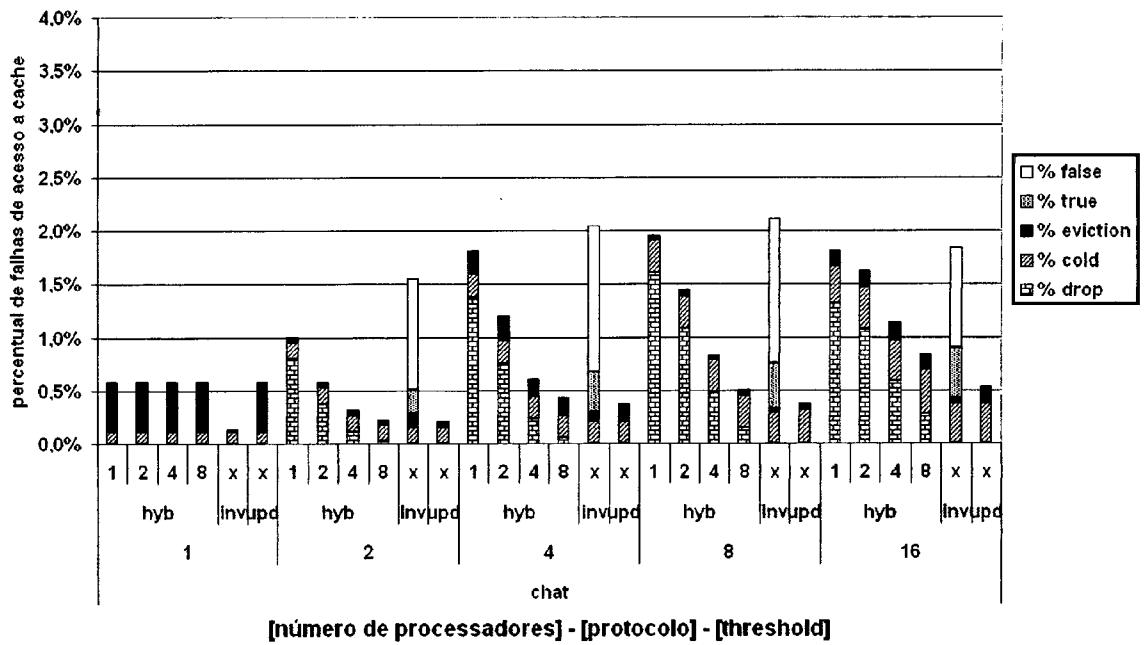

| 5.8 | Número de <i>misses</i> da aplicação CHAT por número de processadores .                                                                    | 41 |

|                                                                                                                                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.9 Número de <i>useless updates</i> da aplicação CHAT por número de processadores . . . . .                                                     | 41 |

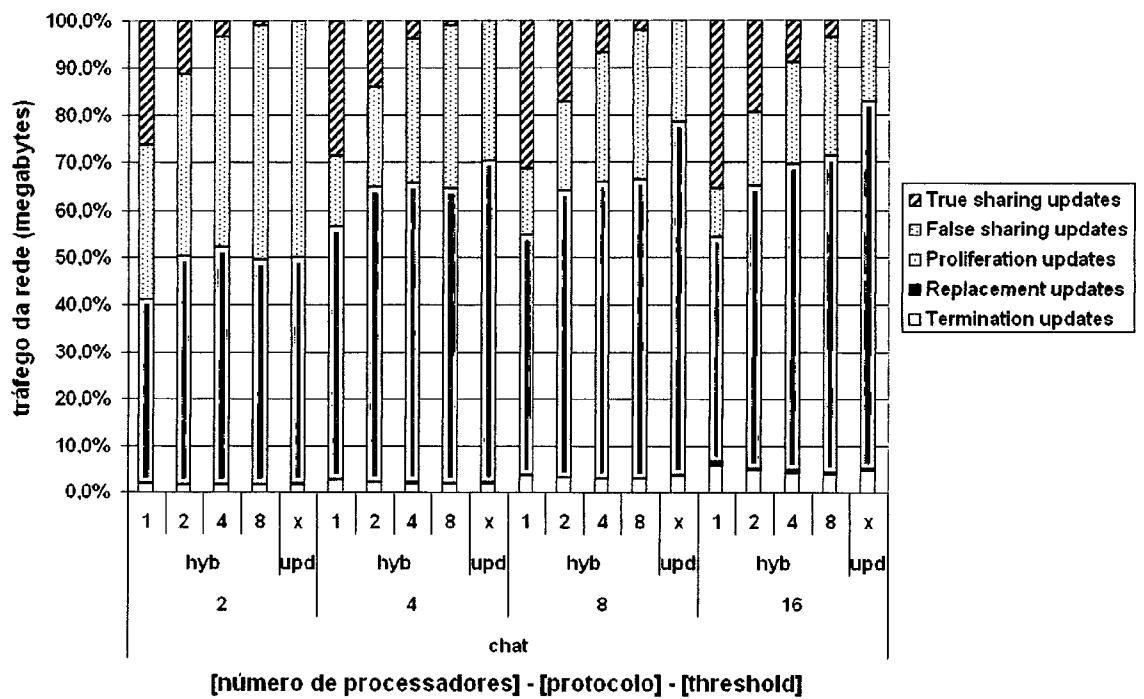

| 5.10 Comportamento da rede da aplicação CHAT por número de processadores . . . . .                                                               | 42 |

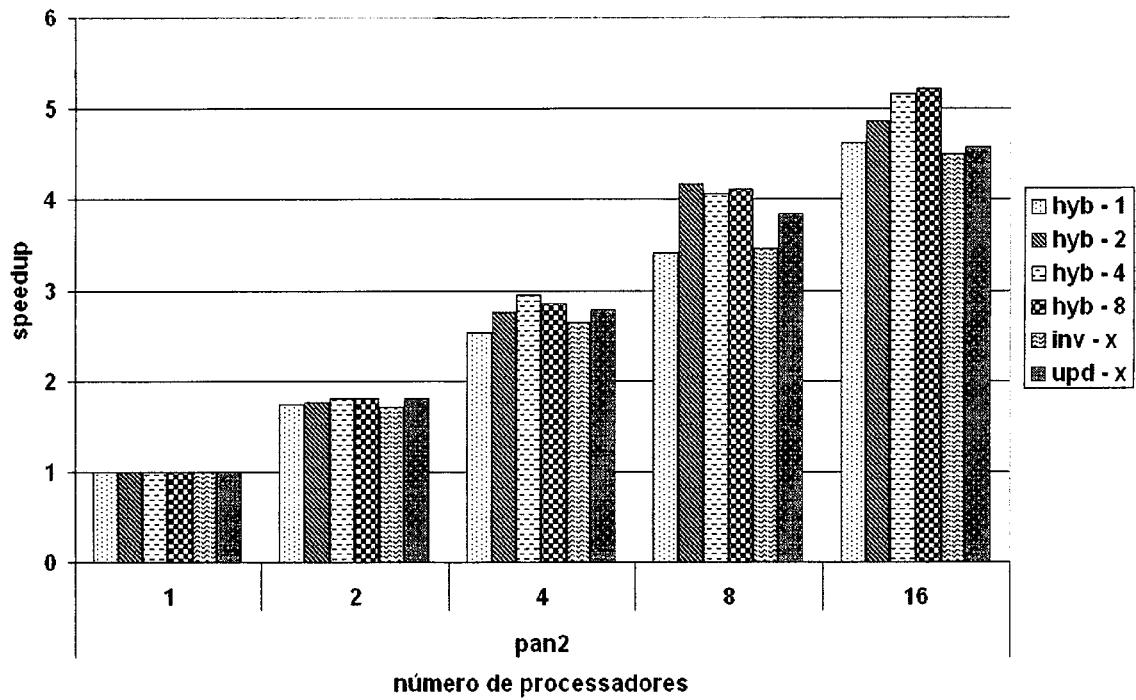

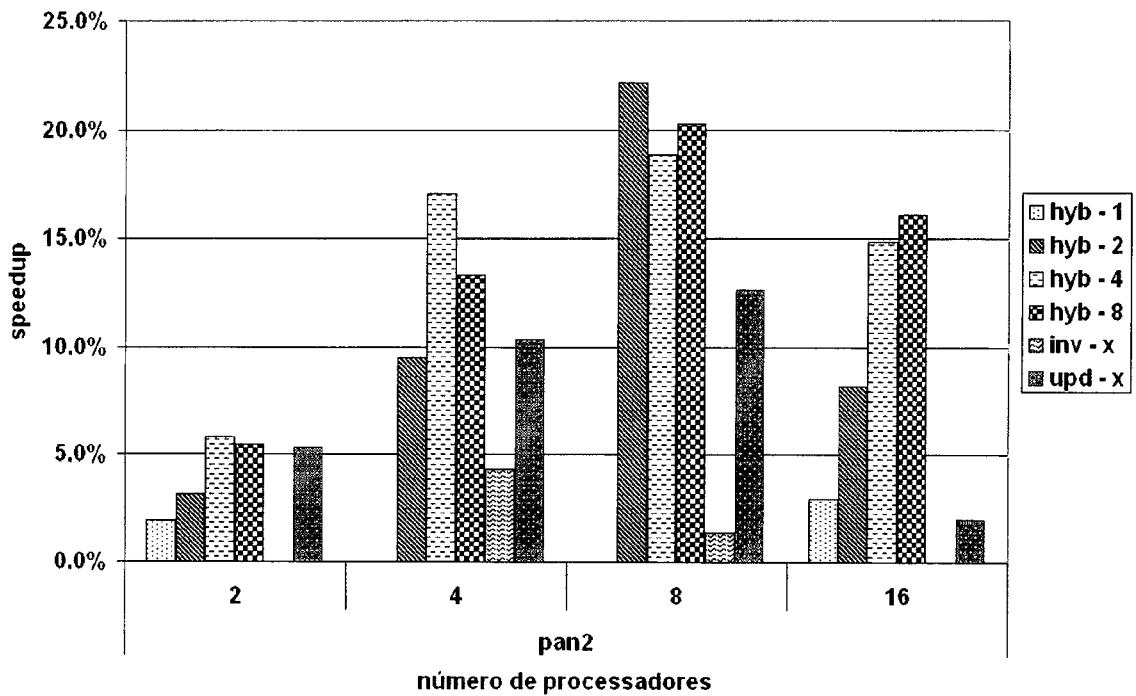

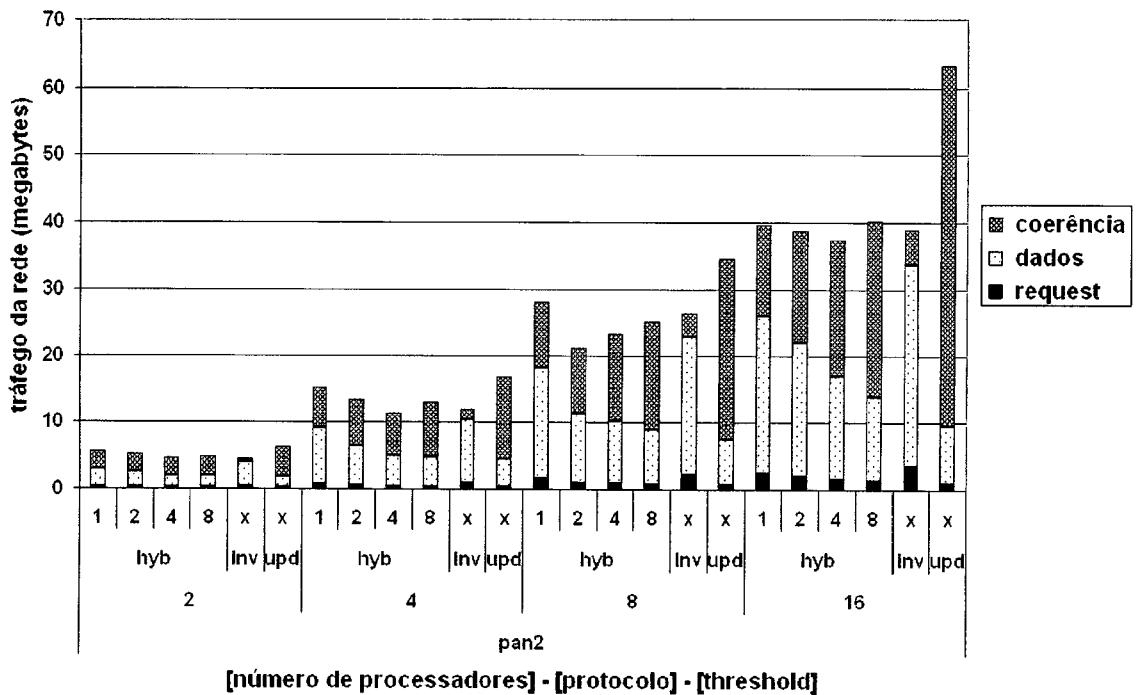

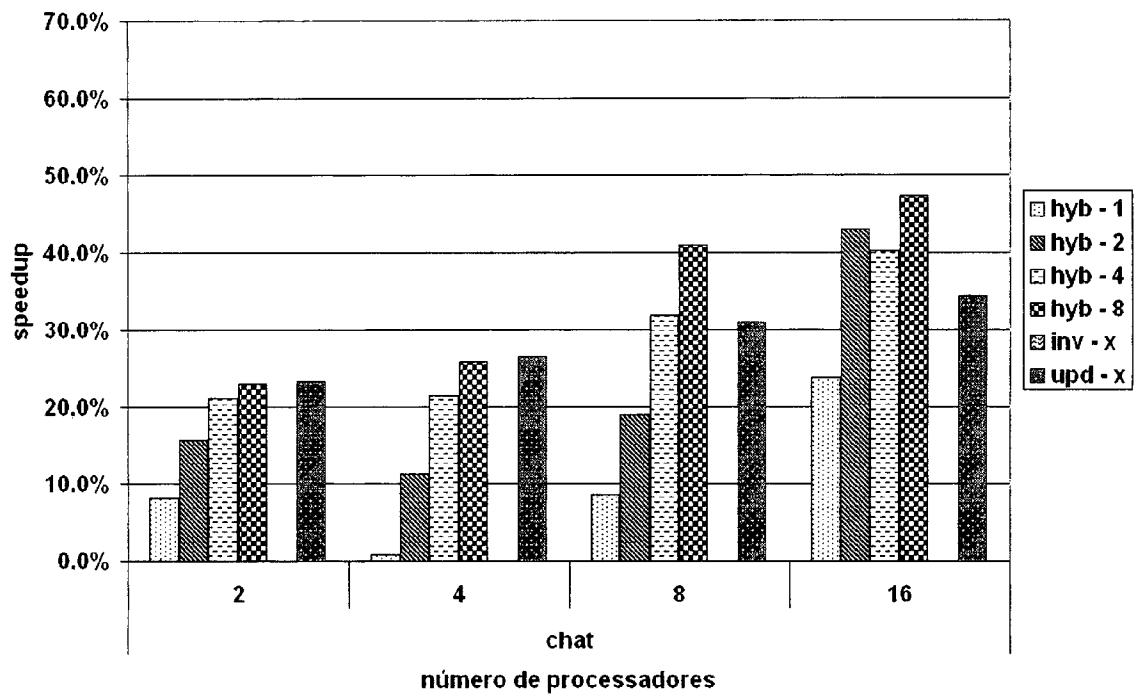

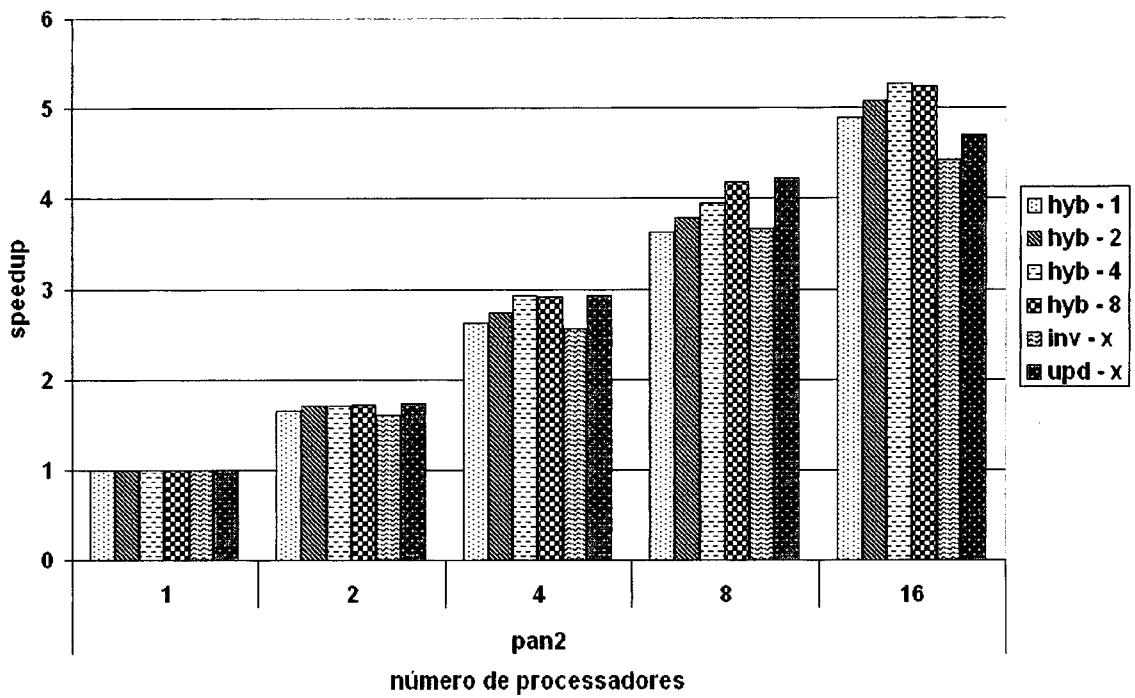

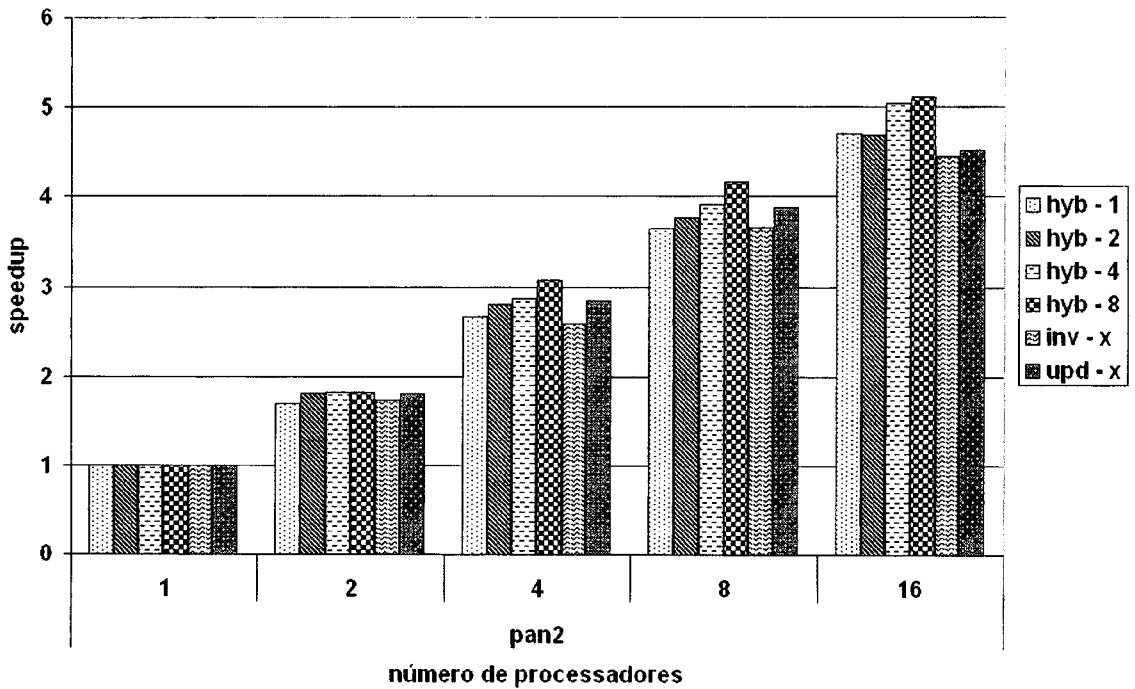

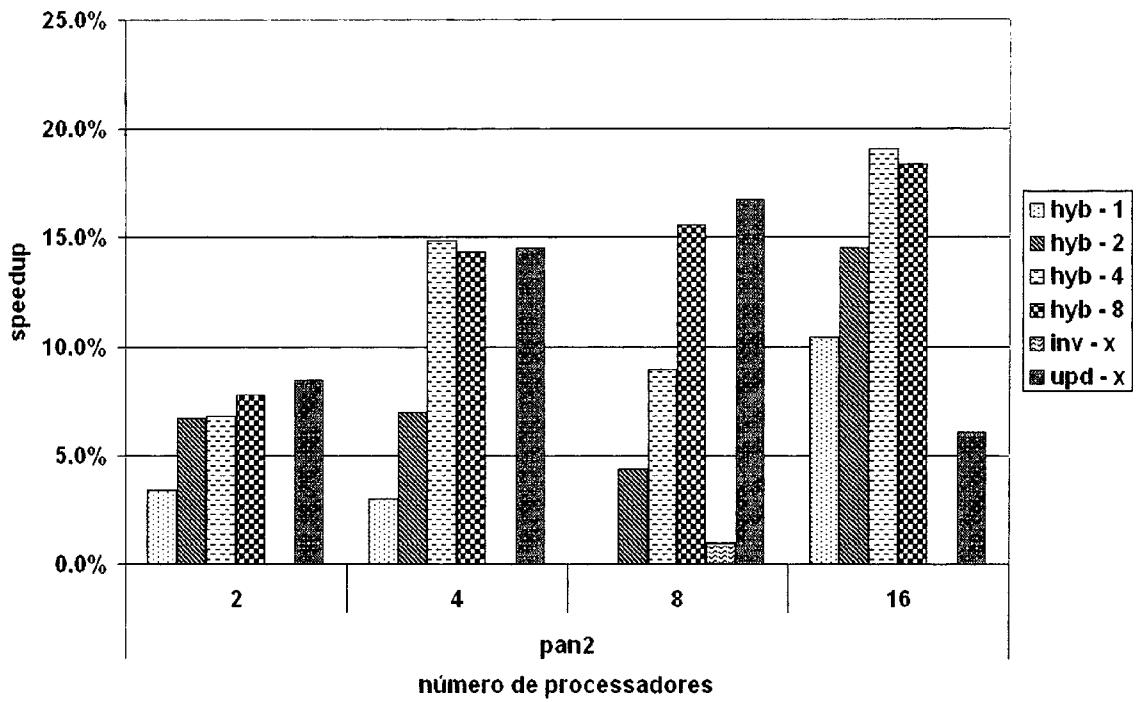

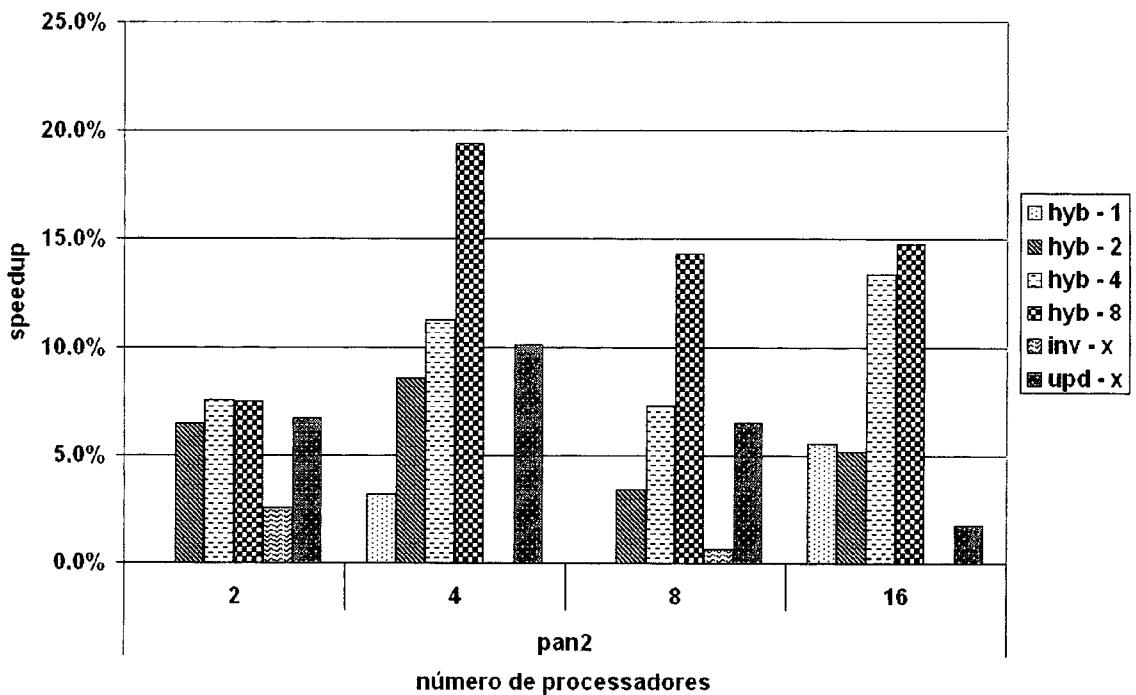

| 5.11 <i>Speedup</i> da aplicação PAN2, <i>cache</i> de 512 KBytes . . . . .                                                                      | 43 |

| 5.12 Comparativo de ganhos percentuais da aplicação PAN2 em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 512 Kbytes . . . . .  | 43 |

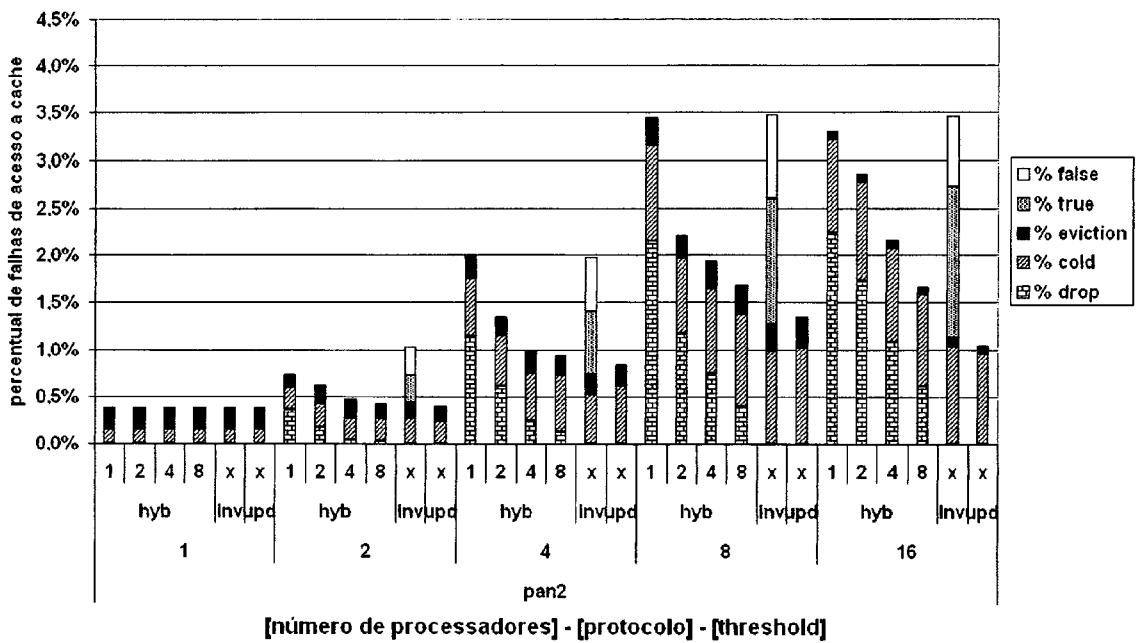

| 5.13 Número de <i>misses</i> da aplicação PAN2 por número de processadores . . . . .                                                             | 44 |

| 5.14 Número de <i>useless updates</i> da aplicação PAN2 por número de processadores . . . . .                                                    | 45 |

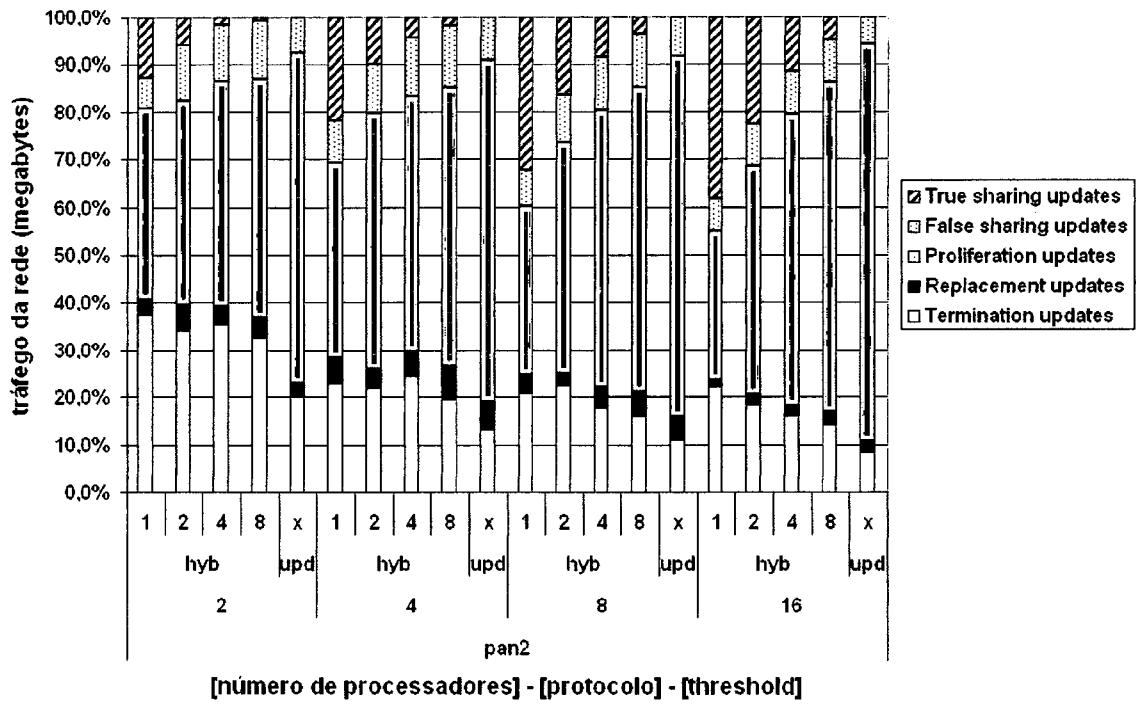

| 5.15 Comportamento da rede da aplicação PAN2 por número de processadores . . . . .                                                               | 45 |

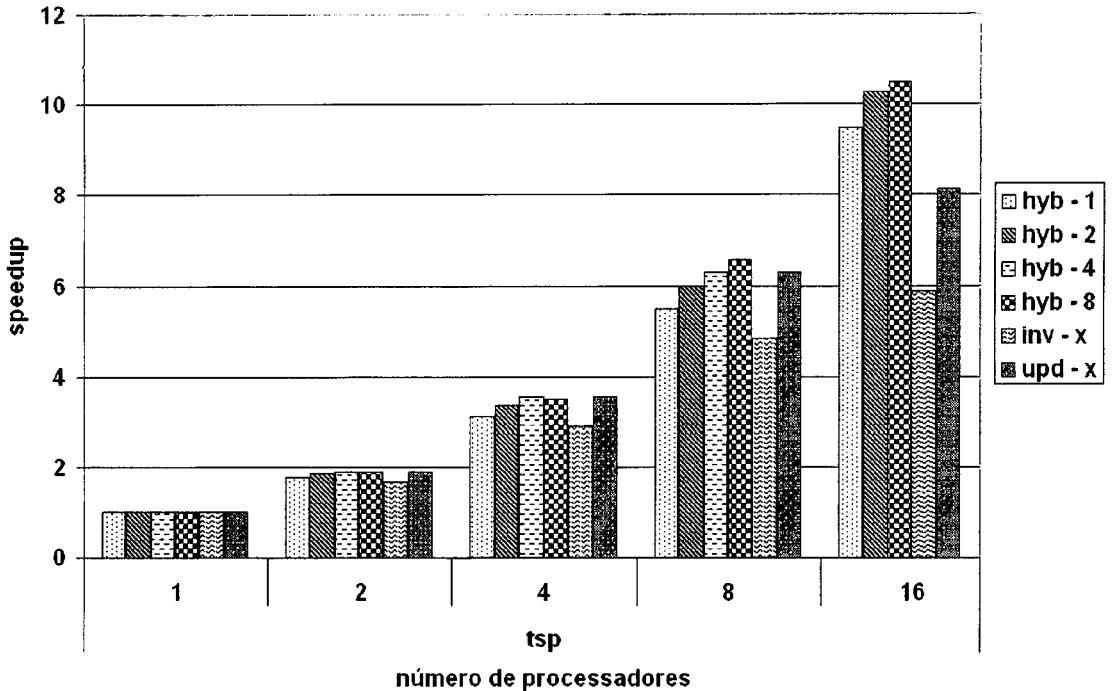

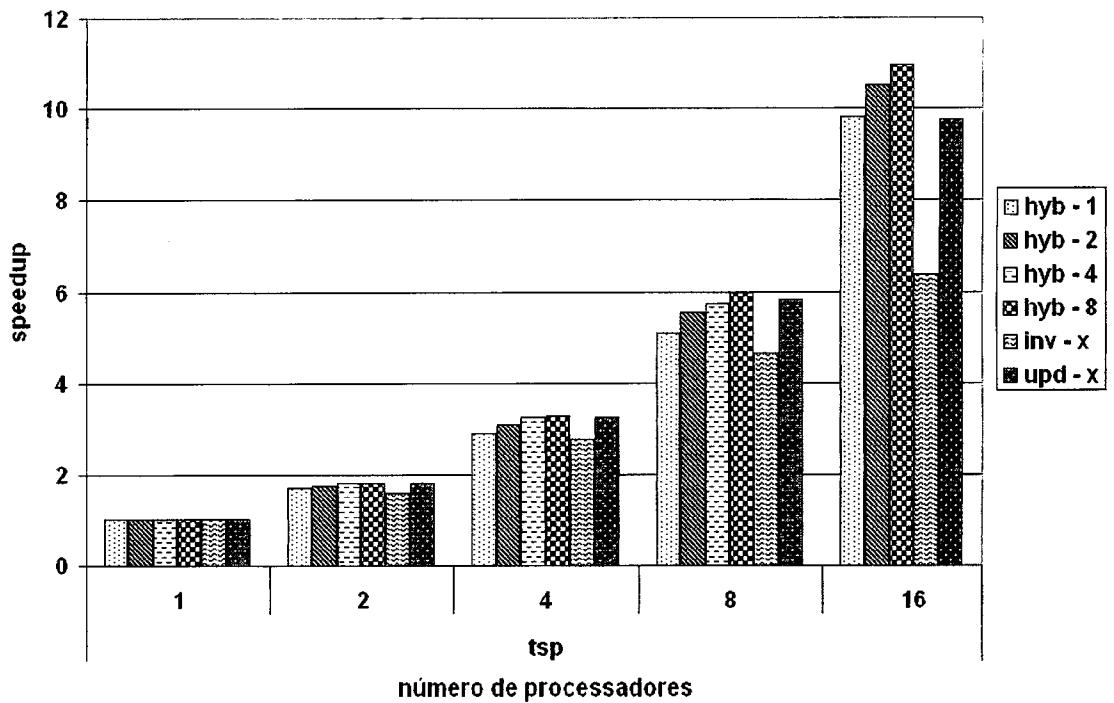

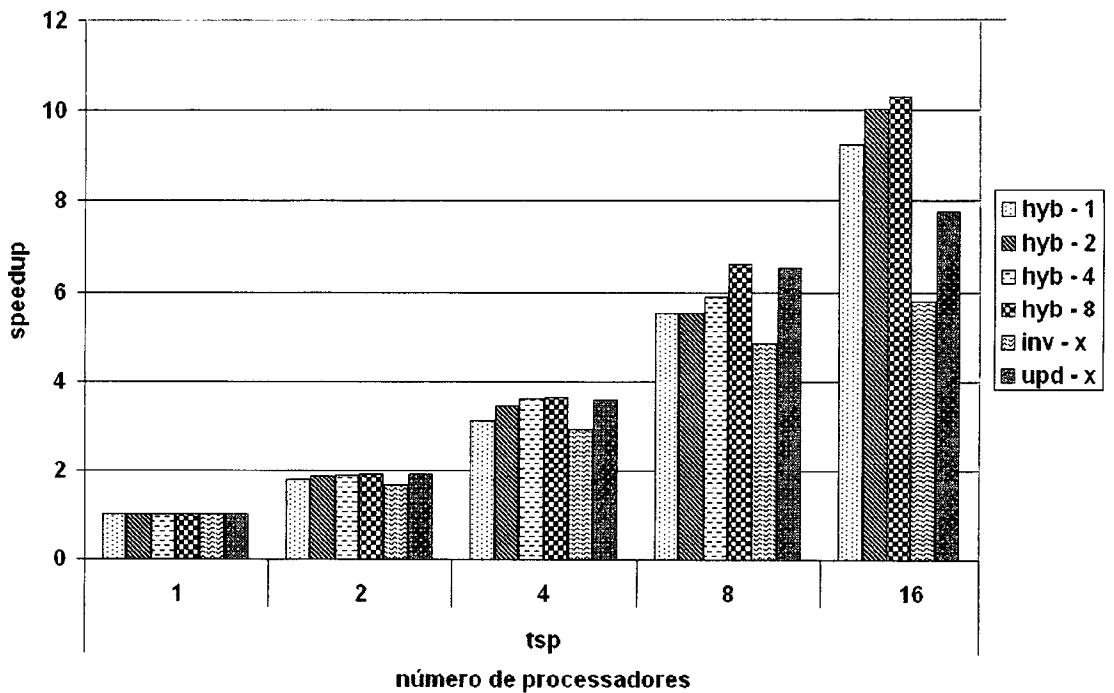

| 5.16 <i>Speedup</i> da aplicação TSP, <i>cache</i> de 512 Kbytes . . . . .                                                                       | 46 |

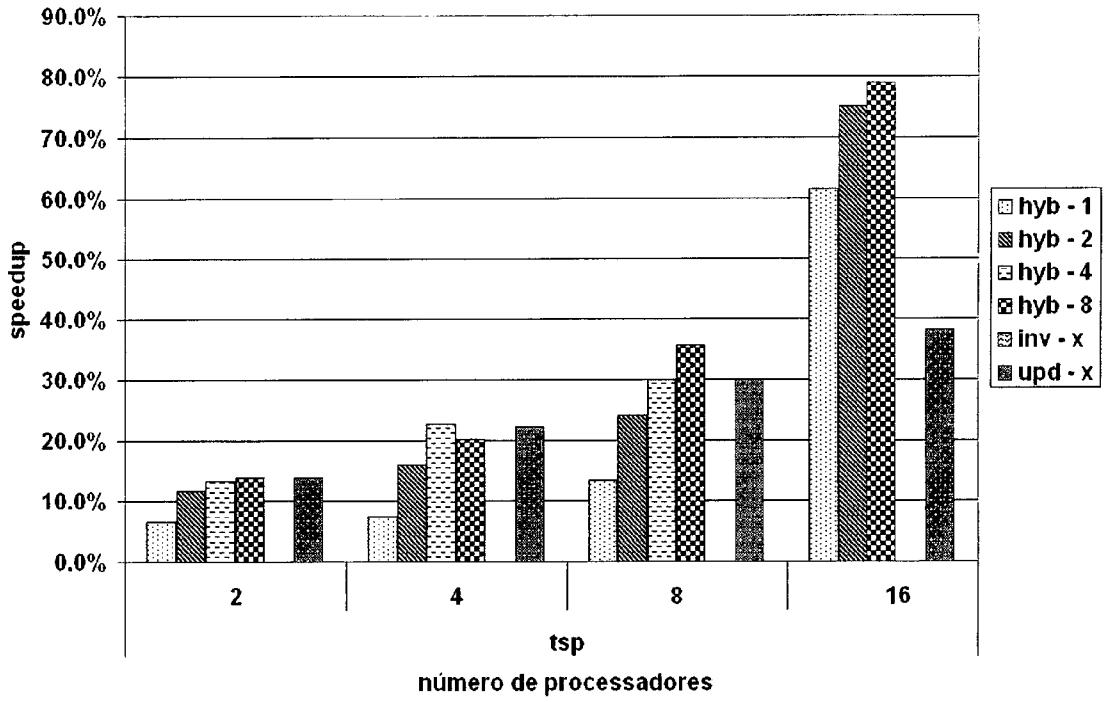

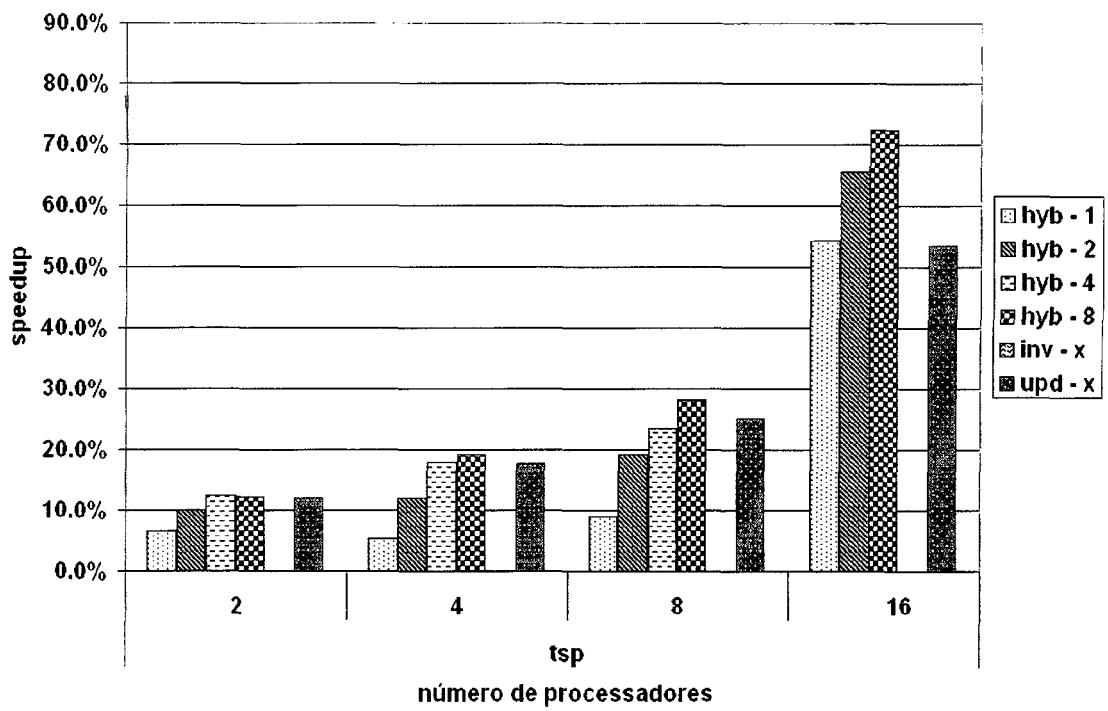

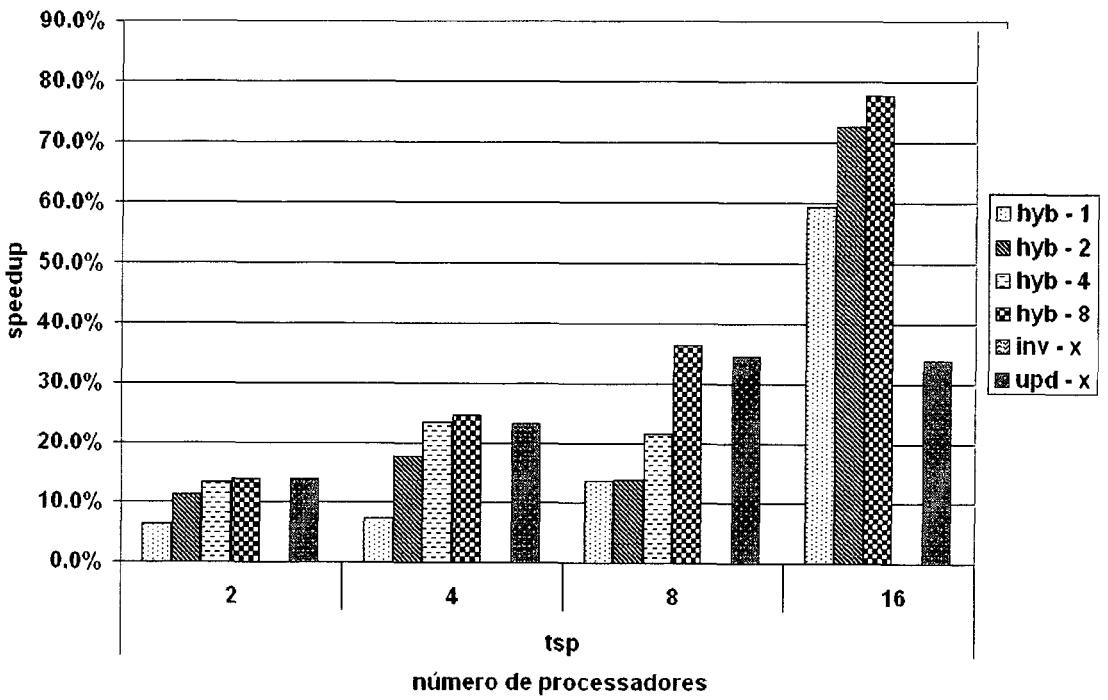

| 5.17 Comparativo de ganhos percentuais da aplicação TSP em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 512 Kbytes . . . . .   | 47 |

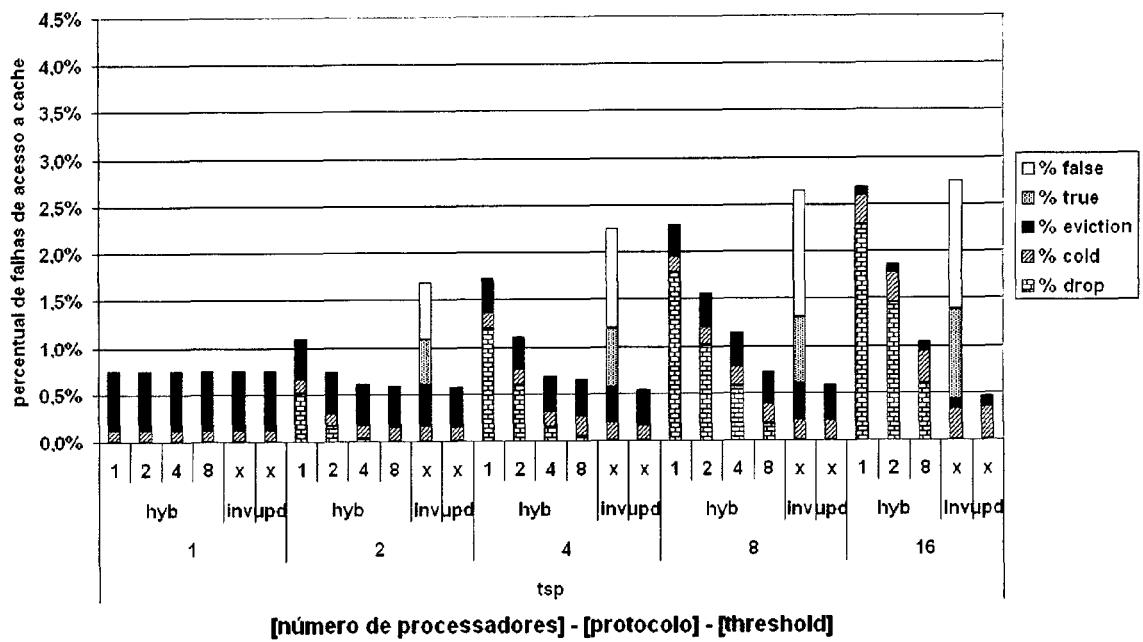

| 5.18 Número de <i>misses</i> da aplicação TSP por número de processadores . . . . .                                                              | 48 |

| 5.19 Número de <i>useless updates</i> da aplicação TSP por número de processadores . . . . .                                                     | 48 |

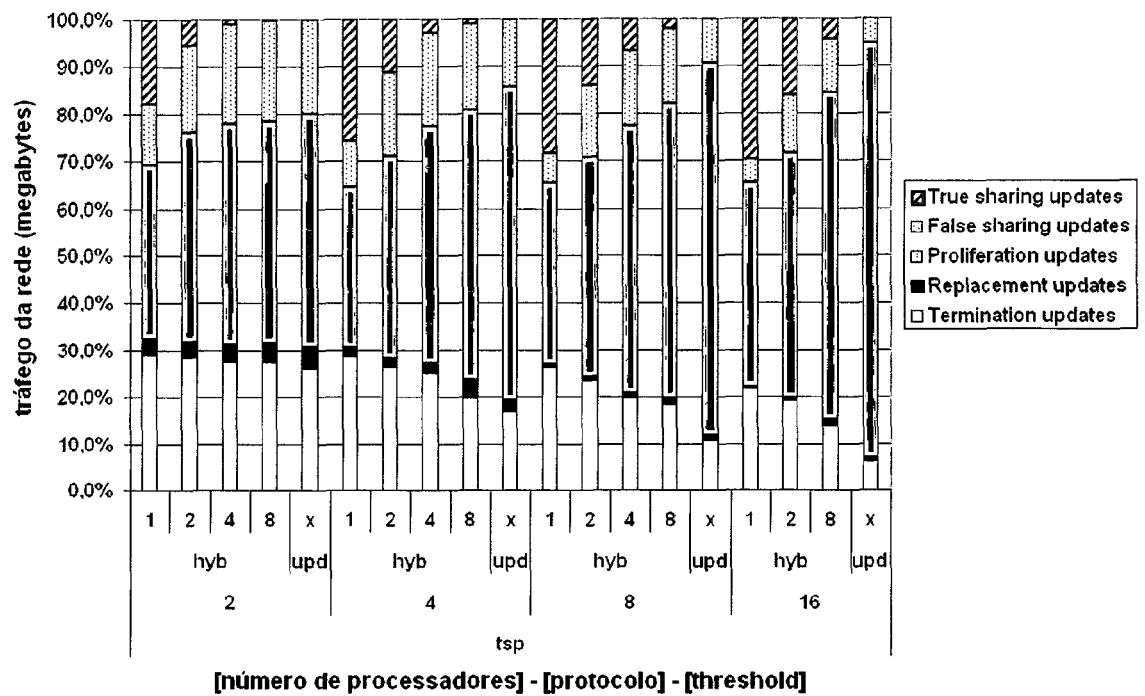

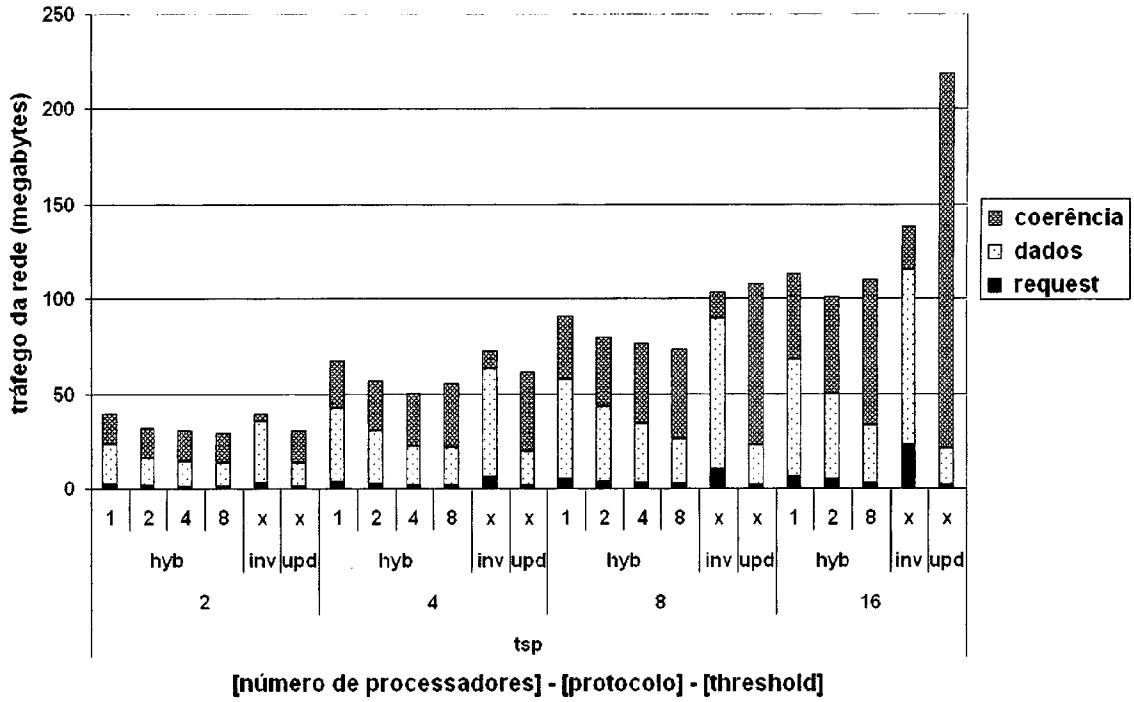

| 5.20 Comportamento da rede da aplicação TSP por número de processadores                                                                          | 49 |

| 5.21 <i>Speedup</i> da aplicação BT, <i>cache</i> de 128 Kbytes . . . . .                                                                        | 51 |

| 5.22 <i>Speedup</i> da aplicação BT, <i>cache</i> de 1024 Kbytes . . . . .                                                                       | 51 |

| 5.23 Comparativo de ganhos percentuais da aplicação BT em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 128 Kbytes . . . . .    | 52 |

| 5.24 Comparativo de ganhos percentuais da aplicação BT em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 1024 Kbytes . . . . .   | 52 |

| 5.25 <i>Speedup</i> da aplicação CHAT, <i>cache</i> de 128 Kbytes . . . . .                                                                      | 53 |

| 5.26 <i>Speedup</i> da aplicação CHAT, <i>cache</i> de 1024 Kbytes . . . . .                                                                     | 53 |

| 5.27 Comparativo de ganhos percentuais da aplicação CHAT em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 128 Kbytes . . . . .  | 54 |

| 5.28 Comparativo de ganhos percentuais da aplicação CHAT em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 1024 Kbytes . . . . . | 54 |

| 5.29 <i>Speedup</i> da aplicação PAN2, <i>cache</i> de 128 Kbytes . . . . .                                                                      | 55 |

| 5.30 <i>Speedup</i> da aplicação PAN2, <i>cache</i> de 1024 Kbytes . . . . .                                                                     | 55 |

|                                                                                                                                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.31 Comparativo de ganhos percentuais da aplicação PAN2 em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 128 Kbytes . . . . .  | 56 |

| 5.32 Comparativo de ganhos percentuais da aplicação PAN2 em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 1024 Kbytes . . . . . | 56 |

| 5.33 <i>Speedup</i> da aplicação TSP, <i>cache</i> de 128 Kbytes . . . . .                                                                       | 57 |

| 5.34 <i>Speedup</i> da aplicação TSP, <i>cache</i> de 1024 Kbytes . . . . .                                                                      | 57 |

| 5.35 Comparativo de ganhos percentuais da aplicação TSP em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 128 Kbytes . . . . .   | 58 |

| 5.36 Comparativo de ganhos percentuais da aplicação TSP em relação ao <i>speedup</i> de menor desempenho, <i>cache</i> de 1024 Kbytes . . . . .  | 58 |

# Lista de Tabelas

|     |                                                                   |    |

|-----|-------------------------------------------------------------------|----|

| 4.1 | <i>Speedup</i> esperado para cada aplicação simulada . . . . .    | 32 |

| 4.2 | Referências por área compartilhada (%) . . . . .                  | 33 |

| 5.1 | Tempo de execução das aplicações simuladas com um processador . . | 34 |

| A.1 | parâmetros do simulador - backend . . . . .                       | 63 |

| B.1 | parâmetros do simulador - frontend . . . . .                      | 64 |

# Capítulo 1

## Introdução

Programação em lógica constitui-se em um modelo de programação declarativo, baseado em um subconjunto de lógica de primeira ordem, cláusulas de Horn [31]. Neste tipo de modelo, o programador concentra-se na definição da solução do problema de forma lógica sem se preocupar com o controle ou como a solução vai ser encontrada. Um exemplo simples de programa em lógica é mostrado na Figura 1.1. Este exemplo é um programa escrito na linguagem Prolog [46] (mais popular para escrever programas em lógica) e define a concatenação de duas listas. O primeiro predicado define que o resultado da concatenação da lista vazia (representada como `[]`) com qualquer outra lista (representada pela variável `L`) é a própria lista. O segundo predicado trata do caso em que a primeira lista é não vazia (representada pelo termo `[X|L1]`, onde `X` é uma variável representando pelo menos um elemento da lista e `L1` é o restante da lista, que pode ser lista vazia). Neste segundo caso, o predicado simplesmente diz que se a concatenação de `L1` com `L2` for `L3` então, quando adicionado um elemento (`X`) a `L1`, este elemento vai ser adicionado, também, ao resultado `L3`.

```

concat([], L, L).

concat([X|L1], L2, [X|L3]) :- concat(L1, L2, L3).

```

Figura 1.1: Exemplo de programa prolog

Note que neste programa não há comandos que dizem "como" computar a concatenação. O programa apenas oferece a sua definição. E esta é uma das principais vantagens de programação em lógica. Como o controle está implícito na linguagem este tipo de modelo oferece maior flexibilidade aos sistemas de execução. Uma grande flexibilidade é oferecer a possibilidade de execução de programas em

ambientes paralelos, de forma que o usuário não precise se preocupar se o ambiente é paralelo. Em outras palavras, o usuário não precisa utilizar construções paralelas, existentes em outras linguagens imperativas, ou bibliotecas para paralelizar o seu programa. A paralelização é importante para programas em lógica porque, geralmente, programas em lógica são escritos para resolver problemas complexos na área de Inteligência Artificial, que consomem muitas horas ou mesmo meses de computação quando executados em uma única CPU.

As formas predominantes de exploração de paralelismo em programação lógica são paralelismo  $-OU$  e paralelismo  $-E$ . Paralelismo  $-OU$  é explorado em sistemas como Aurora [32] ou Muse [1]. Paralelismo  $-E$  é ainda classificado em paralelismo E-independente, e explorado por sistemas tais como &-Prolog [25] e &-ACE [24]; paralelismo E-dependente em Parlog's JAM [15], KLIC [47], e DDAS [43]; paralelismo de dados, em Reform Prolog [4]; e combinações de paralelismo  $-E$  e  $-OU$  como explorado pelos sistemas Andorra-I [3], Penny [35], ACE [23] e PALS [53]. Todos estes sistemas têm sido capazes de obter desempenho razoável em arquiteturas paralelas baseadas em barramento, tais como multiprocessadores Sequent Symmetry ou Sun.

A medida que arquiteturas mais modernas são desenvolvidas e a diferença de velocidades entre a CPU e a memória aumenta (atualmente as CPUs têm avançado em velocidade numa taxa muito maior do que a velocidade das memórias) surge a questão da eficiência destes sistemas paralelos de programação lógica nestas novas arquiteturas. Em multiprocessadores modernos, o desempenho depende principalmente das taxas de falha nas *caches* e pode ser limitado pelo *overhead* de comunicação introduzido pelos protocolos de comunicação utilizados para manter dados compartilhados coerentes.

Compartilhamento em sistemas paralelos de programação lógica tem característica complexa e pode ocorrer em várias circunstâncias dependendo do programa Prolog a ser executado em paralelo. O uso da variável lógica como canal de comunicação em aplicações que possuem paralelismo E-dependente, por exemplo, é um exemplo de compartilhamento de dados baseado num padrão produtor-consumidor. Nesse padrão o processador que instancia a variável (atribui-lhe um valor) escreve na variável e outro processador a lê. Esta comunicação pode ser feita por *streams* se a variável em questão for uma lista com vários elementos.

A segunda maior forma de compartilhamento em programação em lógica é de origem migratória. Esta forma de compartilhamento ocorre quando há sincronização entre processadores. A sincronização ocorre em tarefas tais como busca por trabalho de outros processadores ou quando um processador executa um predicado Prolog que pode causar um efeito colateral relacionado à execução seqüencial. Por exemplo, dois processadores podem querer ler e/ou escrever na tela ou em arquivo em ordens diferentes da original seqüencial. Outro exemplo, que acarreta um custo alto, seria um caso de sincronização onde processadores podem suspender e re-inicializar tarefas. Neste caso, pode acontecer destes processadores ficarem por longo tempo tentando buscar trabalho nas filas de outros processadores, lendo e escrevendo em estruturas compartilhadas. Um processador que produz uma tarefa escreve em uma das estruturas de dados compartilhadas, que mais tarde será modificada por um ou mais processadores que estão ociosos.

O compartilhamento de estruturas de dados de escrita introduz o problema de coerência de *caches*. A maior parte das máquinas paralelas utiliza protocolos de invalidação para manter as *caches* coerentes [22]. Neste protocolo, quando um processador escreve em um dado compartilhado, cópias deste dado que estão em outras *caches* são invalidadas. Se um dos processadores que teve o dado invalidado, posteriormente acessar o mesmo dado, terá que obtê-lo de volta para a sua *cache*. Em multiprocessadores escaláveis, este fato envolve uma comunicação.

Protocolos de atualização [34] são a alternativa principal para os protocolos baseados em invalidação. Em protocolos de atualização, sempre que um dado é escrito, cópias do novo valor são enviadas para outros processadores que compartilham o dado. Mais especificamente, considere o caso de paralelismo E-dependente, onde o padrão é similar a produtor-consumidor. Neste caso, um protocolo de atualização garante que o valor mais atualizado do dado está disponível para o consumidor. Enquanto com um protocolo de invalidação, o consumidor teria solicitar o dado ao outro processador que escreveu. Isso pode levar algumas centenas ou milhares de ciclos. Em casos deste tipo, sistemas paralelos de programação lógica claramente se beneficiariam de protocolos de atualização.

Mas não apenas padrões produtor-consumidor podem se beneficiar de protocolos de atualização. Sincronização envolvendo busca por trabalho, também pode se beneficiar de protocolos de atualização. Por exemplo, assim que um processador produzir trabalho os processadores ociosos teriam acesso à informação

imediatamente, sem ter que buscar a informação no processador que escreveu o dado. Um problema ocorre, porém, quando outros processadores recebem a atualização mas não podem utilizá-la porque outro processador ocioso já obteve aquele trabalho produzido.

Protocolos baseados em invalidação são mais populares do que protocolos baseados em atualização por causa do tráfego excessivo de mensagens produzido pelos protocolos de atualização. Em determinadas classes de aplicações, uma quantidade significativa de atualizações recebidas pelos processadores podem não ser utilizadas. Isto causa tráfego desnecessário, consome banda, e pode degradar o desempenho.

Neste trabalho, estudamos o comportamento de um protocolo híbrido na execução paralela de sistemas de programação lógica. Utilizamos 4 aplicações Prolog que, normalmente, são utilizadas como *benchmarks* nestes sistemas. O sistema de programação lógica utilizado é Andorra-I [3]. Este sistema explora a combinação de paralelismo E-dependente, uma forma restrita de paralelismo E-independente, e paralelismo -OU. Nossa objetivo com este estudo é saber se um protocolo híbrido consegue alcançar desempenho melhor do que protocolos baseados somente em invalidação ou em atualizações.

Utilizamos um simulador orientado por execução (*execution-driven*), de uma arquitetura de multiprocessador escalável. A versão de Andorra-I utilizada não contém otimizações e é a mesma que foi implementada originalmente para máquinas que utilizam barramento. Uma versão otimizada de Andorra-I que favorece o protocolo de invalidação foi desenvolvida [38]. Porém nosso objetivo neste trabalho é averiguar como o protocolo de coerência de memória pode afetar uma aplicação originalmente desenvolvida para memória centralizada. Comparamos nossos resultados com protocolos de invalidação e de atualização. Nossos resultados mostram que protocolos híbridos produzem um ganho de desempenho para todos os números de processadores e aplicações, independente do tipo de paralelismo existente na aplicação.

Nosso trabalho difere de outros estudos de desempenho de protocolos de coerência em sistemas paralelos de programação lógica. Tick e Hermenegildo [50] estudaram o comportamento de *caches* em sistemas que exploram apenas paralelismo E-independente em máquinas baseadas em barramento. Outros pesquisadores estudaram o desempenho de sistemas de programação lógica em

arquiteturas escaláveis tais como a DDM [36], porém não avaliaram o impacto de diferentes protocolos de coerência. Nossa trabalho inicial avaliou o impacto de protocolos de coerência de *cache* para um número menor de *benchmarks* e tamanho menor de *cache* [39]. Um protocolo híbrido com *threshold* fixo foi utilizado na avaliação. Também estudamos em detalhes o impacto do protocolo de invalidação em Andorra-I [40], o que nos permitiu implementar otimizações que melhoraram o desempenho [38, 41]. Silva *et al.* estudaram o impacto de diferentes parâmetros arquiteturais tais como: tamanho do bloco de *cache*, tamanho da *cache* (foi estudado até 256 Kbytes), tamanho do *buffer* de escrita e utilização de escritas concatenadas, utilizando protocolos de invalidação e atualização. Neste trabalho estudamos em detalhes o protocolo híbrido com vários valores de *threshold*, incluímos mais uma aplicação, e estudamos o comportamento do protocolo quando utilizamos tamanhos diferentes de *cache*, variando até 1 MByte.\*

Este trabalho está organizado da seguinte forma. No Capítulo 2 apresentamos as arquiteturas paralelas existentes e suas diferenças, concentrando-se em multiprocessadores escaláveis e protocolos de coerência de *cache*. No Capítulo 3 apresentamos as características de sistemas paralelos de programação lógica, explicando os tipos de paralelismo explorados e as principais estruturas de dados utilizadas em sistemas paralelos de programação lógica implementados para máquinas baseadas em barramento, com ênfase no sistema Andorra-I. No Capítulo 4 descrevemos a metodologia utilizada neste trabalho e o simulador da arquitetura multiprocessada. No Capítulo 5 apresentamos os resultados e discutimos o impacto do protocolo híbrido nas aplicações Prolog, comparando com os resultados utilizando apenas invalidação e apenas atualização. Finalmente, no Capítulo 6 concluímos o nosso trabalho e sugerimos trabalhos futuros.

---

\*Uma parte resumida deste trabalho foi publicada e apresentada na 16th International IASTED Conference on Parallel and Distributed Computing and Systems [18].

# Capítulo 2

## Arquiteturas Paralelas

Arquiteturas paralelas têm demonstrado ser uma das soluções mais efetivas para problemas que exigem alto poder computacional. As máquinas dc Von Neumann (monoprocessadores) têm chegado aos limites de minituarização conhecidos. Assim é necessário um conceito alternativo para atender a crescente demanda de processamento.

Exemplos de aplicações candidatas à execução em sistemas paralelos são o de processamento de dados da área de Biotecnologia, simulações de grande porte, aplicações maciças da área de Inteligência Artificial, entre outras. Elas exigem um nível maior de processamento e armazenamento de informações.

Arquiteturas paralelas podem atender a estas duas exigências. Pode haver redução do tempo total de processamento a partir da divisão de tarefas entre as diversas unidades de processamento do sistema. Podemos, também, obter o aumento da memória do sistema. A *cache* pode ter sua utilização otimizada, pois pode ocorrer a melhor situação entre alocação de dados na *cache* e processamento de dados, de forma a diminuir a probabilidade de desalocar um dado da *cache* em detrimento de outro, aumentando o desempenho do sistema.

De forma a compreender a metodologia apresentamos, a seguir, algumas características e noções referentes ao processamento paralelo.

### 2.1 Arquiteturas de computadores

A categorização definida por Flynn para arquiteturas de computadores é baseada nos fluxos de instruções e fluxos de dados [20]. O fluxo de instruções corresponde às tarefas que devem ser executadas e o fluxo de dados corresponde aos dados que devem ser manipuladas durante a execução destas tarefas. As categorias são apresentadas

a seguir.

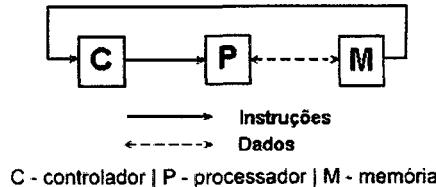

### SISD (Single Instruction Single Data)

Nas arquiteturas SISD um único fluxo de instruções é executado sobre um único fluxo de dados em um mesmo ciclo de relógio. Um processador é suficiente para desempenhar a tarefa. A Figura 2.1 exemplifica esta arquitetura.

Figura 2.1: Arquitetura SISD

As arquiteturas SISD podem ser representadas pelos computadores monoprocessados, que se encontram em larga escala no mercado, por exemplo, os PCs (computadores pessoais e estações de trabalho).

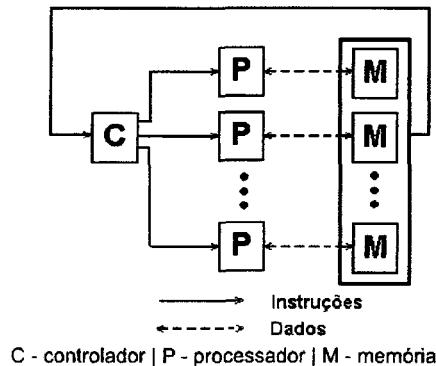

### SIMD (Single Instruction Multiple Data)

Nas arquiteturas SIMD um mesmo fluxo de instruções é executado sobre diferentes fluxos de dados em um mesmo ciclo de relógio. É necessário mais que um processador para executar esta tarefa. Cada um dos processadores estará em sincronia com os demais em relação às instruções, mas cada uma destas unidades as executará sobre um fluxo distinto de dados. A Figura 2.2 exemplifica esta arquitetura.

Figura 2.2: Arquitetura SIMD

Como exemplos de arquiteturas SIMD temos os processadores vetoriais e processadores matriciais. Um exemplo de aplicação capaz de se utilizar desta

arquitetura é a previsão meteorológica, onde os dados meteorológicos referentes a diferentes regiões seguem a mesma regra de cálculo.

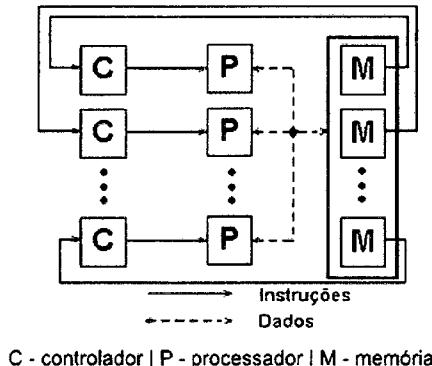

### **MISD (Multiple Instruction Single Data)**

Nas arquiteturas MISD vários fluxos de instruções são executados sobre um mesmo fluxo de dados em um mesmo ciclo de relógio. É necessário mais que um processador para que os diferentes fluxos de instruções sejam executados. A Figura 2.3 exemplifica esta arquitetura.

Figura 2.3: Arquitetura MISD

Aplicações capazes de usufruir desta arquitetura são raras. Um possível exemplo é a execução de múltiplos algoritmos de decriptografia sobre um mesmo dado criptografado ou a aplicação de vários filtros eletrônicos sobre um mesmo sinal recebido. A princípio não foram desenvolvidos sistemas que seguem este modelo arquitetural.

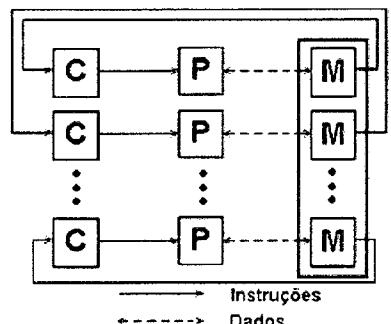

### **MIMD (Multiple Instruction Multiple Data)**

Nas arquiteturas MIMD fluxos de instruções diferentes podem ser executados com diferentes fluxos de dados de forma assíncrona. Para este tipo de arquitetura é necessário mais de um processador para que os diferentes fluxos de instruções sejam executados. A Figura 2.4 exemplifica esta arquitetura.

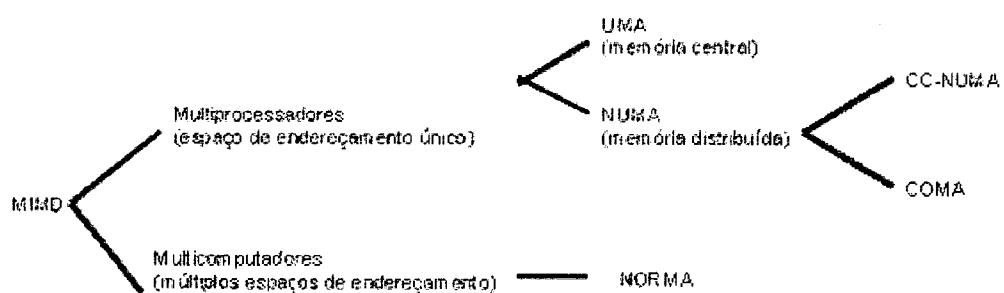

As arquiteturas MIMD podem assumir outras divisões [48]. Estas divisões foram baseadas a partir de modelos de espaços de endereçamento e das arquiteturas de memória, como mostra a Figura 2.5.

Apresentamos a seguir as características de cada uma destas divisões da arquitetura MIMD.

#### **Multiprocessadores (Memória compartilhada centralizada)**

Esta subdivisão da arquitetura MIMD é composta por arquiteturas fortemente

C - controlador | P - processador | M - memória

Figura 2.4: Arquitetura MIMD

Figura 2.5: Divisões das arquitetura MIMD

acopladas. Um barramento liga as unidades de processamento a uma memória logicamente única, compartilhada e centralizada. O espaço de endereçamento é único.

A seguir, apresentamos as características das arquiteturas UMA e NUMA, pertencentes a esta categoria, e que se diferenciam pela localização da memória.

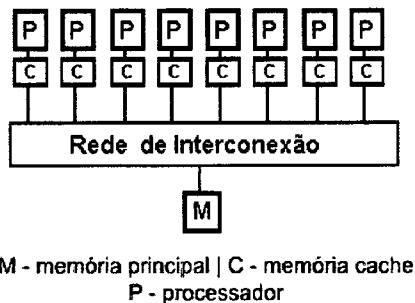

### **UMA (Uniform Memory Access)**

Na arquitetura UMA a memória compartilhada encontra-se a mesma distância de todas as unidades de processamento.

Para amenizar o acesso a memória principal é utilizada uma memória *cache*. Isto diminui a necessidade de acesso a memória principal, que é mais dispendioso que o acesso a *cache*, além de reduzir a contenção de memória.

A Figura 2.6 exemplifica a arquitetura UMA.

Figura 2.6: UMA - *Uniform Memory Access*

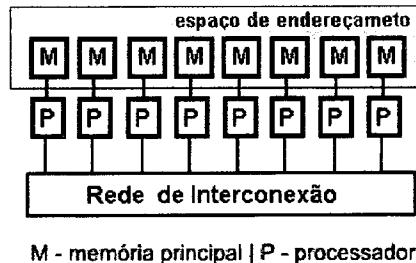

### **NUMA (NON - Uniform Memory Access)**

Na arquitetura NUMA a memória é fisicamente distribuída e logicamente compartilhada. Cada processador tem sua memória privativa, existindo um controlador implementado em hardware responsável pela coerência dos dados compartilhados.

Nesta arquitetura o dado é endereçado a uma das memórias do sistema. Uma vez definido o endereçamento, ele não pode ser alterado, sendo considerado, então, como estático. Assim, o desenvolvimento destas arquiteturas é simplificado, mas pode resultar em queda de desempenho caso o dado seja endereçado a uma memória remota e o sistema não esteja otimizado para acessos remotos.

A Figura 2.7 exemplifica a arquitetura NUMA.

### **COMA (Cache Only Memory Access)**

A arquitetura COMA é fisicamente semelhante a NUMA (Figura 2.7). A

Figura 2.7: NUMA - *NON Uniform Memory Access*

diferença está no processo de endereçamento da memória que é dinâmico. Assim, o dado endereçado inicialmente a uma memória pode ser migrado para uma outra que, de acordo com o algoritmo de coerência utilizado, possa aumentar o desempenho do sistema por proximidade ao processador que fará uso mais eficiente deste dado.

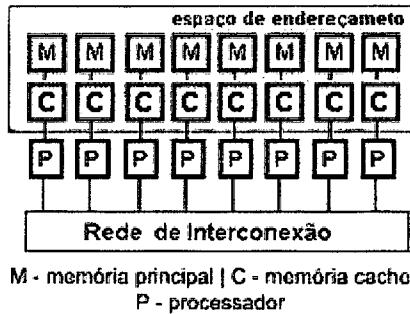

#### CC-NUMA (*Cache Coherente - NON Uniform Memory Access*)

A arquitetura CC-NUMA segue o mesmo conceito arquitetural de COMA. A diferença está nas *caches* incluídas entre a memória principal e os processadores para aumentar o desempenho da arquitetura.

A Figura 2.8 exemplifica a arquitetura CC-NUMA.

Figura 2.8: CC-NUMA - *Cache Coherente - NON Uniform Memory Access*

#### NORMA (Multicomputadores)

A arquitetura NORMA (*Non-Remote Memory Access*), também denominada multicomputadores, é uma subdivisão das arquiteturas MIMD (Figura 2.5). Ela é fracamente acoplada. Cada processador tem sua memória privativa. Os dados comuns a estas unidades são trocados a partir de uma rede de interconexão.

Como a memória é privativa é necessário que haja uma forma de obter os dados necessários ao processamento local em cada processador e entregar os dados requisitados por alguma outra unidade. Este mecanismo pode ser implementado em

software [28, 21], hardware ou híbrido [44].

Em geral, o desempenho de NORMA é menor quando comparado aos multiprocessadores. A rede de interconexão utilizada na comunicação nestas arquiteturas, normalmente, é mais lenta que os barramentos utilizados em sistemas multiprocessadores. O módulo controlador implementado em hardware em sistemas multiprocessadores, também, é mais eficiente que os implementados em software em sistemas multicomputadores.

Em contrapartida, a conexão estabelecida por redes torna a inserção de novos processadores bastante flexível, tornando o sistema escalável. Ao contrário dos sistemas multiprocessadores em que a comunicação por barramento não permite interconexão de outros processadores além dos pré estabelecidos. Mas as tecnologias de interconexão sofrem com as contenções da rede, tornando esta escalabilidade limitada.

Em termos de custo de aquisição os multicomputadores são mais acessíveis. O desenvolvimento em grande escala de PCs e estações de trabalho torna o custo menor. Sistemas multiprocessadores são desenvolvidos em uma escala bem menor e, normalmente, utilizam componentes de hardware específicos, tornando o custo de um sistema com o mesmo número de processadores bem maior.

## 2.2 Modelos de consistência

Os modelos de consistência têm por objetivo determinar quando os dados compartilhados devem estar presentes junto às unidades de processamento do sistema. O modelo de consistência dá subsídios ao protocolo de coerência para determinar em que momento o dado compartilhado deve ser enviado.

O modelo de consistência influí diretamente no desempenho do sistema.

Apresentamos a seguir uma evolução dos modelos de consistência.

### Modelo de consistência seqüencial

O modelo de consistência seqüencial estabelece que as memórias do sistema devem operar como em um modelo monoprocessado. Toda alteração executada por um processador do sistema deve ser imediatamente observada pelas demais unidades. Desta forma, todo acesso à memória compartilhada, seja leitura ou escrita, só pode ser executado quando uma instrução de escrita anterior tiver sido visto pelas demais unidades do sistema.

Os sistemas que utilizam este modelo de consistência têm de executar constantemente os protocolos associados ao modelo, tornando o sistema ineficiente e causando um *overhead* nas redes de interconexão.

### **Modelos de consistência relaxados**

O modelo de consistência seqüencial precisava ser otimizado para se obter melhor desempenho. A programação paralela tem características que permitiam executar corretamente os programas sem a necessidade de tornar o acesso aos dados compartilhados conhecidos por todas as unidades de processamento no mesmo instante em que é alterado.

Os modelos de consistência relaxados trabalham com estas características, como a necessidade de sincronização somente em determinados momentos. Existem vários modelos de consistência relaxados que atuam de forma diferente para aumentar o desempenho. Alguns deles são apresentados a seguir.

#### ***Processor consistency***

O modelo *processor consistency* é semelhante ao modelo seqüencial. A diferença está nas alterações executadas por um determinado processador que não precisam ser imediatamente visualizadas pelas demais unidades do sistema logo após o acesso. Assim, somente a ordem de escrita está restrita à unidade que realizou a operação. As leituras em outras unidades de processamento podem ser executadas sem as restrições estabelecidas no modelo de consistência seqüencial, desde que sejam em regiões de memória compartilhada diferentes.

Desta forma, o sistema fica capacitado a operar com algumas técnicas para o aumento do desempenho, como *write buffers* e *pipelining*.

#### ***Release consistency***

O modelo *release consistency* considera o fato de que o programador pode determinar em que ponto a sincronização dos dados é necessária. Para tanto são estabelecidas primitivas de sincronização que definem quando deve haver uma sincronização.

As primitivas mais comumente utilizadas são: *lock-acquire*, *lock-release*, e *barriers* (barreiras). As primitivas *lock-acquire* e *lock-release* estabelecem os pontos de sincronização e as seções críticas. Nessas regiões somente um processador está capacitado a executar por vez, protegendo, então, as variáveis compartilhadas associados a esta área.

O *lock-acquire* controla o acesso a dados compartilhados. Antes do início da

execução é verificado se alguma outra unidade de processamento tem a variável de *lock* sob sua custódia. Em caso positivo, a unidade requisitante espera a liberação do *lock*. A partir da primitiva *lock-release* a região protegida é liberada e é realizada a sincronização com os demais processadores. Ela é invocada quando é terminado o processamento dentro da região crítica por parte de um dos processadores.

As primitivas de barreiras são utilizadas quando as unidades de processamento precisam ter seu processamento emparelhado. Geralmente, são utilizadas para definir etapas. Elas impedem que a aplicação continue até que todos os processos tenham atingido a barreira.

As trocas de informações entre os elementos de processamento só ocorrem nas chamadas ao *lock-release* ou na saída de uma barreira. Este fato aumenta o desempenho, uma vez que diminui a quantidade de dados que percorrem a rede de interconexão que acontecem nestes momentos, e não a cada acesso a memória compartilhada.

#### ***Lazy release consistency***

O modelo *lazy release consistency* é semelhante ao modelo *release consistency*, porém, ainda mais relaxado.

Quando um dado é alterado não é necessário sincronizar imediatamente. Estes dados são enviados somente se a próxima unidade necessitar utilizá-los dentro de mesma região crítica (*acquirer*). Desta forma, existe redução da propagação de dados entre os processos e a diminuição do *overhead* da rede de interconexão.

Em contrapartida, o desenvolvedor tem a responsabilidade de estabelecer os pontos de sincronização para leitura, diferente dos outros modelos de consistência, porque este modelo garante que os dados estarão coerentes apenas durante a execução de um *lock-acquire*. Conseqüentemente, pontos de sincronização extras devem ser introduzidos no código, o que pode tornar o sistema deficiente.

## **2.3 Modelos de programação**

Apresentamos, a seguir, alguns dos modelos de programação para arquiteturas paralelas. Estes são utilizados pelo programador para desenvolver os programas voltados a estas arquiteturas. Estes modelos definem o nível de complexidade do programa e pode influenciar inclusive no desempenho da aplicação.

### **Modelo de programação para memória compartilhada**

O modelo de programação para memória compartilhada, em princípio, foi desenvolvido para arquiteturas de memória centralizada. Assemelha-se bastante ao modelo de programação seqüencial, tornando simples a tarefa do desenvolvedor. Dependendo do modelo de consistência utilizado é necessária a utilização das primitivas para a definição dos pontos de sincronização.

Os custos de desenvolvimento e manutenção dos programas com o modelo de programação de memória compartilhada são menores.

Entretanto, em relação ao custo de hardware, as máquinas de memória compartilhada são desenvolvidas em menor escala, tornando o custo de aquisição mais alto.

### **Modelo de programação para memória distribuída**

O modelo de programação para memória distribuída é também conhecido por troca de mensagens. Quando necessário acessar dados coerentes, as alterações são enviadas por mensagens, exigindo um protocolo de comunicação controlado pelo programador.

O trabalho de desenvolvimento de programas paralelos pelo modelo de memória distribuída é mais árduo em comparação ao modelo de memória compartilhada. Isto porque é necessário declarar explicitamente os métodos para troca de dados. A manutenção, em geral, é mais complexa tornando os custos de desenvolvimento e de manutenção maiores.

Entretanto, em geral, os custos com aquisição de hardware são inicialmente menores, pois as máquinas são ligadas em rede e podem ser máquinas construídas em larga escala. Também oferecem uma escalabilidade maior, já que as redes de interligação permitem a inserção de novos processadores facilmente.

### **Discussão sobre o modelo de programação para memória compartilhada distribuída (DSM)**

Sistemas de memória compartilhada distribuída tem por objetivo oferecer as facilidades encontradas no modelo de programação para memória compartilhada junto à simplicidade de aquisição de hardware e a escalabilidade encontradas nos sistemas de memória distribuída.

Em contrapartida, determinadas características tornam o modelo de programação ligeiramente diferente do modelo de programação para sistemas de memória compartilhada. Por exemplo, para a leitura de dados compartilhados é necessário que os dados estejam coerentes através da invocação de uma primitiva

de sincronização em sistemas DSM, já que a memória é fisicamente distribuída, ao contrário dos sistemas de memória compartilhada.

O modelo DSM realiza a troca de mensagens baseada em unidades de coerência estabelecidas pelo sistema, normalmente alguma utilizada pelo sistema operacional (páginas) ou pelo hardware (linhas de *cache*).

Devido às características específicas de cada aplicação, o desempenho com este modelo de programação provavelmente não é maior que o obtido no programa desenvolvido com o modelo de programação de memória distribuída da forma mais otimizada. Isto porque a responsabilidade pela migração dos dados é do sistema e não do programador. Como estes modelos utilizam uma unidade de coerência do sistema, a qual pode ser grande, pode ocorrer que nem todos os dados enviados sejam acessados, incrementando o *overhead* na rede de interconexão desnecessariamente.

## 2.4 Problemas associados a multiprocessadores

No desenvolvimento de sistemas multiprocessadores (Figura 2.5) é necessário avaliar quais os possíveis pontos que podem afetar o desempenho das aplicações. Os principais pontos são a memória e a rede de interconexão. Os problemas associados a estes elementos estão definidos a seguir.

### Contenção de memória

A contenção de memória ocorre quando várias unidades de processamento acessam um mesmo *chip* de memória em um mesmo instante. Como este recurso é restrito, é necessária a serialização dos acessos, acarretando assim a contenção de memória.

Em sistemas multiprocessados os dados podem ser compartilhados por vários processos. O protocolo de coerência de memória pode estar restringindo o acesso a memória ou a alguma região dela para proteger os dados, possibilitando a perda de desempenho.

### Contenção de comunicação

A contenção de comunicação ocorre por causa do número limitado de canais entre os processadores do sistema multiprocessado. Quando existe um número de requisições maior que a capacidade oferecida pelos canais existentes ocorre a contenção de comunicação.

Em sistemas multiprocessadores o canal de comunicação, seja ele um barramento

ou uma rede de interconexão, é limitado e compartilhado entre os vários processadores do sistema, possibilitando a contenção e perda do desempenho.

### **Latência de rede**

Em um sistema multiprocessado os processadores estão interligados por uma rede de conexão. O tempo decorrente entre o envio de uma requisição de um processador ao outro é denominado latência de rede.

A latência de rede é extremamente influenciada pela tecnologia de rede de interconexão utilizada e pela quantidade de dados que trafegam por ela.

## **2.5 Classes de coerência de memória**

Em sistemas paralelos existe a necessidade de determinar como os dados compartilhados serão acessados pelas diversas unidades de processamento. Para tanto são desenvolvidos protocolos que devem ser seguidos por todos os elementos da arquitetura paralela. Esta tarefa é denominada coerência de *cache*.

Em geral, estes protocolos podem pertencer a duas classes de coerência de *cache*: migração e replicação.

A técnica de migração envia o dado alterado por uma unidade de processamento a uma outra, enviando, também, a custódia da administração do dado. Quando outra unidade de processamento necessitar do dado ela requisitará ao nó que o tem sob custódia.

A técnica de replicação é definida quando um dado não é administrado por uma única unidade de processamento. O dado é replicado nas unidades de processamento que fazem parte do sistema.

Estes dois procedimentos são críticos e a sua utilização afeta o desempenho dos sistemas compartilhados. A classe de migração tem uma taxa de tráfego de dados menor que a encontrada na classe de replicação. O dado migra de um elemento de processamento diretamente para um outro quando requisitado. Na classe de replicação quando ocorre a alteração de um dado, ele deve ser enviado aos demais nós do sistema, aumentando o tráfego de dados pela rede.

Sistemas atuais utilizam a classe de replicação, pois as redes de interconexão são lentas, tornando o desempenho extremamente deficiente quando necessário o uso constante da rede para acesso aos dados compartilhados e espera pela chegada destes, o que ocorre no caso das classe de migração.

Para sistemas multiprocessados, ainda existem duas classes de coerência de memória: *directory-based* [29] e *snooping* [27].

Em *directory-based* o estado do compartilhamento do bloco de memória compartilhado está presente em uma estrutura física denominada *directory*. Em *snooping* toda *cache* tem uma cópia dos blocos de memória compartilhados, tornando o estado de compartilhamento não centralizado.

*Snooping* diminui os possíveis gargalos existentes no acesso a estrutura *directory* existente na classe *directory-base*. Em contrapartida, aumenta o fluxo de dados na rede de conexão. *Snooping*, também, aumenta a escalabilidade, já que uma estrutura *directory* limita o número das memórias *cache* que estão distribuídas no sistema.

## 2.6 Protocolos de coerência de memória

Em sistemas paralelos para manter os dados coerentes é necessário um conjutno de regras que mantenham atualizados os dados compartilhados nos elementos de processamento. Para tanto são desenvolvidos os protocolos de coerência de memória.

Estes protocolos influenciam diretamente no desempenho do sistema. As influências dos protocolos dependem das características da aplicação e das tecnologias de rede utilizadas.

A seguir apresentamos os principais protocolos de coerência de memória: invalidação, atualização e híbrido.

### 2.6.1 Invalidation (*invalidate*)

No protocolo de invalidação [22] quando uma unidade de processamento executa uma operação de *release*, as demais unidades são informadas, através de mensagens, quais elementos foram alterados. Não são enviadas as modificações propriamente ditas.

Em uma operação de *acquire* o processador é responsável por requisitar os dados que estão indicados como alterados às demais unidades do sistema. Este protocolo tem como vantagem a diminuição da transferência de dados na rede de interconexão. Entretanto, quando for necessária a aquisição de dados modificados o processador tem que esperar até que os dados sejam enviados e atualizados localmente, ficando em modo de espera.

### 2.6.2 Atualização (*update*)

No protocolo de atualização [34] quando uma unidade de processamento executa uma operação de *release* ela repassa às demais unidades todos os dados alterados.

A vantagem deste protocolo é a presença imediata dos dados quando um processador acessa o dado compartilhado. Dessa forma o protocolo de atualização elimina o período de espera pelos dados remotos.

Este protocolo tem como desvantagem o *overhead* na rede de conexão, que aumenta consideravelmente em relação ao protocolo de invalidação. Além disso, várias das alterações recebidas não são acessadas pelos processos, tornando muitas destas atualizações desnecessárias.

### 2.6.3 Híbrido (*competitive update*)

O protocolo híbrido [27] visa encontrar um equilíbrio das vantagens proporcionadas pelos protocolos de invalidação (menor tráfego de dados pela rede de conexão) e de atualização (menor tempo de espera pelos dados remotos), se adaptando melhor as necessidades da aplicação.

Ele se baseia na heurística de que se um dado não for acessado durante  $n$  atualizações, onde  $n$  é o valor do *threshold*, então, aquele dado pode ser invalidado. Ou seja, não é mais útil ao processador nos próximos tempos.

Após a atualização de um dado, o protocolo de atualização volta a atuar nele durante os  $n$  *thresholds*.

A maior parte dos processadores atuais utiliza protocolo de invalidação, porque a atualização produz uma quantidade excessiva de mensagens que pode causar contenção na rede de interconexão. Multiprocessadores baseados em barramento que usam o processador DEC Alpha AXP21064 [49] utilizam protocolo híbrido.

## 2.7 Tipos de *miss*

Quando a memória *cache* é acessada, é possível que um dado, que esteve presente anteriormente, não esteja mais presente naquele momento. É necessário, então, requisitá-lo em outro nível de *cache* ou na memória principal. À ausência do dado na *cache* denominamos *cache miss* (falha na *cache*).

Em sistemas onde os dados são compartilhados e as memórias são distribuídas pode haver outros tipos de *miss*, além dos já existentes em sistemas

monoprocessados. A seguir estão definidos os tipos de *miss* e suas características.

### 2.7.1 *False miss*

Um *false miss* (falha por falso compartilhamento) ocorre quando o sistema entende que uma unidade (página, bloco de memória ou linha de *cache*) da memória não está coerente em relação ao sistema compartilhado. Porém o dado acessado, que é uma parte da unidade, não estava incoerente.

Isto ocorre principalmente quando o sistema utiliza unidades de coerência com um tamanho considerável. Aumentando o tamanho da unidade aumenta também a probabilidade de existirem dados que não foram alterados. Isso porque a unidade possui maior capacidade de armazenar dados.

A existência de *false miss* pode gerar aumento desnecessário do tráfego na rede e o aumento da latência pela espera dos dados remotos.

### 2.7.2 *True miss*

Um *true miss* ocorre quando um dado local não está coerente em relação ao sistema compartilhado. É necessário requisitar o dado modificado mais recentemente.

Neste tipo de falha é necessário requisitar os dados. Assim, podemos usar o *true miss* como parâmetro para avaliar o quanto o protocolo de coerência está sendo eficiente em diminuir o número destas falhas.

### 2.7.3 *Eviction miss*

*Eviction miss* (ou *replacement miss*) ocorre quando um sistema troca linhas na *cache* e posteriormente precisa acessá-las novamente.

Em sistemas hardware DSM, o *eviction miss* pode comprometer o sistema tanto quanto o *false miss*. A princípio, uma solução é aumentar o tamanho da memória *cache* em hardware.

### 2.7.4 *Cold start miss*

*Cold start miss* ocorre na primeira referência a um bloco da *cache*. Isto é, a falha ocorre porque o bloco nunca esteve na memória, por estar no início da execução.

Este dado é importante para determinar o quanto o sistema está capacitado a melhorar o desempenho a partir do comportamento da *cache*, já que estas falhas são obrigatórias.

### 2.7.5 *Drop miss*

*Drop miss* ocorre quando o processador referencia uma palavra que foi invalidada pelo protocolo híbrido quando ele atua como protocolo de invalidação.

# Capítulo 3

## Programação Lógica-Paralela

Neste capítulo apresentamos conceitos básicos de sistemas paralelos de programação lógica, mecanismos de extração de paralelismo implícito, tipos de paralelismo implícito e modelos de implementação. Apresentamos, também, alguns sistemas que exploram paralelismo em programação lógica, enfocando no sistema Andorra-I, base para o estudo realizado nesta tese.

### 3.1 Conceitos Básicos

Computação lógica segue o paradigma da programação declarativa, onde o algoritmo é definido por um conjunto de regras [33, 31]. Estas regras expressam relações condicionais a partir de uma ou mais cláusulas. A partir de uma base de dados que contém fatos - cláusulas sempre verdadeiras - o processamento é realizado sendo possível gerar as conclusões desejadas.

Nesta metodologia o programador se concentra na descrição do problema, diminuindo consideravelmente o tempo dedicado aos mecanismos de computação, presente em outros modelos de programação, como o funcional ou imperativo.

Os programas gerados por este modelo são mais simples de desenvolver e compreender. Estas são características importantes em sistemas com alto nível de complexidade, presentes em áreas como Inteligência Artificial e Biotecnologia. A linguagem de programação mais conhecida que segue este modelo é o Prolog [11, 13, 6, 9].

Uma característica deste modelo de programação é a capacidade de parallelizar seus programas de forma implícita [37], não exigindo intervenção no código por parte do programador. Outros modelos de programação, como o funcional ou imperativo, exigem a participação do desenvolvedor na definição do paralelismo.

A paralelização implícita é possível já que as regras que constituem o programa lógico são constituídas por cláusulas e estas são constituídas por termos que se relacionam. Cada qual pode ter seu processamento distribuído em processadores de uma arquitetura paralela. Dentro destas características é possível dividir a metodologia de paralelização em dois tipos: paralelismo *-OU* e paralelismo *-E*.

O paralelismo do tipo *-OU* está associado ao processamento de diferentes cláusulas que correspondem à definição do problema. Estas cláusulas podem ser processadas de forma independente. Por exemplo:

- (1) `tio(A,B) :- pai(A,X), irmao(X,B).`

- (2) `tio(A,B) :- mae(A,X), irmao(X,B).`

Figura 3.1: Exemplo de algoritmo de programação lógica - definição de *tio*

Para avaliar a regra *tio(X,Y)* o processamento da cláusula (1) do algoritmo apresentado na Figura 3.1 pode ser delegado a um processador diferente daquele que executará a cláusula (2) deste mesmo algoritmo.

O paralelismo do tipo *-E* visa executar os diferentes termos de uma mesma cláusula paralelamente. Por exemplo:

- (3) `irmao(A,B) :-`

`pai(A,X), pai(B,X),`

`mae(A,Y), mae(B,Y).`

Figura 3.2: Exemplo de algoritmo de programação lógica - definição de *irmão*

Na cláusula (3) do algoritmo descrito na Figura 3.2 a regra *irmao* é composta por quatro termos que inicialmente podem ser avaliados em processadores diferentes.

O paralelismo do tipo *-E* pode, ainda, ser subdividido em outras duas categorias: o paralelismo *-E* dependente (DAP) e o independente (IAP).

Em DAP os termos que compõem a cláusula compartilham variáveis comuns, de tal forma que é necessário um pré-processamento de um dos termos para capacitar a execução do próximo. Esta situação ocorre quando a resposta obtida de um dos termos é utilizada como base de avaliação ao outro termo na mesma cláusula. Exemplificamos o paralelismo DAP pela cláusula (1) do algoritmo descrito na Figura 3.1, onde para executar o termo *irmao* é necessário que a variável *X* tenha o resultado obtido da cláusula *pai*. Este tipo de execução caracteriza um padrão produtor-consumidor.

Em IAP os termos que compõem a cláusula podem ser executados independentemente, pois ainda que os termos compartilhem as variáveis estas não servem de base para a execução dos demais. Um exemplo de paralelismo *-E* independente é mostrado no exemplo da Figura 3.3.

```

quicksort([X|L],S) :-

partition(X,L,L1,L2),

quicksort(L1,S1),

quicksort(L2,S2),

append(S1,[X|S2],S).

```

Figura 3.3: Exemplo de algoritmo de programação lógica - *quicksort*

Esta figura mostra uma parte da solução que ordena elementos em uma lista utilizando o algoritmo *quicksort*. Neste pequeno programa, particionamos a lista de entrada *L*, utilizando o primeiro elemento da lista *X* como pivô, e geramos duas novas listas, *L1* (contém todos os elementos de *L* menores ou iguais que *X*) e *L2* (contém todos os elementos maiores do que *X*). Em seguida, as ordenações de *L1* e *L2* podem ser feitas em paralelo, dando origem ao paralelismo *-E* independente.

Sistemas foram desenvolvidos para aproveitar o paralelismo *-OU* como o Aurora [8, 10] e MUSE [1]. Outros sistemas aproveitam o paralelismo do tipo *-E* independente, como o &-Prolog [25], e outros o paralelismo do tipo *-E* dependente, como o Parlog [16]. Existem ainda sistemas que estão capacitados a aproveitar os dois tipos de paralelismo como o Andorra-I [3].

Para executar um programa lógico em uma arquitetura paralela precisamos de um *framework*, sendo este composto por dois módulos principais: a máquina virtual Prolog e o escalonador de tarefas.

A máquina virtual Prolog tem a função de executar as tarefas lógicas. A função do escalonador é distribuir eficientemente as tarefas entre os vários processadores da arquitetura paralela, de forma que a granulosidade das tarefas não seja tão pequena, o que aumentaria a comunicação na rede, e nem tão grande, o que possibilharia que alguma máquina se tornasse ociosa. O escalonador, também, é capaz de otimizar o processo de execução, fazendo com que tarefas associadas às condições que não tenham sido satisfeitas não sejam executadas.

### 3.2 Andorra-I

Andorra-I [42] é um sistema capaz de executar programas lógicos desenvolvidos em Prolog e distribuir as tarefas entre diversos processadores de uma arquitetura paralela. A principal diferença quando comparado a outros sistemas já desenvolvidos é a capacidade de explorar os dois tipos de paralelismo, presentes em aplicações reais e consequentemente obtendo boas taxas de desempenho.

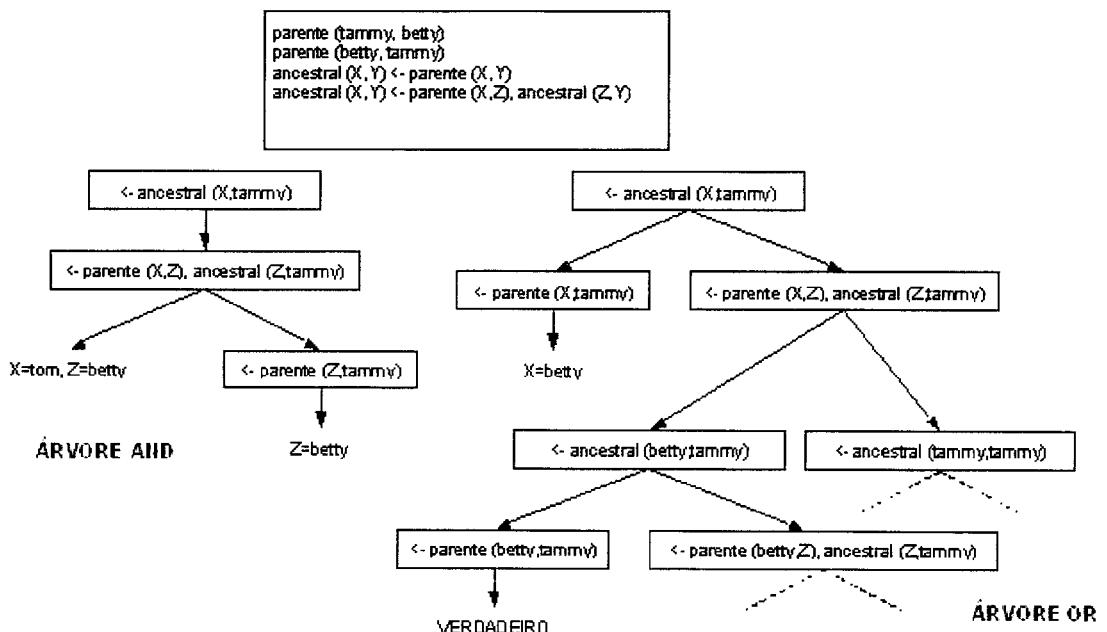

Andorra-I estrutura o programa lógico como uma árvore. Cada nó desta árvore corresponde a uma tarefa a ser executada, sendo esta uma cláusula ou um termo de uma cláusula. Os nós que se seguem a este são as tarefas derivadas do nó que o gerou. Quando os resultados são gerados estes são repassados ao nó que os gerou, sendo esta tarefa denominada *backtracking*. A Figura 3.4 apresenta um exemplo de árvore de tarefas.

Figura 3.4: Exemplo de árvores de tarefas -E e -OU

A partir desta estrutura o sistema é capaz de determinar quais são as tarefas *-OU* e *-E*. Na árvore *-E* da Figura 3.4 os termos *parente* e *ancestral* da regra *ancestral* são separados. Já na árvore *-OU* são separadas as duas cláusulas referentes a regra *ancestral*.

A partir desta estrutura os escalonadores são capazes de determinar quais são as tarefas a serem distribuídas pelos processadores e como devem ser executados de acordo com o tipo de paralelismo.

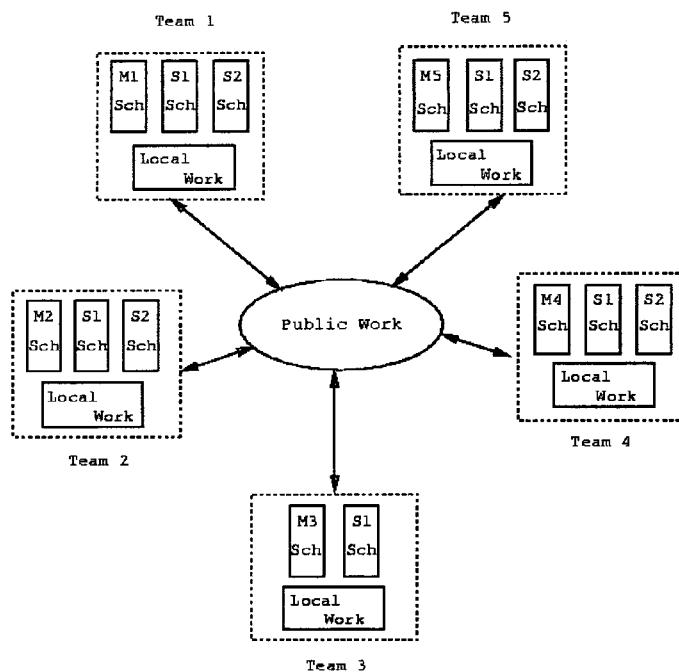

Em Andorra-I cada processador é denominado *worker*, sendo este capaz de executar as tarefas lógicas delegadas pelo escalonador. Os *workers* podem ser agrupados em *teams*, onde cada *team* tem um processador *master*. Dentro de um *team* os *workers* cooperam de forma a explorar o paralelismo do tipo *-E*, enquanto os *teams* cooperam entre si de forma a explorar o paralelismo do tipo *-OU*.

O escalonador administra uma área de memória comum a todos os processos, onde devem estar presentes os resultados obtidos das tarefas delegadas a outros processadores e as tarefas que ainda devem ser executadas.

Associado a cada processador existe, também, uma área de memória privativa. Ela contém os dados referentes às tarefas atribuídas ao processador.

A Figura 3.5 apresenta a estrutura seguida pelo sistema Andorra-I.

Figura 3.5: Estrutura do sistema Andorra-I

O modelo estabelecido por Andorra-I para aproveitar o paralelismo *-OU* é o SRI [55], onde cada *team* coopera com o escalonador na tarefa de procura de tarefas a serem processadas, estas associadas a uma sub-árvore da estrutura citada anteriormente. Este escalonador foi desenvolvido na universidade de Bristol [2].

Andorra-I divide a memória compartilhada em vários segmentos com diferentes funcionalidades. Esta divisão permite a melhor administração dos dados de acordo com as tarefas do *framework*, como a sincronização das tarefas. Descrevemos estas

áreas a seguir, incluindo suas funcionalidades.

*Estrutura de dados do escalonador-OU.* O escalonador -OU de Bristol utiliza três estruturas compartilhadas: um conjunto de campos para cada ponto de escolha e duas estruturas de dados com variáveis globais. Esta região de memória engloba estas estruturas.

*Estrutura de dados das tarefas (workers).* Estruturas necessárias para controlar as variáveis associadas ao controle das tarefas a serem executadas. O acesso a esta estrutura está normalmente relacionado ao escalonamento -E.

*Vetor de locks.* Usado para estabelecer a relação entre uma determinada região de memória e uma variável de *lock*. O acesso é realizado sempre que há a necessidade de um *lock*. Esta área é necessária nas simulações realizadas neste trabalho, já que o simulador não realiza as instruções de sincronização do MIPS. A estrutura utiliza o mecanismo de *hashing* para diminuir o efeito de perda de desempenho.

*Espaço de código.* Espaço para o código compilado. Durante a execução são realizados acessos somente de leitura.

*Espaço do heap.* Utilizado de forma comum em sistemas Prolog. Armazena estruturas e variáveis. Ele aumenta durante o avanço da execução da tarefa e diminui no *backtracking* referente ao término de um objetivo.

*Espaço de objetivos (goal frame).* Este espaço armazena argumentos para desenvolver os objetivos, variáveis para ligar os vários objetivos e campos de controle críticos. O sistema tenta reutilizar os objetivos conforme a execução.

*Pilha do ponto de escolha (choicepoint).* Armazena os ponteiros para o topo das pilhas e *flags* que são alterados de acordo com a execução do sistema.

*Pilha de trail.* Região acessada somente por aplicações que tenham tarefas do tipo -OU. Contém variáveis com múltiplas atribuições e condições referentes ao *binding*.

*Binding array.* Região acessada somente pelas aplicações que tenham tarefas do tipo OU.

*Outras variáveis compartilhadas.* Armazena outras variáveis compartilhadas, como descritores de arquivos.

# Capítulo 4

## Metodologia de Avaliação

Este trabalho visa avaliar o comportamento de sistemas de programação lógica paralela variando os protocolos de coerência de memórias compartilhadas, complementando trabalhos já existentes como [45] e [14]. A maioria dos trabalhos apresentados até então tem avaliado o comportamento de aplicações científicas.

Procuramos observar se o protocolo híbrido pode gerar os melhores desempenhos em sistemas lógicos paralelos, já que ele procura oferecer o melhor dos outros dois protocolos: invalidação e atualização.

A avaliação é feita em sistemas multiprocessadores. Isso porque as características de desempenho dos multiprocessadores são mais adequadas para sistemas de programação lógica paralela. Trabalhos anteriores indicam que arquiteturas de sistemas multicamputadores ainda precisam ser aprimoradas para comportar sistemas de programação lógica paralela [19], pois existem perdas de desempenho constatadas.

Outros trabalhos mostram que o desempenho em sistemas multicamputadores podem ser otimizados por novas técnicas, mas não obtiveram uma resposta mais significativa que as encontradas em sistemas multiprocessadores. Principalmente devido à tecnologia de rede [12].

Por estes motivos concentramos os esforços em arquiteturas multiprocessadas, apesar da grande flexibilidade encontrada em sistemas de memória distribuída.

### 4.1 Simulador MINT

Utilizamos um simulador orientado à execução, que viabiliza a execução de aplicativos compilados para uma arquitetura MIPS R3000 multiprocessada, DASH-like [30], com 24 processadores, diretamente conectados. Cada nó da máquina

simulada contém um único processador, um *buffer* de escrita, uma *cache*, memória local, um diretório *full-map* e uma rede de interconexão. Este simulador foi desenvolvido na universidade de Rochester e utiliza como *front-end* o MINT (Mips INTerpreter), desenvolvido por Veenstra e Fowler [52, 51]. Ele simula a arquitetura MIPS e gera referências à memória, às quais são repassadas ao *back-end*, desenvolvido por Bianchini, Kontothanassis e Veenstra [5] para simular os sistemas de memória e de interconexão. Quando o módulo *back-end* termina a tarefa ele envia um sinal ao *front-end*, indicando o resultado e que pode continuar a tarefa.

As aplicações a serem executadas sobre o simulador devem ser compiladas para a arquitetura MIPS R3000 e os endereços devem ser gerados estaticamente.

Nas simulações realizadas cada elemento de processamento foi definido como tendo uma *cache* de 512 kbytes mapeada diretamente, com blocos de 64 *bytes*. Todas as instruções e acessos a *cache* realizados com sucesso duram 1 ciclo de relógio. Falhas de leitura suspendem o processador até que a leitura seja completada. Escritas são armazenadas em um *buffer* de escrita com 16 entradas e duram 1 ciclo de relógio. A exceção encontra-se quando o *buffer* está cheio. Neste caso, o processador espera até que exista uma entrada livre. Leituras podem passar a frente de escritas no *buffer*. Os dados compartilhados são distribuídos pelas memórias de forma intercalada no nível de bloco (64 bytes).

Um barramento de memória com metade da velocidade de processamento conecta os principais componentes de cada nó da máquina. Uma nova operação no barramento pode começar a cada 34 ciclos de processador. Um módulo de memória pode prover a primeira palavra de uma linha de *cache* 20 ciclos após o pedido ser feito. Cada palavra subsequente é enviada a cada 2 ciclos.

A rede de interconexão é uma grade bidirecional *wormhole-routed*, com roteamento ordenado por dimensão. A velocidade da rede é a mesma do processador. Nós de chaveamento introduzem um atraso de 4 ciclos ao cabeçalho de cada mensagem. A largura da rede é de 16 bits, equivalente a largura de banda de memória.

Estes parâmetros são considerados coerentes para arquiteturas paralelas atuais. Os Apêndices A e B apresentam os parâmetros que podem ser simulados pelo MINT.

Nossas simulações foram realizadas com 1, 2, 4, 8 e 16 processadores.

Os protocolos utilizados nas simulações são os de invalidação, atualização e híbrido. O protocolo híbrido é executado com os seguintes valores de *threshold*:

1, 2, 4 e 8. Nosso protocolo de invalidação utiliza o protocolo DASH com *release consistency* [29].

Nas figuras mostradas neste capítulo, o protocolo de invalidação apresenta taxas de falhas para as categorias *true*, *false*, *cold* e *eviction*. Esta categorização utiliza o algoritmo descrito em [17] e estendido por Bianchini [5]. O protocolo de atualização apresenta taxas de falha apenas para as categorias *cold* e *eviction*. O falso compartilhamento no protocolo de atualização é capturado através de uma outra categorização que classifica mensagens de atualização em *useful* ou *useless*. As mensagens de atualização têm a seguinte classificação:

- **True sharing updates.** O processador que recebe a atualização acessa a palavra atualizada antes que outra mensagem de atualização para a mesma palavra chegue ao processador;

- **False sharing updates.** O processador que recebe a atualização não acessa a palavra atualizada antes desta ser sobreescrita por outra atualização, mas acessa outra palavra no mesmo bloco de *cache*;

- **Proliferation updates.** O processador que recebe a atualização não acessa a palavra atualizada antes dela ser sobreescrita por outra atualização, e, também, não acessa outra palavra do mesmo bloco;

- **Replacement updates.** O processador que recebe a atualização não acessa a palavra atualizada até que o bloco é substituído de sua *cache*;

- **Termination updates.** Esta é uma mensagem de proliferação (*proliferation update*) que ocorre no término do programa.

Esta classificação utiliza o algoritmo descrito em [5]. É uma categorização simples, exceto pela classe de *false updates*. Sucessivas atualizações para a mesma palavra na *cache* são classificadas como proliferação, se o processador não estiver acessando outras palavras no mesmo bloco. Se o falso compartilhamento estiver realmente acontencendo, ou seja, o processador recebe sucessivas atualizações para o mesmo bloco, mas acessa outra palavra no bloco, estes *useless updates* são classificados como falsos.

O protocolo híbrido utiliza as mesmas classes do protocolo de atualização, porém inclui a classe *drop misses*, como descrito na Seção 2.7.

## 4.2 Aplicações e suas características

As aplicações utilizadas neste trabalho possuem somente paralelismo *-E*, somente paralelismo *-OU*, ou uma combinação das duas formas. Portanto, seus padrões de comportamento são variados. Estas são aplicações normalmente utilizadas para medir desempenho de sistemas paralelos de programação lógica.

### 4.2.1 Problema do caixeiro viajante (tsp)

A aplicação TSP (*Traveller Salesperson Problem*) possui paralelismo do tipo *-E*. É um problema clássico, onde é calculada a rota com menor distância entre vários pontos, sem que um ponto esteja presente duas vezes em uma mesma rota.

Esta aplicação encontra a solução aproximada do problema e é baseada numa solução escrita em Reform Prolog [4].

Nos experimentos utilizamos um grafo com 24 pontos, onde cada ponto representa uma cidade e as interconexões entre estes indicam as possíveis rotas.

### 4.2.2 Gerenciamento de redes da British Telecom (bt)

A aplicação BT possui paralelismo do tipo *-E*. Essa aplicação implementa um algoritmo de agrupamento (*clustering*) da British Telecom. Seu objetivo é agrupar os pontos cuja distância entre si seja menor que um determinado limite. Nos experimentos são utilizados 400 pontos.

### 4.2.3 Sistema de pergunta-resposta usando linguagem natural (chat)

A aplicação CHAT apresenta somente paralelismo do tipo *-OU*. Utilizamos a versão implementada por Pereira e Warren [54] que executa uma consulta para acesso à base de dados geográfica chat-80.

Esta aplicação foi utilizada inicialmente na avaliação dos sistemas Aurora [7] e Muse [1].

### 4.2.4 Sistema de alocação de recursos Pandora (pan2)

A aplicação PAN2 possui paralelismos do tipo *-E* e do tipo *-OU*. É uma aplicação real de controle de recursos aéreos. Por exemplo, o controle de porta-aviões associado a um conjunto de aeronaves.

Paralelismo do tipo  $-OU$  é explorado quando é feita a busca pelas várias possibilidades de alocação que possam existir. Paralelismo do tipo  $-E$  é explorado quando se executa várias restrições em paralelo.

O grau de paralelismo  $-E$  e  $-OU$  desta aplicação depende da consulta. Na consulta utilizada nos experimentos, o paralelismo  $-E$  é predominante. A consulta feita ao programa requer a alocação de 11 aeronaves, 36 membros da tripulação e 10 vôos.

A Tabela 4.1 apresenta as características de paralelismo e o *speedup* esperado pelas aplicações utilizadas neste estudo.

| Aplicação | Tipo de paralelismo | <i>Speedup</i> esperado em 16 processadores |

|-----------|---------------------|---------------------------------------------|

| BT        | $-E$                | entre 14 e 15                               |

| TSP       | $-E$                | aproximadamente 12                          |

| PAN2      | $-E$ e $-OU$        | entre 8 e 10                                |

| CHAT      | $-OU$               | aproximadamente 10                          |

Tabela 4.1: *Speedup* esperado para cada aplicação simulada

Estas aplicações foram escolhidas baseadas na variedade e quantidade de paralelismo. A terceira coluna da Tabela 4.1 indica o *speedup* esperado para cada aplicação baseado no *speedup* obtido quando rodando o simulador MINT configurado como uma máquina onde o custo de acesso à memória é desprezível.