### ON OPTIMIZATION OF HARDWARE-ASSISTED SECURITY

Leandro Santiago de Araújo

Tese de Doutorado apresentada ao Programa de Pós-graduação em Engenharia de Sistemas e Computação, COPPE, da Universidade Federal do Rio de Janeiro, como parte dos requisitos necessários à obtenção do título de Doutor em Engenharia de Sistemas e Computação.

Orientadores: Felipe Maia Galvão França Sandip Kundu Leandro Augusto Justen Marzulo

Rio de Janeiro Julho de 2019

#### ON OPTIMIZATION OF HARDWARE-ASSISTED SECURITY

Leandro Santiago de Araújo

TESE SUBMETIDA AO CORPO DOCENTE DO INSTITUTO ALBERTO LUIZ COIMBRA DE PÓS-GRADUAÇÃO E PESQUISA DE ENGENHARIA (COPPE) DA UNIVERSIDADE FEDERAL DO RIO DE JANEIRO COMO PARTE DOS REQUISITOS NECESSÁRIOS PARA A OBTENÇÃO DO GRAU DE DOUTOR EM CIÊNCIAS EM ENGENHARIA DE SISTEMAS E COMPUTAÇÃO.

Examinada por:

Prof. Felipe Maia Galvão França, Ph.D.

Prof. Claudio Luis de Amorim, Ph.D.

Prof. Valmir Carneiro Barbosa, Ph.D.

Prof. Maurício Lima Pilla, D.Sc.

Prof. Tiago Assumpção de Oliveira Alves, D.Sc.

RIO DE JANEIRO, RJ – BRASIL JULHO DE 2019 Araújo, Leandro Santiago de

On Optimization of Hardware-Assisted Security/Leandro Santiago de Araújo. – Rio de Janeiro: UFRJ/COPPE, 2019.

XVIII, 174 p.: il.; 29, 7cm.

Orientadores: Felipe Maia Galvão França

Sandip Kundu

Leandro Augusto Justen Marzulo

Tese (doutorado) – UFRJ/COPPE/Programa de Engenharia de Sistemas e Computação, 2019.

Referências Bibliográficas: p. 157 – 174.

PUF. 2. Taint Analysis. 3. DIFT. 4. Weightless Neural Network. 5. Bloom Filter. 6. Cuckoo Filter. 7. Quotient Filter. 8. Approximate Membership Query. 9. Multi-index Hashing. 10. Hardware Security. I. França, Felipe Maia Galvão *et al.* II. Universidade Federal do Rio de Janeiro, COPPE, Programa de Engenharia de Sistemas e Computação. III. Título.

Meu filho, guarda a sabedoria e a reflexão, não as percas de vista. Elas serão a vida de tua alma e um adorno para teu pescoço. Então caminharás com segurança, sem que o teu pé tropece. Se te deitares, não terás medo. Uma vez deitado, teu sono será doce. Não terás a recear nem terrores repentinos, nem a tempestade que cai sobre os ímpios. Porque o Senhor é tua segurança e preservará teu pé de toda cilada. (Bíblia, Provérbios 3:21-26)

> Dedico este trabalho à minha namorada Isis.

## Agradecimentos

Primeiramente, agradeço à minha namorada Isis, que me aguentou durante todo este tempo e que me apoiou em todas as minhas decisões, mesmo sabendo o quão difícil seria suportar a distância, e por ter me ajudado a manter o foco e me mostrar que sempre há uma luz no fim do túnel. Agradeço pelo seu companherismo, sua paciência e cumplicidade. Obrigado por tudo que tem feito por mim e por acreditar em mim. Te amo!

Agradeço à minha mãe, por me dá forças para seguir em frente e ter investido em mim, me ensinado o grande valor do estudo, educação e respeito.

Agradeço ao meus orientadores Felipe França e Leandro Marzulo que me acompanharam durante o mestrado e o doutorado. Obrigado pelos incetivos, confiança e por todos os ensinamentos. Esse trabalho só foi possível por vocês acreditarem na minha capacidade. Também agradeço por me disponibilizarem uma das bolsas de doutorado sanduíche vinculados ao projeto em parceria com a UMass. Sou muito grato por todas as oportunidades que vocês me deram.

Agradeço ao meu orientador Sandip Kundu, que começou a me orientar no período de doutorado sanduíche na UMass. Obrigado por me guiar e motivar a conhecer diversas áreas de pesquisas relacionadas à segurança. Grande parte desse trabalho é fruto das contribuições realizadas durante minha estadia na UMass. Também cito o professor Israel Koren, no qual contribuiu com o desenvolvimento do meu trabalho.

Agradeço aos amigos que fiz durante o doutorado sanduíche, dentre eles Nur, Felipe, Priscilla, Brenno, Camila, Maurício, Juliana, que me acolheram e me ajudaram durante todo o período fora do Brasil. Sou muito feliz por Deus ter colocado vocês na minha vida. Também agradeço aos colegas de laboratório da UMass, em especial ao Vinay Patil pelas parcerias em vários projetos e pelas conversas técnicas que foram de grande aprendizado para mim.

Agradeço aos amigos da UFRJ, dentre eles Brunno, Victor Cruz, Rui, entre outros. Obrigado pelas conversas descontraídas, por sempre estarem disponíveis em situações complicadas e pelas motivações.

À todos que contribuem em fazer Programa de Engenharia de Sistemas e Computação (PESC/COPPE/UFRJ) o melhor programa de pós-graduação do país. Agradeço aos professores e aos funcionários por serem atenciosos e prestativos contribuindo com a minha formação acadêmica.

Às agências de fomento CNPq, CAPES e COPPETEC, pelas bolsas que permitiram custear minhas despesas durante período de doutorado sanduíche na UMass, assim como o período de doutorado no Brasil. Resumo da Tese apresentada à COPPE/UFRJ como parte dos requisitos necessários para a obtenção do grau de Doutor em Ciências (D.Sc.)

#### SOBRE A OTIMIZAÇÃO DA SEGURANÇA ASSISTIDA POR HARDWARE

Leandro Santiago de Araújo

Julho/2019

Orientadores: Felipe Maia Galvão França Sandip Kundu Leandro Augusto Justen Marzulo

Programa: Engenharia de Sistemas e Computação

Physically Unclonable Functions (PUFs) surgiram como simples primitivas de segurança de hardware para implementar recursos de autenticação e geração de chaves criptográficas em dispositivos eletrônicos. Um Strong PUF ideal não é clonável e mapeia unicamente uma entrada de n-bits para uma saída de m-bits. Contudo, implementações reais de Strong PUFs possuem problemas de segurança. Esta tese propõe diversos modelos originais de Strong PUF, baseados na arquitetura de Redes Neurais sem Peso (RNP), resistentes contra ataques de construção de modelos por meio de algoritmos de aprendizado de máquina. A fabricação de grande volume de PUFs necessitam de técnicas de testes online para garantir a propriedade de exclusividade entre os PUFs fabricados. Uma solução de teste de PUF online baseado em Multi-Index Hashing (MIH) é otimizada através de estratégias de busca de similaridades para reduzir os recursos de memória. Dynamic Information Flow Tracking (DIFT) tem sido utilizado com sucesso para detectar acesso ilegal a informações confidenciais em tempo de execução. Nesta tese, um rastreador de fluxo implícito aninhado portátil é proposto para permitir que mecanismos baseados em fluxo explícito possam rastrear fluxos implícitos, inclusive em casos de aninhamento de laços profundo. Além do mais, uma nova regra de propagação é definida para mitigar a propagação incorreta dos dados afetados pela dependência de controle. Enfim, novos modelos de RNP baseados em estruturas de dados probabilísticas são propostas e analisadas com o objetivo de reduzir os requisitos de memória. Os novos modelos são robustos e são adequados como componentes para soluções de segurança assistidas por hardware.

Abstract of Thesis presented to COPPE/UFRJ as a partial fulfillment of the requirements for the degree of Doctor of Science (D.Sc.)

#### ON OPTIMIZATION OF HARDWARE-ASSISTED SECURITY

Leandro Santiago de Araújo

#### July/2019

Advisors: Felipe Maia Galvão França Sandip Kundu Leandro Augusto Justen Marzulo

Department: Systems Engineering and Computer Science

Physically Unclonable Functions (PUFs) have emerged as lightweight hardware security primitives to implement authentication and key generation features on electronic devices. An ideal Strong PUF cannot be cloned and maps an n-bit input to a unique m-bit output. However, real Strong PUF implementations suffer from security issues. This thesis proposes various novel Strong PUF designs, based on Weightless Neural Network (WNN) architecture, which are resistant against model building attacks through machine learning algorithms. Then, the proposed WNN PUFs are combined with a reliable entropy source to extend the reliability property to the final Strong PUF. High volume manufacturing of PUFs requires online testing techniques to ensure the desired uniqueness property among the manufactured PUFs. An online testing PUF solution based on Multi-Index Hashing (MIH) is optimized by similarity search strategies to reduce the memory resources. Dynamic Information Flow Tracking (DIFT) has been successfully utilized to detect illegal access to sensitive information at runtime. Nonetheless, recent evasion attacks explore implicit flows based on control dependencies that are not detectable by most of DIFT implementations, which only track data dependency propagation. In this thesis, a portable nested implicit flow tracking is proposed to enable explicitflow based DIFT mechanisms track implicit flows, including deeply-nested branch scenarios. In addition, a new propagation rule is defined to mitigate the incorrect propagation of data under control dependencies. Finally, new WNN models based on probabilistic data structures are proposed and analyzed in order to reduce the memory requirements. The new models are robust and are suitable as components for hardware-assisted security solutions.

## Contents

| $\operatorname{Li}$ | st of | Figures                                                                                                                                        | xiii |

|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|------|

| $\mathbf{Li}$       | st of | Tables x                                                                                                                                       | viii |

| 1                   | Intr  | roduction                                                                                                                                      | 1    |

|                     | 1.1   | Contribution                                                                                                                                   | 4    |

|                     | 1.2   | Thesis outline                                                                                                                                 | 5    |

| 2                   | Bac   | ckground                                                                                                                                       | 7    |

|                     | 2.1   | PUF                                                                                                                                            | 7    |

|                     |       | 2.1.1 Classification of PUFs                                                                                                                   | 7    |

|                     |       | 2.1.1.1 Weak PUF                                                                                                                               | 7    |

|                     |       | $2.1.1.2  \text{Strong PUF} \dots \dots$ | 8    |

|                     |       | 2.1.2 Ideal Properties of PUFs                                                                                                                 | 9    |

|                     |       | $2.1.2.1  \text{Security}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                    | 10   |

|                     |       | $2.1.2.2  \text{Uniqueness}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                  | 10   |

|                     |       | 2.1.2.3 Reliability                                                                                                                            | 10   |

|                     |       | 2.1.3 Weak PUF Realibility                                                                                                                     | 10   |

|                     | 2.2   | WiSARD                                                                                                                                         | 11   |

|                     | 2.3   | Dynamic Information Flow Tracking                                                                                                              | 13   |

|                     |       | 2.3.1 Under-tainting and over-tainting problems                                                                                                | 13   |

|                     |       | 2.3.2 DIFT Designs                                                                                                                             | 14   |

|                     |       | 2.3.3 Related Works                                                                                                                            | 15   |

|                     | 2.4   | Error Correction Codes                                                                                                                         | 16   |

|                     | 2.5   | Multi-Index Hashing                                                                                                                            | 18   |

|                     |       |                                                                                                                                                |      |

| 3                   | Rel   | iable Strong PUFs based on Weightless Neural Network                                                                                           | 19   |

|                     | 3.1   | Strong PUFs based on Weightless Neural Network                                                                                                 | 20   |

|                     |       | 3.1.1 WiSARD PUF                                                                                                                               | 20   |

|                     |       | 3.1.2 Extensions to WiSARD PUF architecture                                                                                                    | 21   |

|                     |       | 3.1.2.1 Fuzzy logic based address generation                                                                                                   | 22   |

|                     |       | 3.1.2.2 Concatenated codes based response generation                                                                                           | 24   |

|          | 3.2                  | WNN PUF - Experimental Setup and Results                                                              | 24              |

|----------|----------------------|-------------------------------------------------------------------------------------------------------|-----------------|

|          |                      | 3.2.1 Experimental Setup                                                                              | 26              |

|          |                      | 3.2.2 Uniqueness $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                | 26              |

|          |                      | $3.2.3  \text{Reliability}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 28              |

|          |                      | 3.2.4 Machine Learning Attack Resistance                                                              | 30              |

|          |                      | 3.2.5 Hardware Analysis                                                                               | 31              |

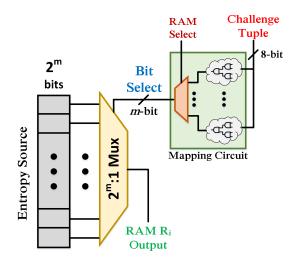

|          | 3.3                  | Reliable Strong PUF Implementation                                                                    | 33              |

|          |                      | 3.3.1 Reliable Weak PUF Entropy Source                                                                | 33              |

|          |                      | 3.3.2 Complete Strong PUF architecture                                                                | 34              |

|          | 3.4                  | Reliable Strong PUF - Experimental Setup and Results                                                  | 34              |

|          |                      | 3.4.1 Experimental Setup                                                                              | 35              |

|          |                      | 3.4.2 Uniqueness                                                                                      | 35              |

|          |                      | 3.4.3 Machine Learning Resistance                                                                     | 36              |

|          | 3.5                  | Concluding Remarks                                                                                    | 40              |

| 4        | FÆ                   | signation Change DIJE for Ilainneas                                                                   | 40              |

| 4        | <b>E</b> .III<br>4.1 | cient Testing Strong PUF for Uniqueness                                                               | <b>46</b><br>47 |

|          | 4.1                  | MIH for Testing Strong PUFs4.1.1Metrics for Uniqueness                                                | $\frac{47}{47}$ |

|          |                      | 4.1.1       Metrics for Oniqueness         4.1.2       Problem Statement                              | $\frac{47}{47}$ |

|          |                      | 4.1.2 <u>Froblem Statement</u>                                                                        | 47<br>48        |

|          |                      | 4.1.5       Wutt-index frashing for resting r or         4.1.4       Uniqueness Test Procedure        | 48<br>48        |

|          | 4.2                  | Analyzing MIH Implementations                                                                         | 40<br>49        |

|          | 4.2                  | 4.2.1       Original MIH Implementation                                                               | 49              |

|          |                      | 4.2.2 MIH Implementation with Global Index                                                            | 49<br>50        |

|          | 4.3                  | Strategies for Memory Reduction                                                                       | 51              |

|          | 1.0                  | 4.3.1 Distance Free Computation Strategy                                                              | 51              |

|          |                      | 4.3.2 Hamming Weight Strategy                                                                         | 53              |

|          | 4.4                  | Experiments and Results                                                                               | 54              |

|          |                      | 4.4.1 Experimental Setup                                                                              | 54              |

|          |                      | 4.4.2 Original MIH vs MIH with Global Index                                                           | 54              |

|          |                      | 4.4.3 Strategy Thresholds Evaluation                                                                  | 56              |

|          |                      | 4.4.4 MIH Versions Analysis                                                                           | 58              |

|          | 4.5                  | Concluding Remarks                                                                                    | 61              |

|          |                      |                                                                                                       |                 |

| <b>5</b> | Dee                  | ply-Nested Implicit Information Flow Tracking                                                         | 62              |

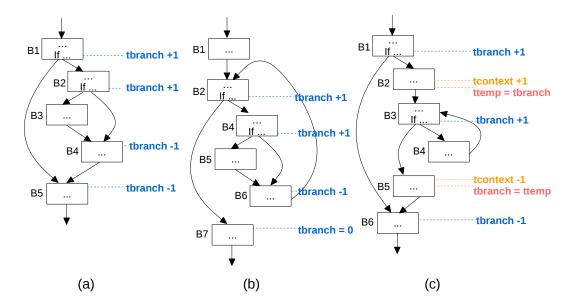

|          | 5.1                  | Nested Implicit Flow Tracking Implementation                                                          | 63              |

|          |                      | 5.1.1 Taint Propagation to No-operand Instructions                                                    | 63              |

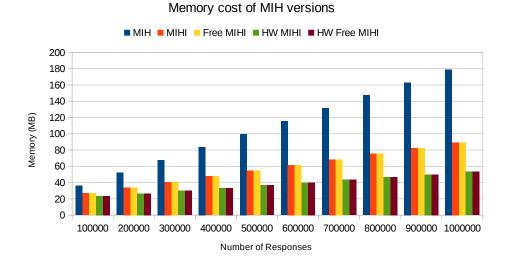

|          |                      | 5.1.2 Branch and Context Counter Scheme                                                               | 64              |

|          |                      | 5.1.3 Taint Instructions                                                                              | 66              |

|          | 5.2                  | Nested Implicit Flow Tracking Formal Verification                                                     | 69              |

|                |     | 5.2.1 UPPAAL Model Checker                                                                                                                       | 69  |

|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                |     | 5.2.2 Modelling Nested Implicit Flow Tracking                                                                                                    | 70  |

|                |     | 5.2.3 Correctness Verification                                                                                                                   | 71  |

|                | 5.3 | Experiment Results                                                                                                                               | 74  |

|                |     | 5.3.1 Experimental Setup                                                                                                                         | 74  |

|                |     | 5.3.2 Performance Overhead                                                                                                                       | 75  |

|                |     | 5.3.3 Code Size                                                                                                                                  | 76  |

|                |     | 5.3.4 Tainting Capabilities                                                                                                                      | 76  |

|                | 5.4 | Concluding Remarks                                                                                                                               | 81  |

| _              |     |                                                                                                                                                  |     |

| 6              |     | mory Efficient WiSARD using Approximate Membership                                                                                               |     |

|                | Que |                                                                                                                                                  | 83  |

|                | 6.1 | Approximate Membership Query Structures                                                                                                          |     |

|                |     | 6.1.1 Bloom Filter                                                                                                                               |     |

|                |     | $6.1.2  \text{Cuckoo Hashing} \dots \dots$ |     |

|                |     | 6.1.3 Cuckoo Filter                                                                                                                              |     |

|                |     | 6.1.4 Quotient Filter                                                                                                                            |     |

|                | 6.2 | WiSARD based on AMQ Filters                                                                                                                      |     |

|                |     | 6.2.1 Bloom WiSARD - WiSARD based on Bloom Filters                                                                                               |     |

|                |     | 6.2.2 Cuckoo WiSARD - WiSARD based on Cuckoo Filters                                                                                             |     |

|                |     | 6.2.3 Quotient WiSARD - WiSARD based on Quotient Filters                                                                                         |     |

|                | 6.3 | Experiments and Results                                                                                                                          |     |

|                |     | 6.3.1 Dataset                                                                                                                                    |     |

|                |     | 6.3.2 Experimental Setup                                                                                                                         |     |

|                |     | 6.3.3 Accuracy, Performance and Memory Consumption Results                                                                                       |     |

|                |     | 6.3.4 Bloom WiSARD: False Positive Rate vs. Accuracy vs. Mem-                                                                                    |     |

|                |     | ory Analysis                                                                                                                                     |     |

|                |     | 6.3.5 AMQ WiSARD: Accuracy vs. Memory Analysis                                                                                                   |     |

|                | 6.4 | Concluding Remarks                                                                                                                               | 102 |

| $\overline{7}$ | Cor | nclusion                                                                                                                                         | 103 |

|                |     |                                                                                                                                                  | 100 |

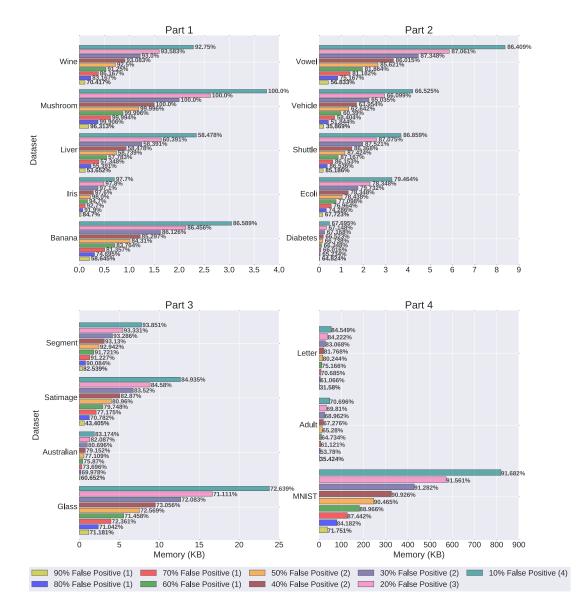

| Α              | Har | dware Similarity Search with Multi-Index Hashing                                                                                                 | 106 |

|                | A.1 | K-Nearest Neighbors Search Algorithm                                                                                                             | 107 |

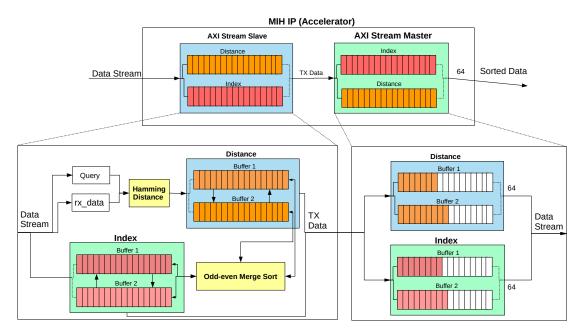

|                | A.2 | The Accelerator Architecture                                                                                                                     | 108 |

|                |     | A.2.1 Top View                                                                                                                                   | 108 |

|                |     | A.2.2 Accelerator Design                                                                                                                         | 109 |

|                |     | A.2.3 Specialized Components                                                                                                                     |     |

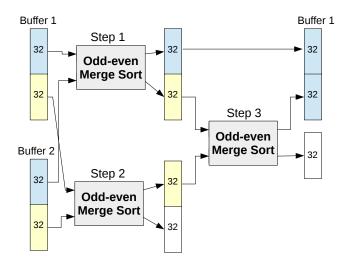

|                |     | A.2.4 Buffer Merge Strategy                                                                                                                      | 113 |

|                | A.3 | Experiments                                                                                                                                      | 113 |

|                     | A.3.1 Data sets                                         | . 114 |

|---------------------|---------------------------------------------------------|-------|

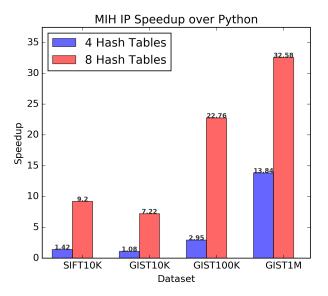

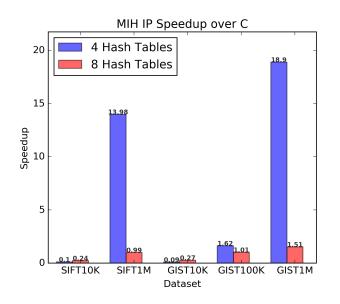

|                     | A.3.2 Performance                                       | . 114 |

|                     | A.3.3 Utilization Cost                                  | . 117 |

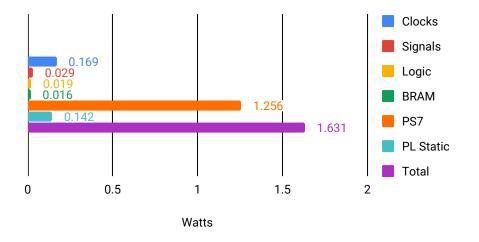

|                     | A.3.4 Power                                             | . 117 |

|                     | A.4 Concluding Remarks                                  | . 118 |

|                     |                                                         |       |

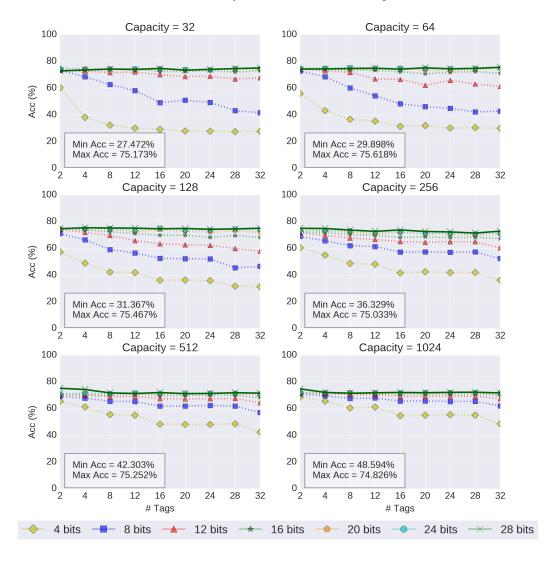

| Β                   | Complete Accuracy Results of Cuckoo and Quotient WiSARD | 120   |

|                     | B.1 Adult                                               | . 120 |

|                     | B.2 Australian                                          | . 120 |

|                     | B.3 Banana                                              | . 120 |

|                     | B.4 Diabetes                                            | . 122 |

|                     | B.5 Ecoli                                               | . 122 |

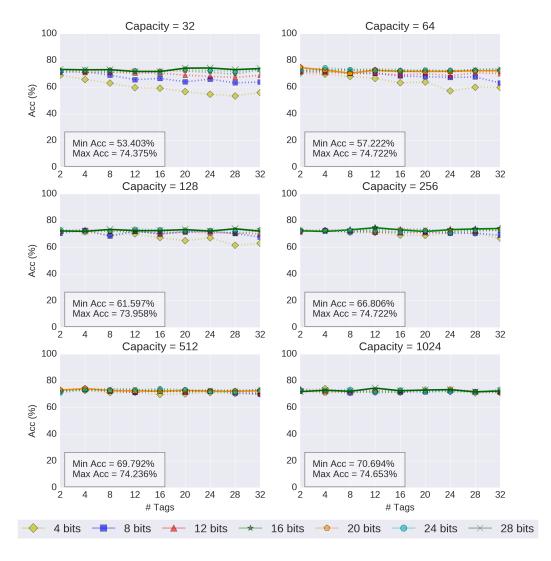

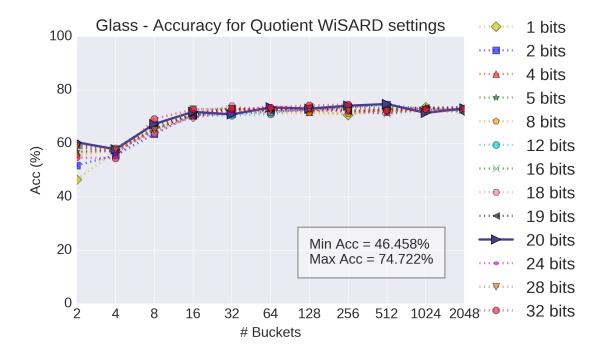

|                     | B.6 Glass                                               | . 122 |

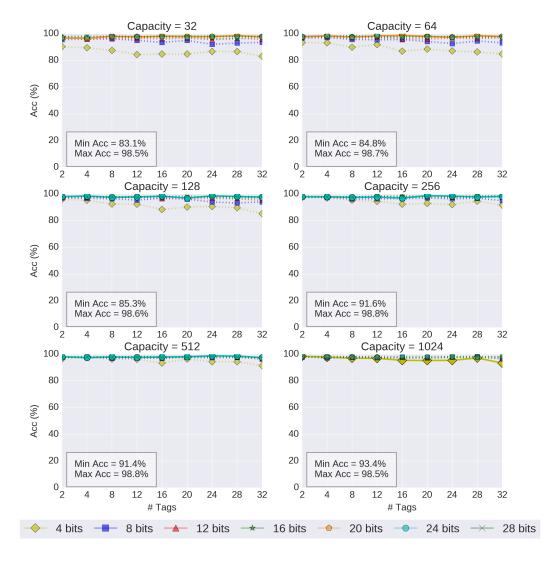

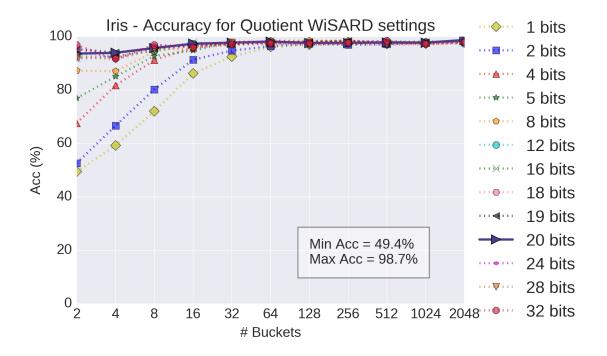

|                     | B.7 Iris                                                | . 122 |

|                     | B.8 Letter                                              | . 124 |

|                     | B.9 Liver                                               | . 124 |

|                     | B.10 MNIST                                              | . 124 |

|                     | B.11 Mushroom                                           | . 124 |

|                     | B.12 Satimage                                           | . 126 |

|                     | B.13 Segment                                            | . 126 |

|                     | B.14 Shuttle                                            | . 126 |

|                     | B.15 Vehicle                                            | . 126 |

|                     | B.16 Vowel                                              | . 128 |

|                     | B.17 Wine                                               |       |

|                     |                                                         |       |

| $\mathbf{C}$        | List of Publications                                    | 155   |

|                     | C.1 Journal Articles                                    | . 155 |

|                     | C.2 In Conference Proceedings                           | . 155 |

|                     |                                                         |       |

| $\operatorname{Bi}$ | bliography                                              | 157   |

# List of Figures

| 1.1 Category of HW-assisted security technologies $\blacksquare$ . |                                           | 3  |

|--------------------------------------------------------------------|-------------------------------------------|----|

| 2.1 Example of six transistors at SRAM cell                        |                                           | 8  |

| 2.2 Example of training in WiSARD                                  | 1                                         | 12 |

| 2.3 Example of testing operation in one WiSARD disc                | riminator 1                               | 12 |

| 2.4 Example of testing operation to WiSARD select p                | redicted class 1                          | 13 |

| 2.5 The three DIFT designs.                                        | 1                                         | 14 |

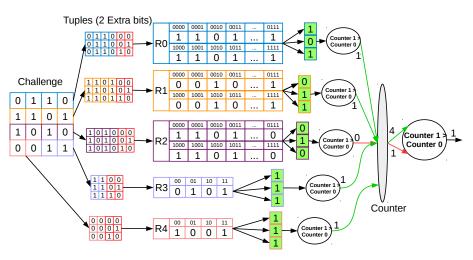

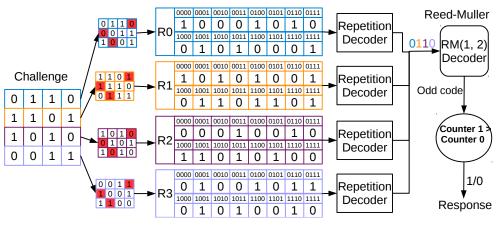

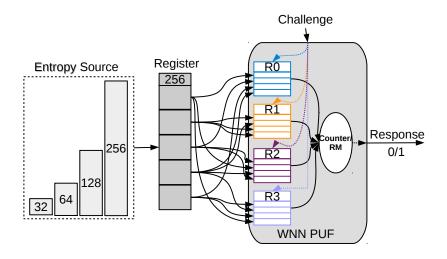

| 3.1 Example of WiSARD PUF architecture <b>2</b>                    | <b>0</b>                                  | 20 |

| 3.2 Example of WiSARD PUF with fixed tuples amon                   |                                           | 20 |

|                                                                    |                                           | 11 |

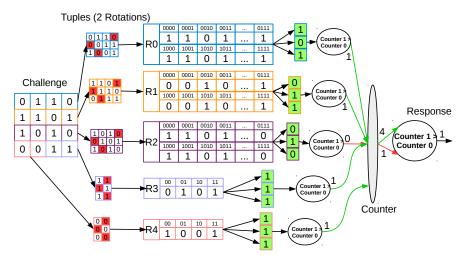

| 3.3 Example of WiSARD PUF architecture with exte                   |                                           |    |

| generation <b>2</b>                                                |                                           | 22 |

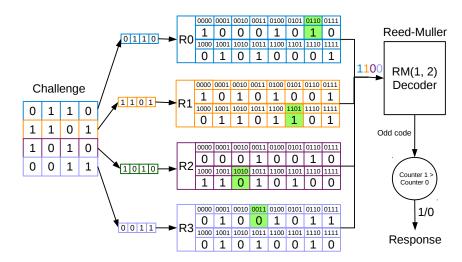

| 3.4 Example of RM-WiSARD PUF architecture $2$ .                    |                                           | 23 |

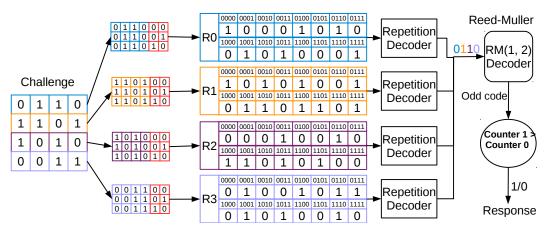

| 3.5 Example of RM-WiSARD PUF architecture with                     | concatenated code                         |    |

| 2                                                                  | 2                                         | 25 |

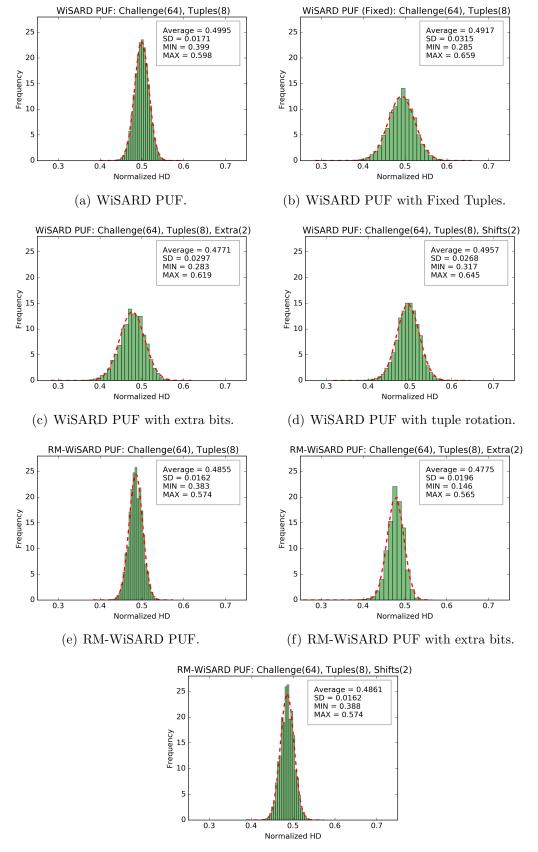

| 3.6 Inter-class Hamming Distance (uniqueness) distribution         | ution for WiSARD                          |    |

| PUFs                                                               | 2                                         | 27 |

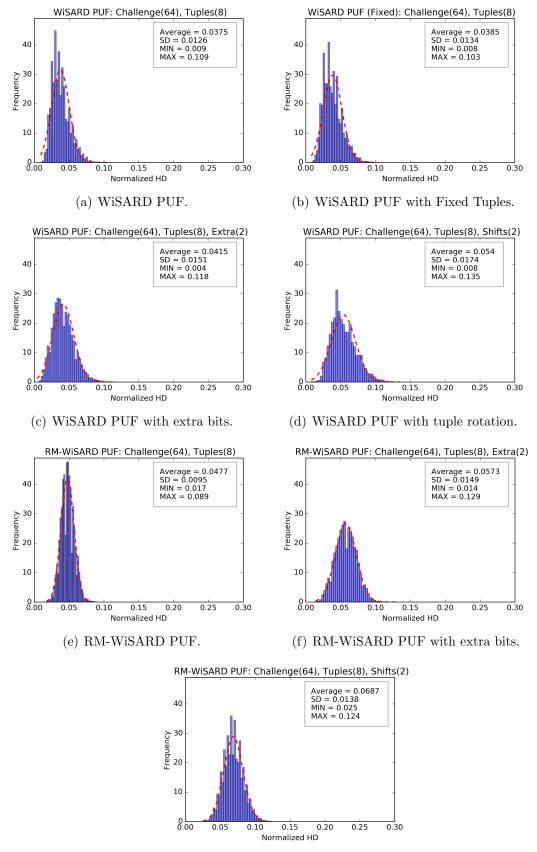

| 3.7 Intra-class Hamming Distance (reliability) distribution        | $1 tion. \dots \dots \dots \dots \dots 2$ | 29 |

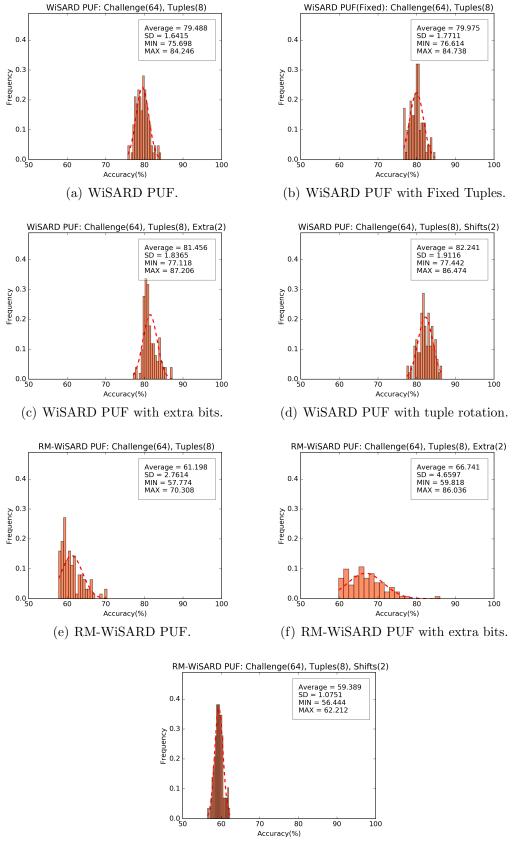

| 3.8 Gradient Boosting accuracy distribution                        | 3                                         | 32 |

| 3.9 Reliable Strong PUF implementation $[3]$                       | 3                                         | 34 |

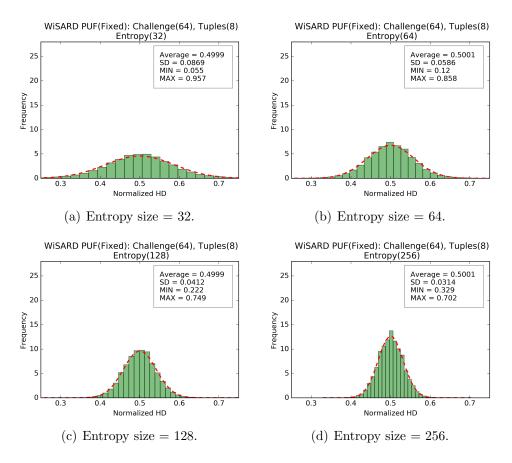

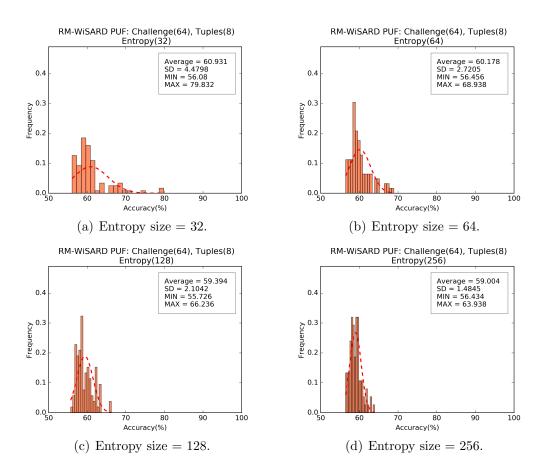

| 3.10 Uniqueness distribution for WiSARD PUF with Fiz               | xed Tuples varying                        |    |

| Entropy Source sizes                                               | 3                                         | 36 |

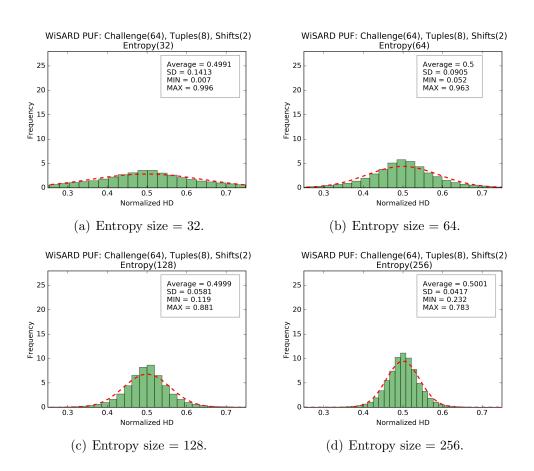

| 3.11 Uniqueness distribution for WiSARD PUF with tu                | uple rotation vary-                       |    |

| ing Entropy Source sizes                                           | 3                                         | 37 |

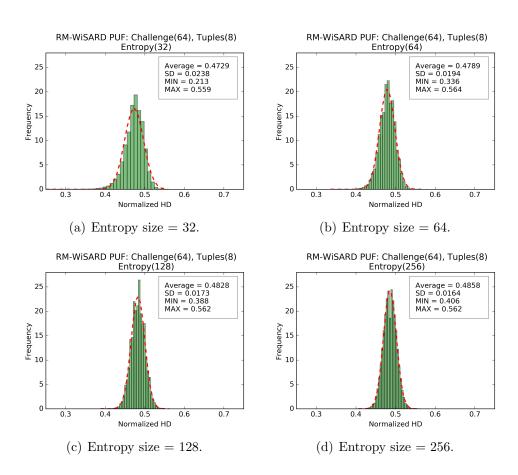

| 3.12 Uniqueness distribution for RM-WiSARD PUF                     | varying Entropy                           |    |

| Source sizes                                                       | 3                                         | 38 |

| 3.13 Uniqueness distribution for RM-WiSARD PUF w                   | vith tuple rotation                       |    |

| varying Entropy Source sizes                                       | 3                                         | 39 |

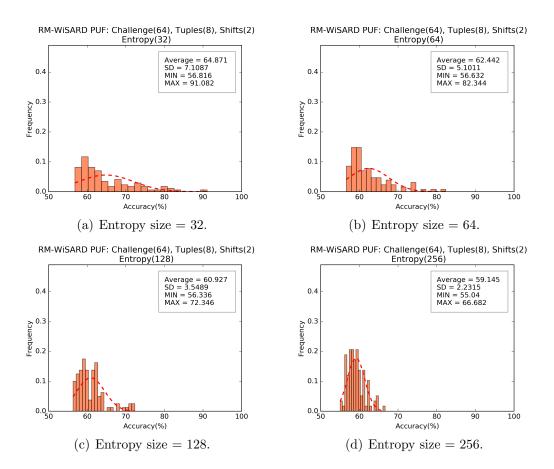

| 3.14 Gradient Boosting machine learning accuracy dist              | ributions for RM-                         |    |

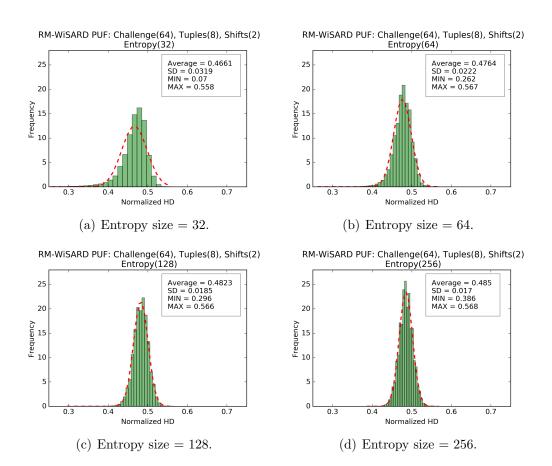

| WiSARD PUF.                                                        | 4                                         | 11 |

|   | 0 1 -      |                                                                         |    |

|---|------------|-------------------------------------------------------------------------|----|

|   | 3.15       | Gradient Boosting machine learning accuracy distributions for RM-       |    |

|   |            | WiSARD PUF with tuple rotation.                                         | 42 |

|   | 3.16       | Combinational logic-based implementation of Strong PUF 3                | 44 |

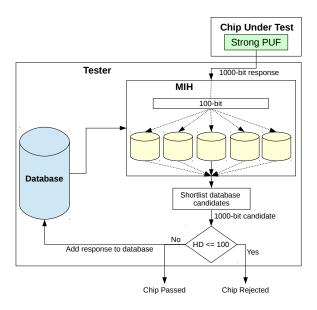

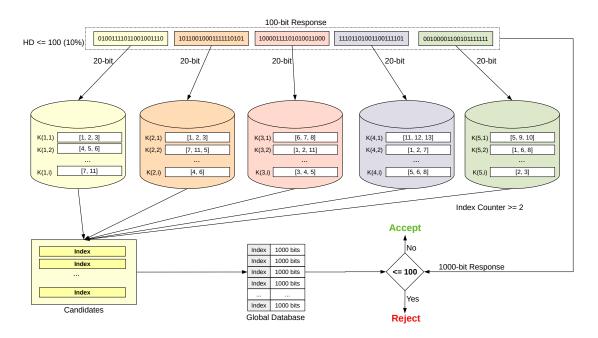

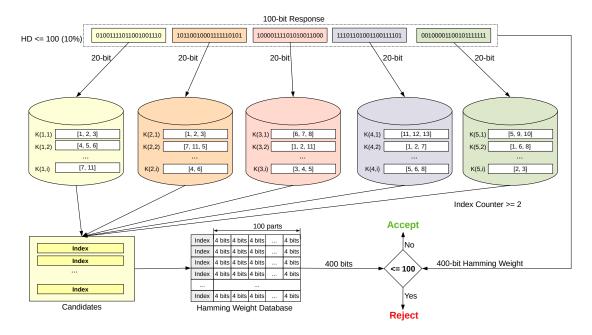

|   | 4.1        | Example of testing Strong PUF.                                          | 49 |

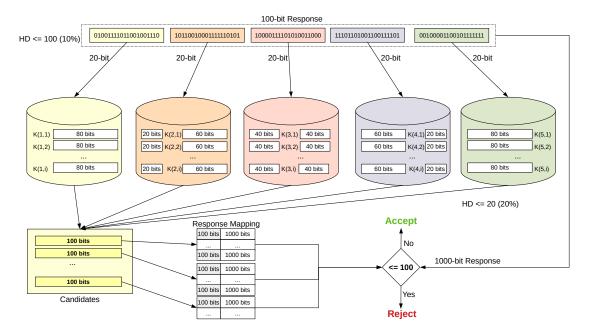

|   | 4.2        | Example of testing Strong PUF using original MIH.                       | 50 |

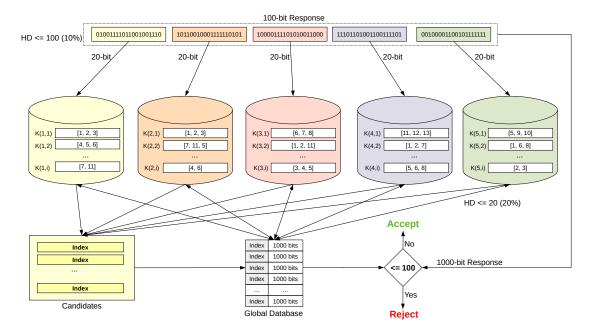

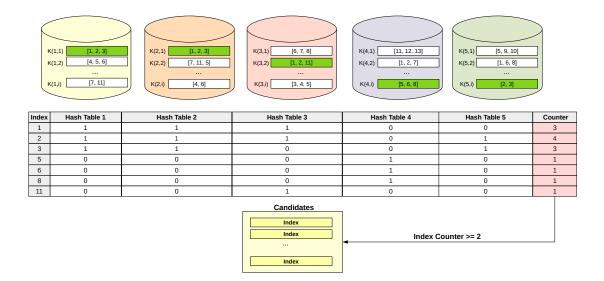

|   | 4.3        | Example of testing Strong PUF using MIH with global index.              | 51 |

|   | 4.4        | Example of distance free computation strategy.                          | 52 |

|   | 4.5        | Example of MIH using distance free computation strategy.                | 52 |

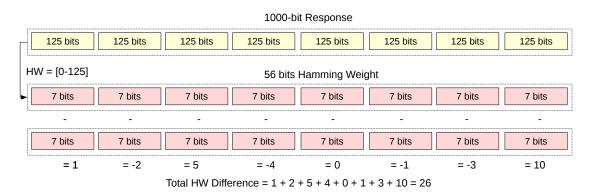

|   | 4.6        | Example of hamming weight strategy.                                     | 53 |

|   | 4.7        | Example of MIH using hamming weight strategy.                           | 54 |

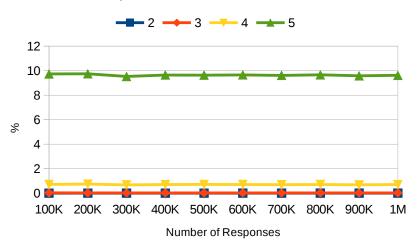

|   | 4.8        | Faulty chip rate for different configurations using distance free com-  |    |

|   |            | putation strategy.                                                      | 56 |

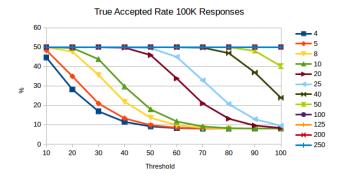

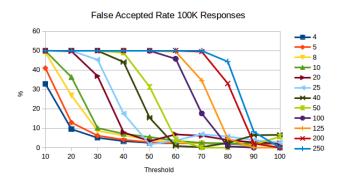

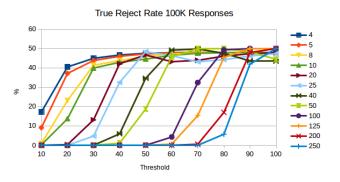

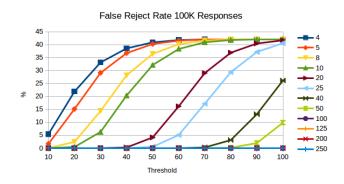

|   | 4.9        | Experiment of true/false rates vs HW difference threshold               | 57 |

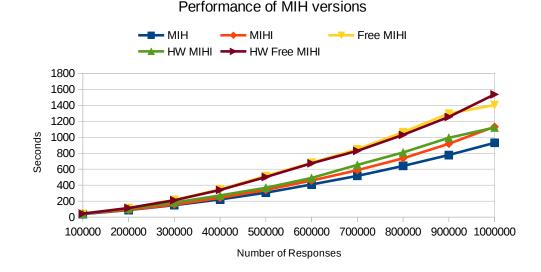

|   | 4.10       | Performance of all MIH versions.                                        | 60 |

|   | 4.11       | Memory consumption of all MIH versions.                                 | 60 |

| 1 | 5.1        | Example of code with implicit propagation flow.                         | 64 |

|   | 5.2        | Examples of taint register operations.                                  | 65 |

|   | 5.2<br>5.3 | Examples of taint instructions.                                         | 67 |

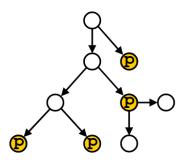

|   | 5.3        | UPPAAL model for NIFT.                                                  | 70 |

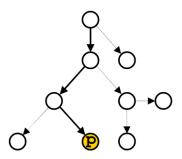

|   | 5.5        | Example of reachability property on UPPAAL.                             | 71 |

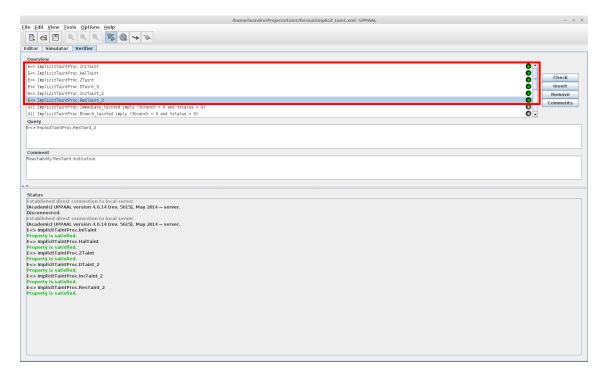

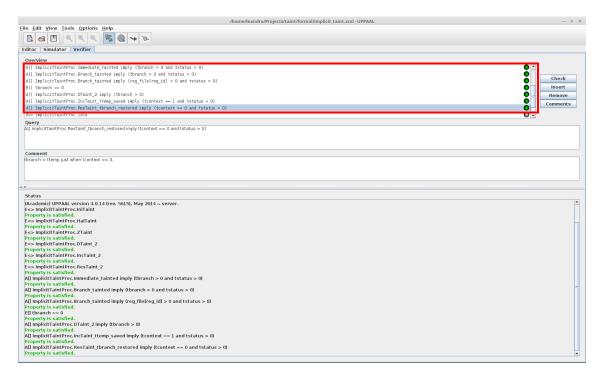

|   | 5.6        | Reachability property of NIFT on UPPAAL verifier.                       | 72 |

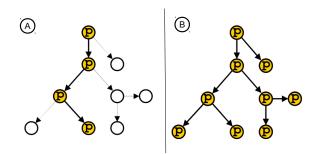

|   | 5.7        | Example of safety property on UPPAAL.                                   | 72 |

|   | 5.8        | Safety property of NIFT on UPPAAL verifier.                             | 73 |

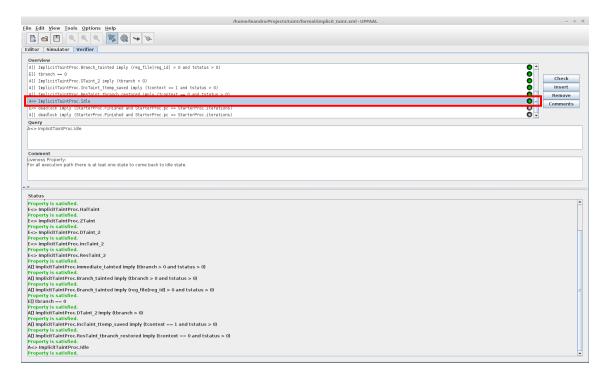

|   | 5.9        | Example of liveness property on UPPAAL.                                 | 73 |

|   |            | Liveness property of NIFT on UPPAAL verifier.                           | 74 |

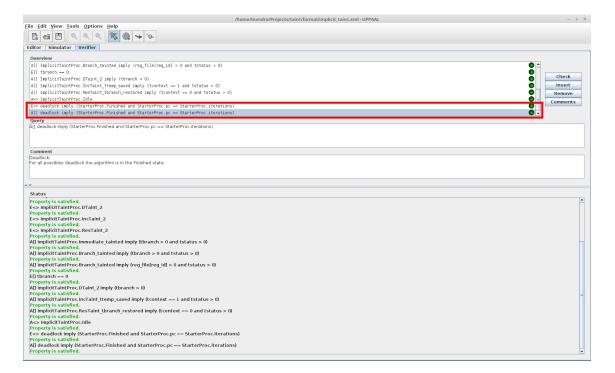

|   | 5.11       | Deadlock property of NIFT on UPPAAL verifier.                           | 75 |

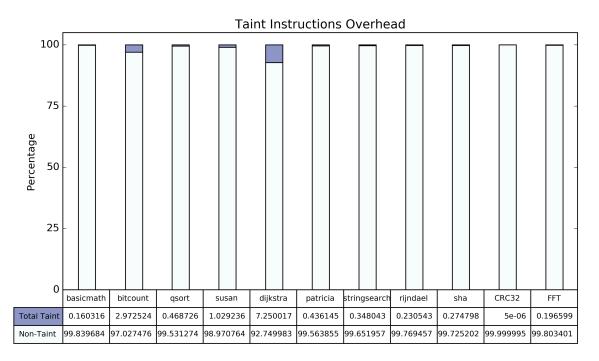

|   | 5.12       | Performance overhead of the NIFT(%).                                    | 76 |

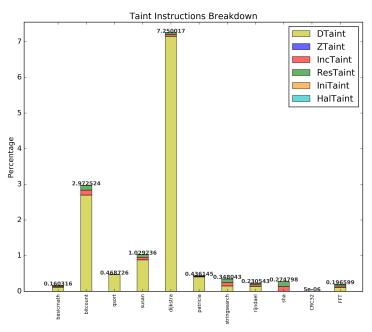

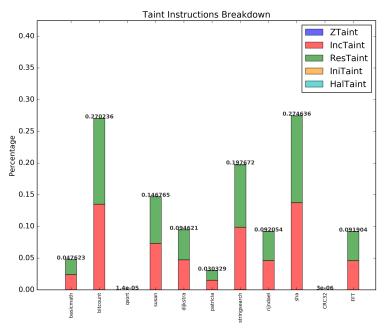

|   | 5.13       | The overhead of the individual taint instructions.                      | 77 |

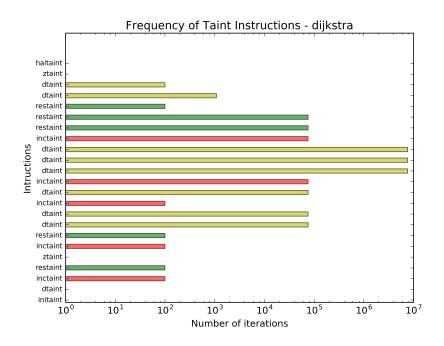

|   | 5.14       | Number of iterations for the <b>dtaint</b> instructions.                | 78 |

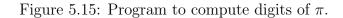

|   | 5.15       | Program to compute digits of $\pi$ .                                    | 78 |

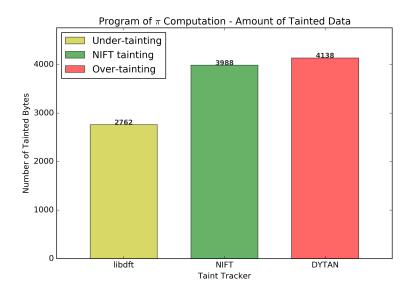

|   | 5.16       | Comparison of tainted bytes in $\pi$ computation program.               | 79 |

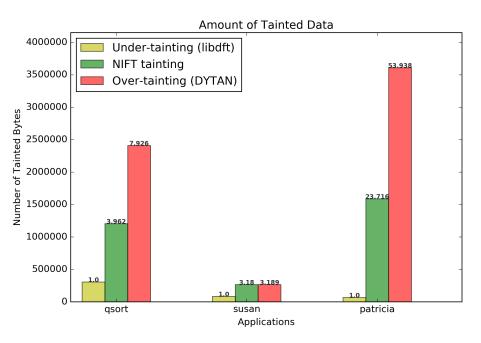

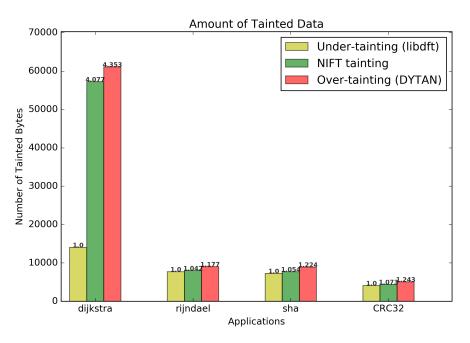

|   | 5.17       | Comparison of tainted bytes for mibench applications                    | 80 |

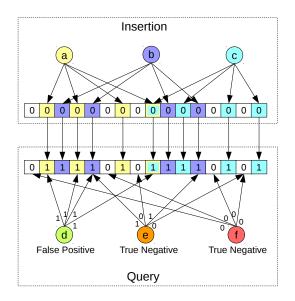

|   | 6.1        | Bloom filter operations example with 16-bit array and 4 hash functions. | 84 |

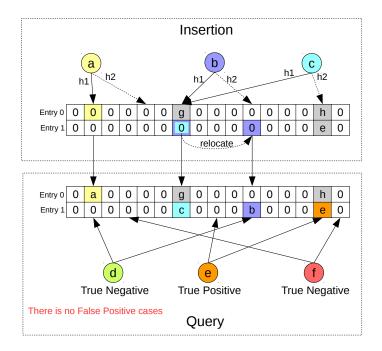

|   | 6.2        | Example of Cuckoo Hash Table operations with 16 buckets with 2          |    |

|   |            | entries.                                                                | 86 |

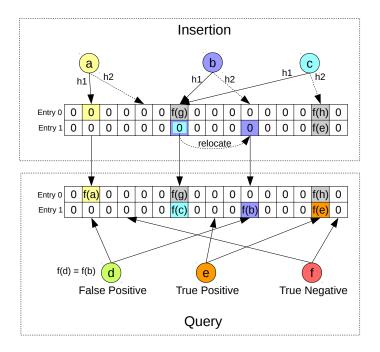

|   | 6.3        | Example of Cuckoo filter operations with 16 buckets with 2 entries.     | 87 |

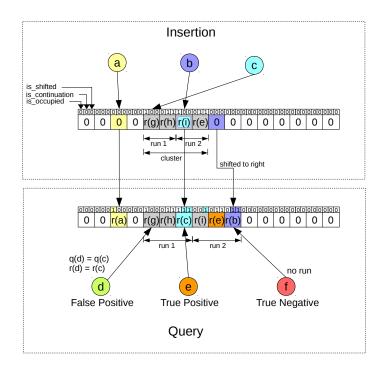

|   | 6.4        | Example of Quotient filter operations with 16 buckets.                  | 89 |

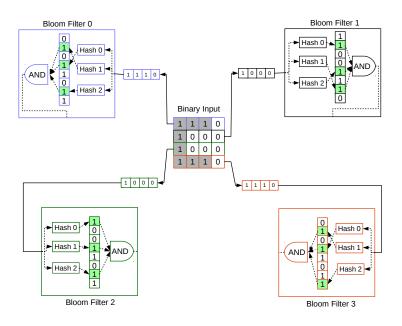

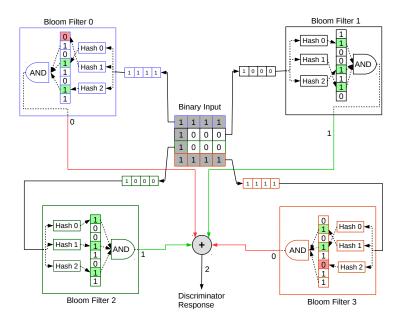

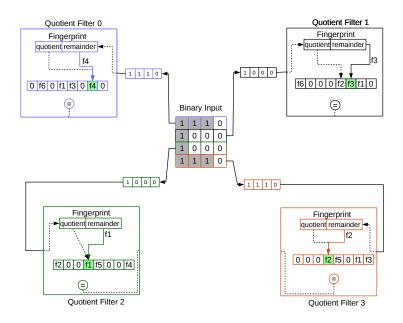

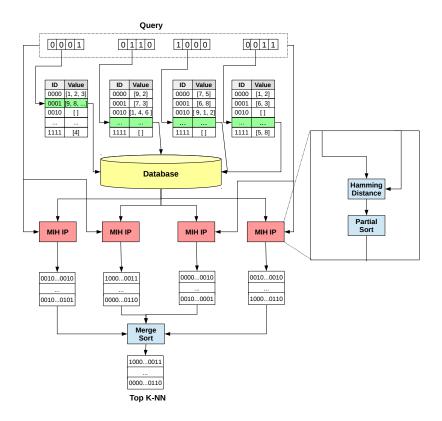

|   | 6.5  | Example of training in Bloom WiSARD with 16-bit input, 4-bit tuples  |     |

|---|------|----------------------------------------------------------------------|-----|

|   |      | and 4 Bloom filters                                                  | )1  |

|   | 6.6  | Example of classification in Bloom WiSARD with 16-bit input, 4-bit   |     |

|   |      | tuples and 4 Bloom filters                                           | )1  |

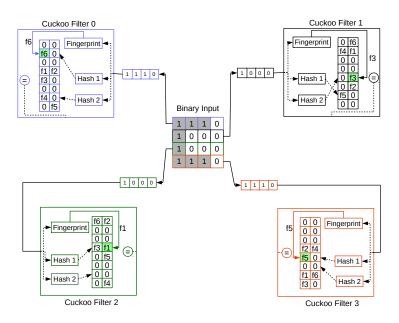

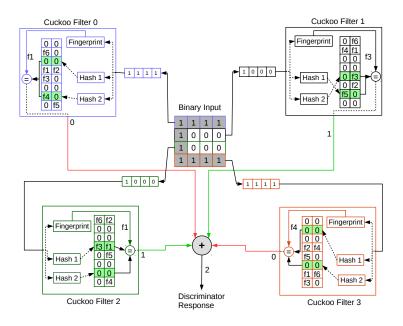

|   | 6.7  | Example of training in Cuckoo WiSARD with 16-bit input, 4-bit tu-    |     |

|   |      | ples and 4 Cuckoo filters                                            | 92  |

|   | 6.8  | Example of classification in Cuckoo WiSARD with 16-bit input, 4-bit  |     |

|   |      | tuples and 4 Cuckoo filters                                          | )3  |

|   | 6.9  | Example of training in Quotient WiSARD with 16-bit input, 4-bit      |     |

|   |      | tuples and 4 Quotient filters                                        | 94  |

|   | 6.10 | Example of classification in Quotient WiSARD with 16-bit input, 4-   |     |

|   |      | bit tuples and 4 Quotient filters                                    | 94  |

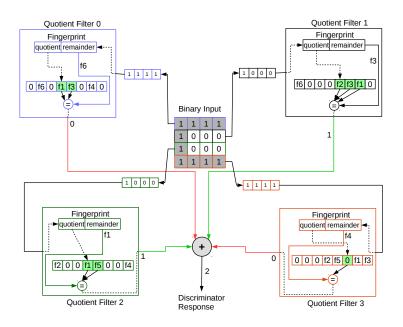

|   | 6.11 | Accuracy and memory consumption results when varying the false       |     |

|   |      | positive rate of Bloom WiSARD                                        | )() |

|   | A 1  |                                                                      | _   |

| _ | A.1  | K-nearest neighbor search with Multi-Index Hashing (MIH) hardware    |     |

|   |      | accelerator (MIH Intellectual Property - IP).                        |     |

|   | A.2  | Overview of the MIH Accelerator                                      |     |

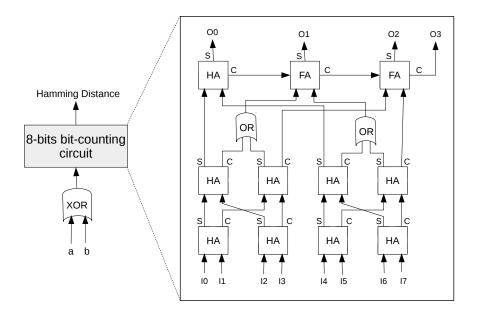

|   | A.3  | 8-bits Hamming Distance counting component, as proposed in [4] 11    | . 1 |

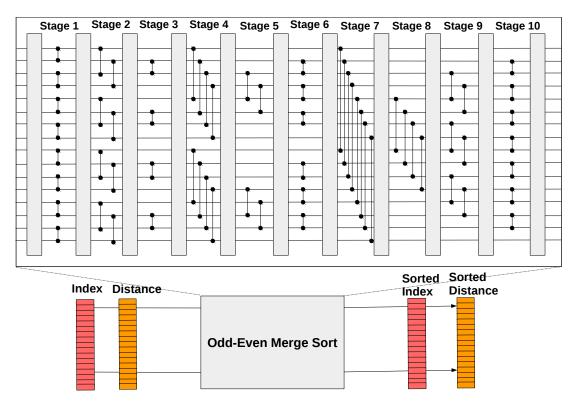

| _ | A.4  | Odd-even merge sort component, exemplifying the sort network with    |     |

|   |      | 16-bit inputs, 16-bit outputs and 10 pipeline stages.                |     |

|   | A.5  | Buffering merge process of buffer 1 and 2                            |     |

|   | A.6  | Speedup of MIH IP compared to Python version                         |     |

|   | A.7  | Speedup of MIH IP compared to C version                              |     |

|   | A.8  | Vivado 2018.1 Power consumption report                               | .8  |

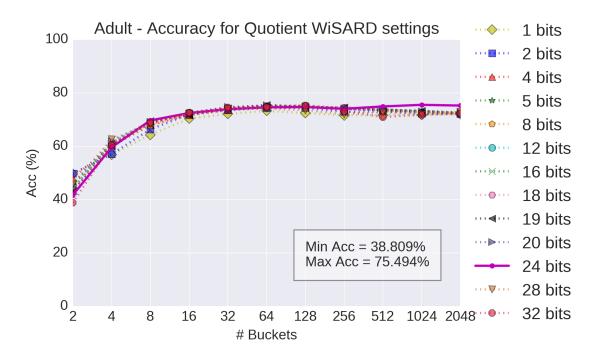

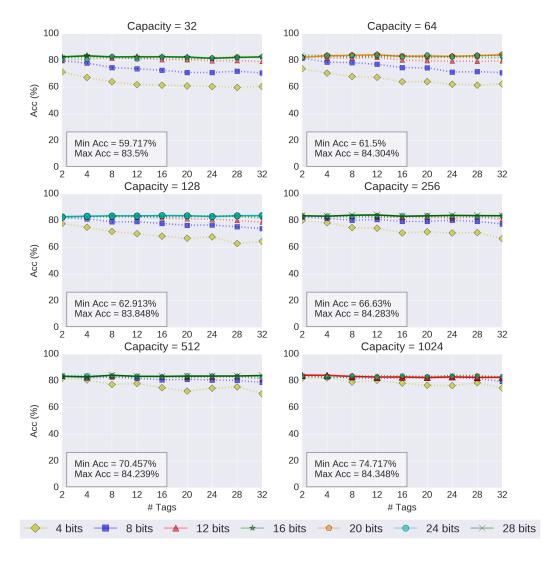

|   | B.1  | Accuracy results of Adult dataset when varying capacity, number of   | ٦   |

|   |      | tags (entries) per bucket and tag bits of Cuckoo WiSARD              | 21  |

|   | B.2  | Accuracy results of Adult dataset when varying capacity (quotient    | ٦   |

|   |      | bits) and tag bits (remainder bits) of Quotient WiSARD               | 22  |

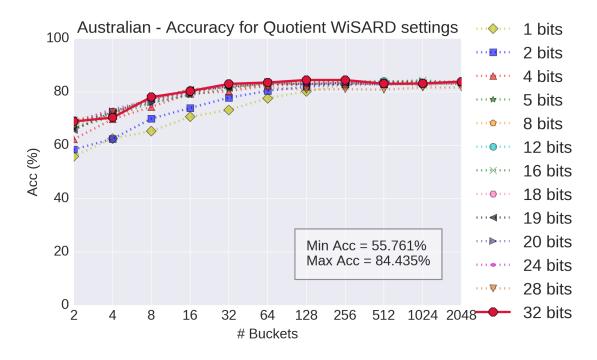

|   | B.3  | Accuracy results of Australian dataset when varying capacity, number | ٦   |

| Г |      | of tags (entries) per bucket and tag bits of Cuckoo WiSARD 12        | 23  |

|   | B.4  | Accuracy results of Australian dataset when varying capacity (quo-   | ٦   |

| Г |      | tient bits) and tag bits (remainder bits) of Quotient WiSARD 12      | 24  |

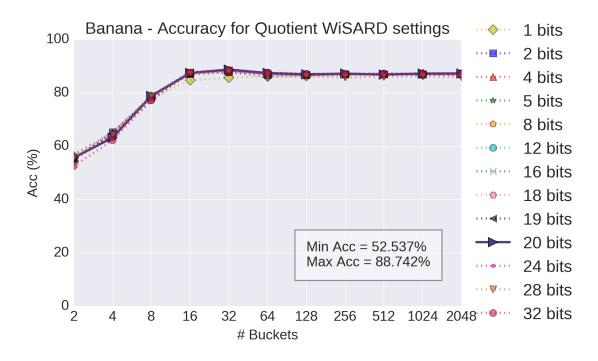

|   | B.5  | Accuracy results of Banana dataset when varying capacity, number     |     |

|   |      | of tags (entries) per bucket and tag bits of Cuckoo WiSARD 12        | 25  |

|   | B.6  | Accuracy results of Banana dataset when varying capacity (quotient   |     |

|   |      | bits) and tag bits (remainder bits) of Quotient WiSARD               | 26  |

|   | B.7  | Accuracy results of Diabetes dataset when varying capacity, number   |     |

|   |      | of tags (entries) per bucket and tag bits of Cuckoo WiSARD 12        | 27  |

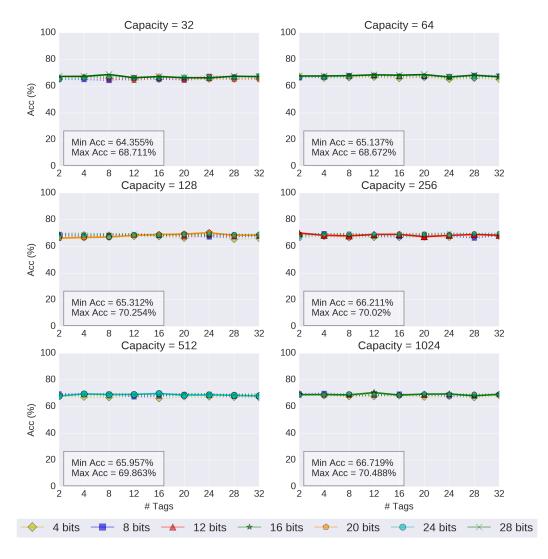

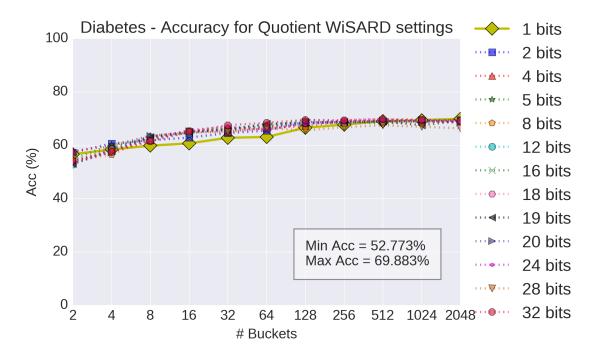

| B.8 Accuracy results of Diabetes dataset when varying capacity (quotient    |

|-----------------------------------------------------------------------------|

| bits) and tag bits (remainder bits) of Quotient WiSARD                      |

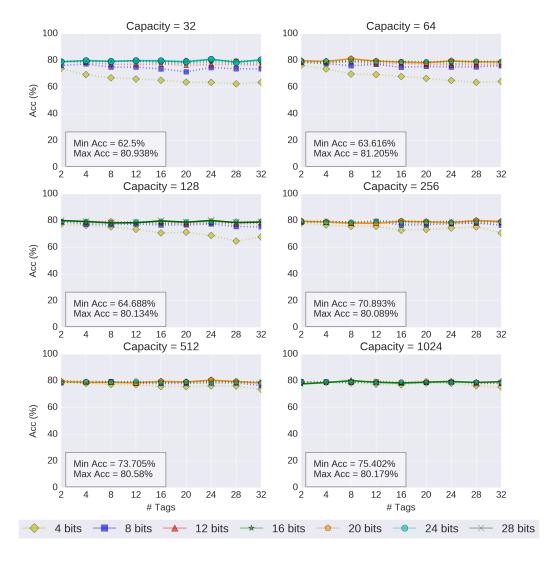

| B.9 Accuracy results of Ecoli dataset when varying capacity, number of      |

| tags (entries) per bucket and tag bits of Cuckoo WiSARD.                    |

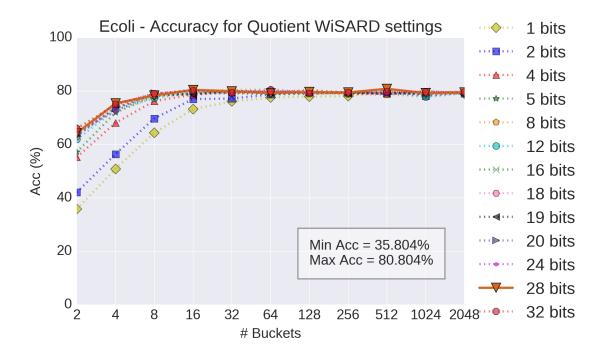

| B.10 Accuracy results of Ecoli dataset when varying capacity (quotient      |

| bits) and tag bits (remainder bits) of Quotient WiSARD 130                  |

| B.11 Accuracy results of Glass dataset when varying capacity, number of     |

| tags (entries) per bucket and tag bits of Cuckoo WiSARD.                    |

| B.12 Accuracy results of Glass dataset when varying capacity (quotient      |

| bits) and tag bits (remainder bits) of Quotient WiSARD 132                  |

| B.13 Accuracy results of Iris dataset when varying capacity, number of tags |

| (entries) per bucket and tag bits of Cuckoo WiSARD                          |

| B.14 Accuracy results of Iris dataset when varying capacity (quotient bits) |

| and tag bits (remainder bits) of Quotient WiSARD                            |

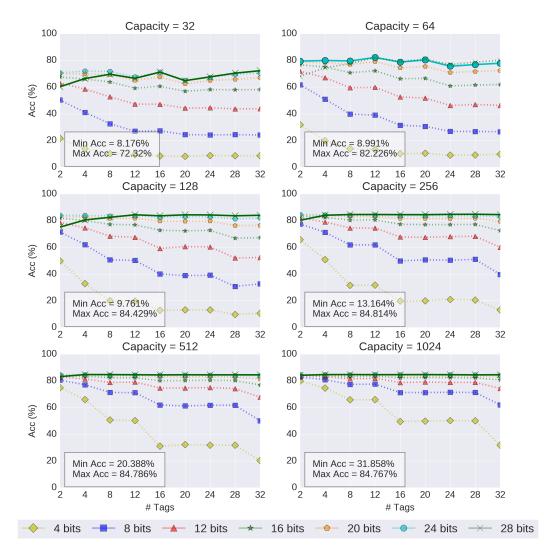

| B.15 Accuracy results of Letter dataset when varying capacity, number of    |

| tags (entries) per bucket and tag bits of Cuckoo WiSARD 135                 |

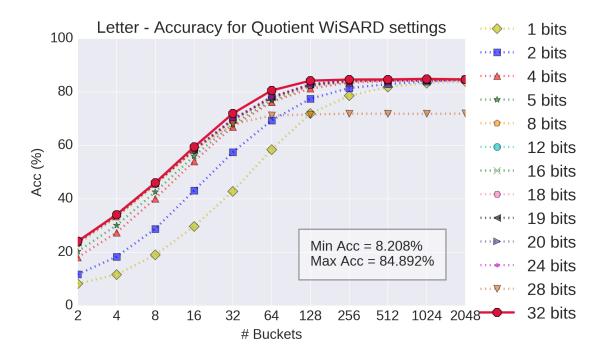

| B.16 Accuracy results of Letter dataset when varying capacity (quotient     |

| bits) and tag bits (remainder bits) of Quotient WiSARD 136                  |

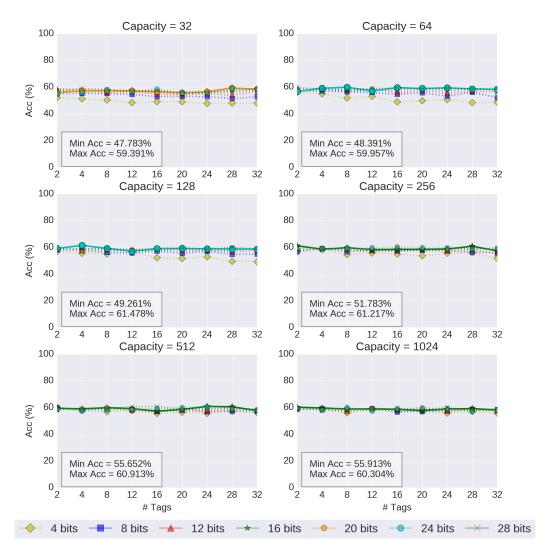

| B.17 Accuracy results of Liver dataset when varying capacity, number of     |

| tags (entries) per bucket and tag bits of Cuckoo WiSARD 137                 |

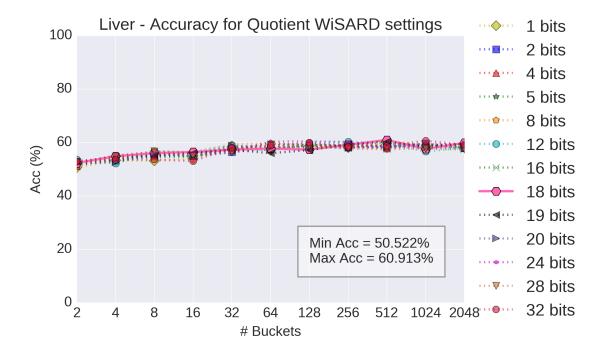

| B.18 Accuracy results of Liver dataset when varying capacity (quotient      |

| bits) and tag bits (remainder bits) of Quotient WiSARD 138                  |

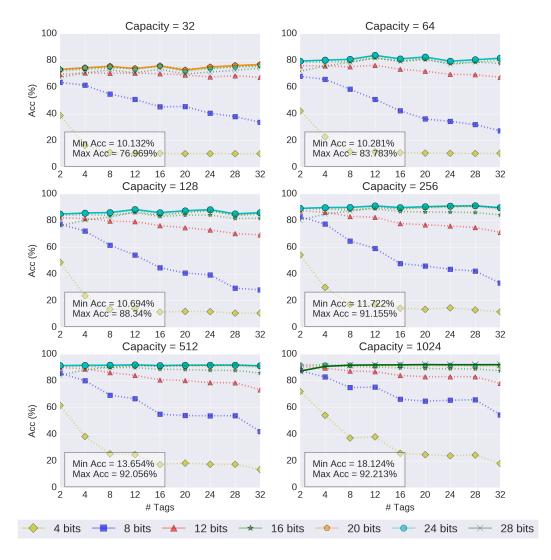

| B.19 Accuracy results of MNIST dataset when varying capacity, number        |

| of tags (entries) per bucket and tag bits of Cuckoo WiSARD 139              |

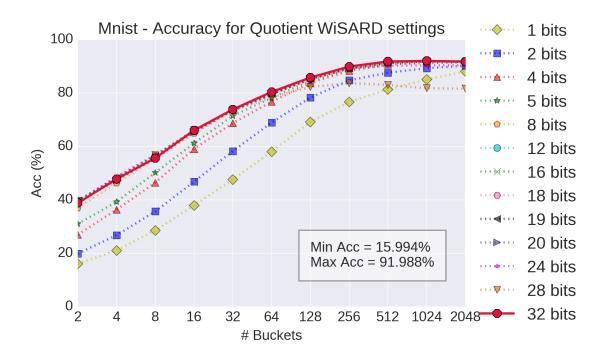

| B.20 Accuracy results of MNIST dataset when varying capacity (quotient      |

| bits) and tag bits (remainder bits) of Quotient WiSARD 140                  |

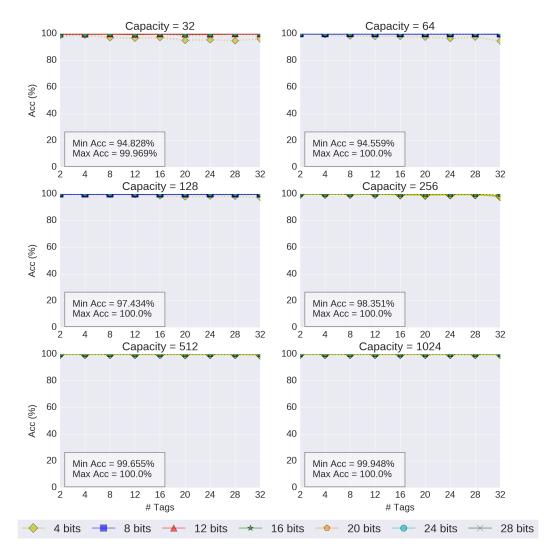

| B.21 Accuracy results of Mushroom dataset when varying capacity, number     |

| of tags (entries) per bucket and tag bits of Cuckoo WiSARD 141              |

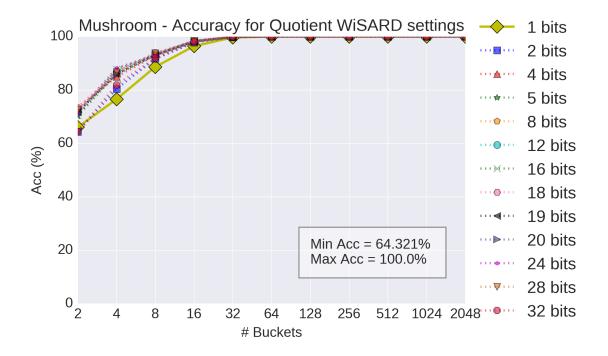

| B.22 Accuracy results of Mushroom dataset when varying capacity (quo-       |

| tient bits) and tag bits (remainder bits) of Quotient WiSARD 142            |

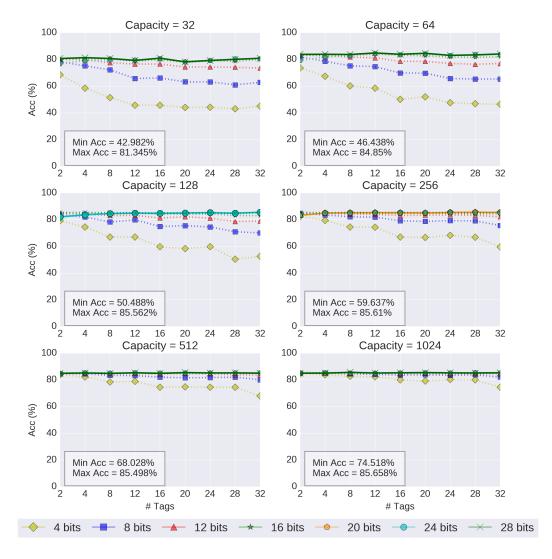

| B.23 Accuracy results of Satimage dataset when varying capacity, number     |

| of tags (entries) per bucket and tag bits of Cuckoo WiSARD 143              |

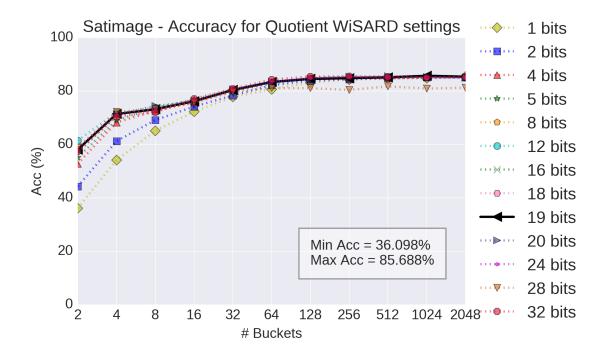

| B.24 Accuracy results of Satimage dataset when varying capacity (quotient   |

| bits) and tag bits (remainder bits) of Quotient WiSARD 144                  |

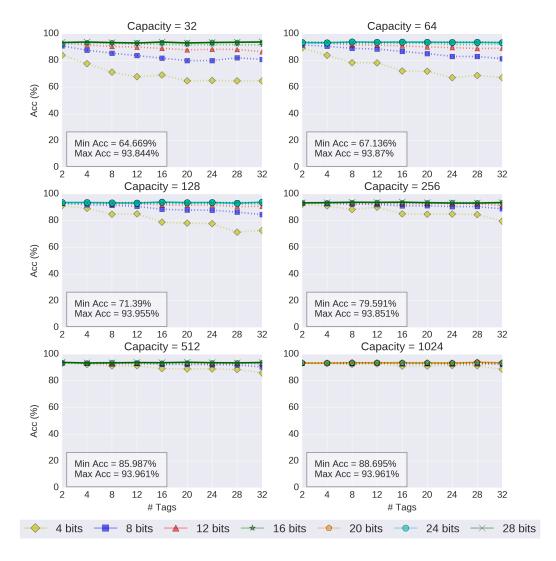

| B.25 Accuracy results of Segment dataset when varying capacity, number      |

| of tags (entries) per bucket and tag bits of Cuckoo WiSARD 145              |

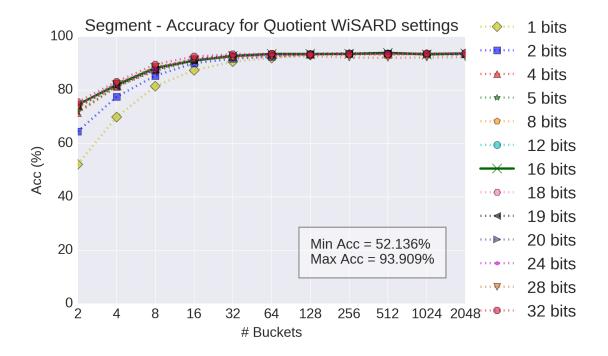

| B.26 Accuracy results of Segment dataset when varying capacity (quotient    |

| bits) and tag bits (remainder bits) of Quotient WiSARD 146                  |

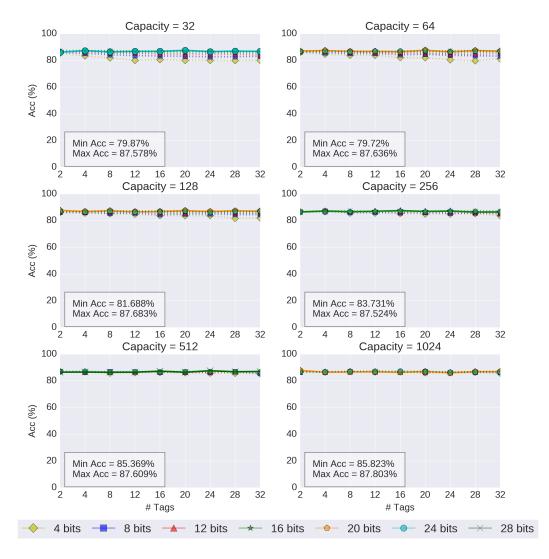

| B.27 Accuracy results of Shuttle dataset when varying capacity, number of |

|---------------------------------------------------------------------------|

| tags (entries) per bucket and tag bits of Cuckoo WiSARD 147               |

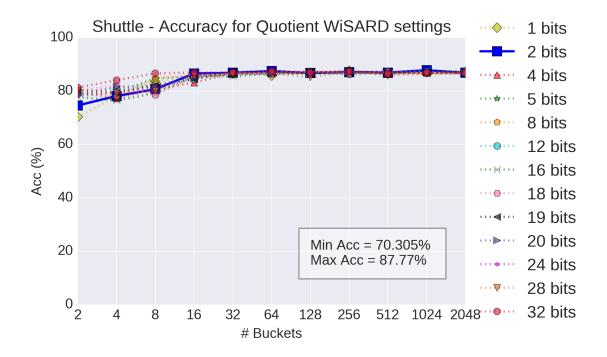

| B.28 Accuracy results of Shuttle dataset when varying capacity (quotient  |

| bits) and tag bits (remainder bits) of Quotient WiSARD                    |

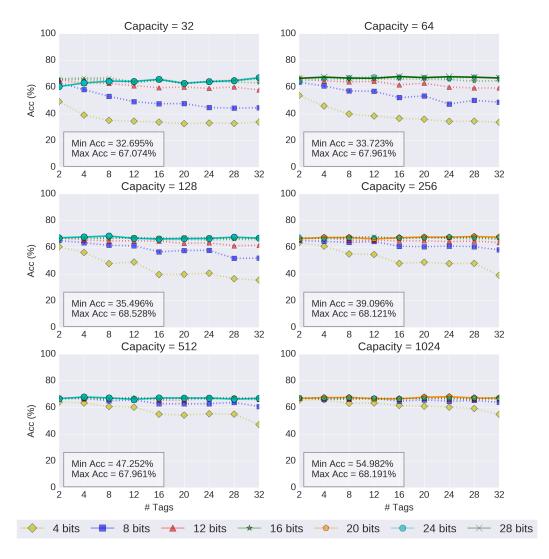

| B.29 Accuracy results of Vehicle dataset when varying capacity, number of |

| tags (entries) per bucket and tag bits of Cuckoo WiSARD 149               |

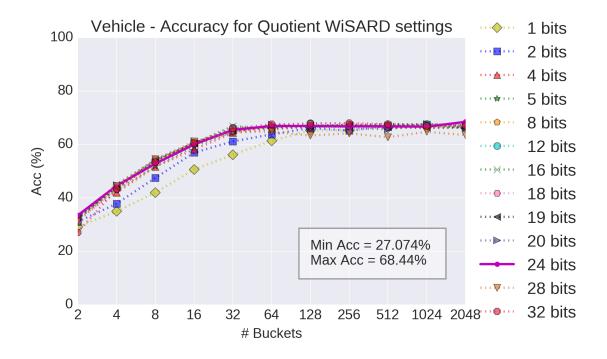

| B.30 Accuracy results of Vehicle dataset when varying capacity (quotient  |

| bits) and tag bits (remainder bits) of Quotient WiSARD                    |

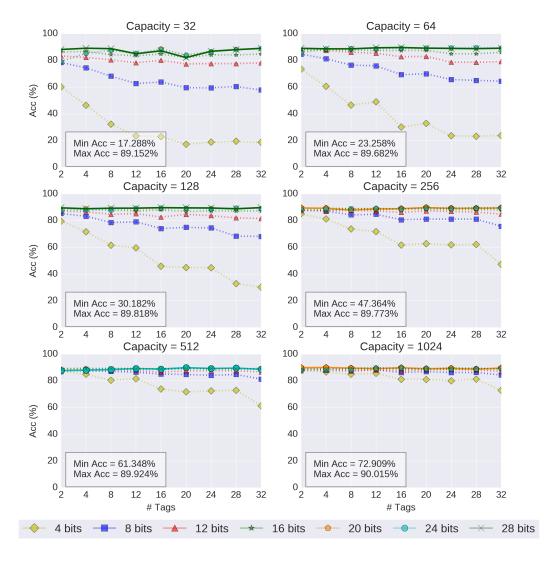

| B.31 Accuracy results of Vowel dataset when varying capacity, number of   |

| tags (entries) per bucket and tag bits of Cuckoo WiSARD 151               |

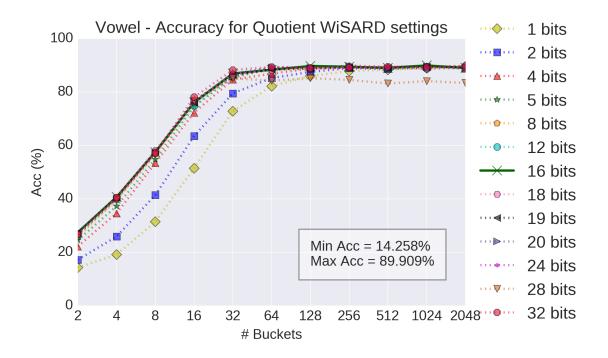

| B.32 Accuracy results of Vowel dataset when varying capacity (quotient    |

| bits) and tag bits (remainder bits) of Quotient WiSARD                    |

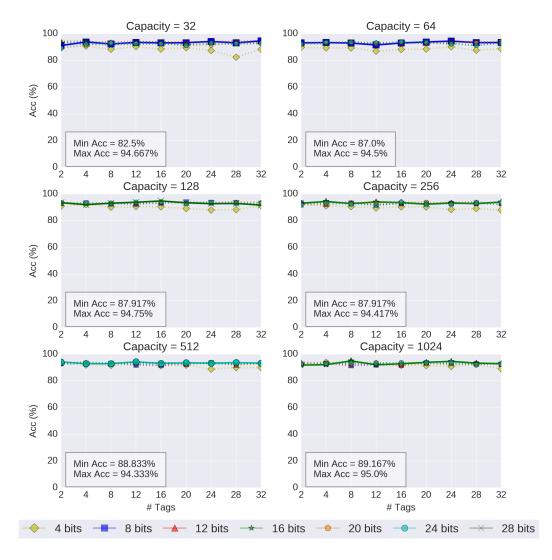

| B.33 Accuracy results of Wine dataset when varying capacity, number of    |

| tags (entries) per bucket and tag bits of Cuckoo WiSARD 153               |

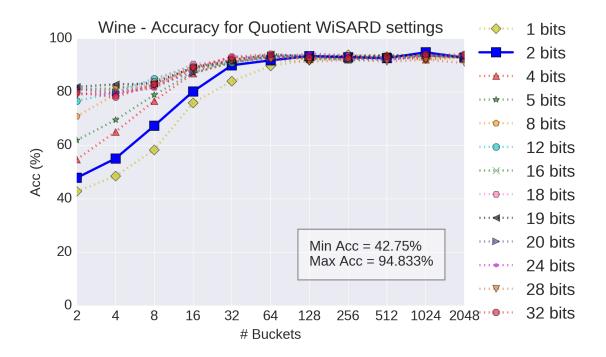

| B.34 Accuracy results of Wine dataset when varying capacity (quotient     |

| bits) and tag bits (remainder bits) of Quotient WiSARD                    |

# List of Tables

| 3.1 | WiSARD PUF design architectures for 64-bit challenges $\boxed{2}$   | 26 |

|-----|---------------------------------------------------------------------|----|

| 3.2 | Machine Learning results for WiSARD PUF variants 2                  | 31 |

| 3.3 | Reliable WiSARD PUF Architectures with 64-bit challenges $[3]$      | 35 |

| 3.4 | Gradient Boosting-based Machine Learning Accuracy for WiSARD        |    |

|     | PUF variants $[3]$ .                                                | 40 |

| 3.5 | Combinational Logic implementations of PUF with varying Entropy     |    |

|     | Sources.                                                            | 43 |

| 4.1 | MIH quality test results.                                           | 55 |

| 4.2 |                                                                     | 55 |

|     |                                                                     |    |

| 4.3 |                                                                     | 56 |

| 4.4 |                                                                     | 58 |

| 4.5 | Quality test results for all MIH versions.                          | 59 |

| 5.1 | Number of instructions and code size (bytes).                       | 78 |

| 6.1 | Meaning of metadata bit combinations from Quotient Filter           | 89 |

| 6.2 | Specification of binary classification datasets.                    | 95 |

| 6.3 | Specification of multiclass classification datasets.                | 95 |

| 6.4 | Accuracy, training time, testing time and memory results for Binary |    |

|     | Classification problems.                                            | 97 |

| 6.5 | Accuracy, training time, testing time and memory results for Multi- |    |

|     | class Classification problems.                                      | 98 |

| 6.6 | Accuracy, training time, testing time and memory results for Multi- |    |

|     | class Classification problems (continuation).                       | 99 |

| 6.7 | Accuracy and memory results for AMQ WiSARD compared to $50\%$       |    |

|     | false positive probability                                          | 01 |

|     |                                                                     |    |

| A.1 | Bit-counting consumption                                            |    |

| A.2 | Batcher's odd-even merge sort pipeline consumption                  | 13 |

| A.3 | Dataset configurations                                              | 15 |

| A.4 | Application utilization on the Pynq board                           | 17 |

## Chapter 1

## Introduction

The modern society is living the era of *ubiquitous computing* which is increasingly dependent on electronic devices in various areas such as banking, healthcare, autonomous car, smart homes, smart phones, supply chain and transportation. Progressively, more sensitive information are carried in these devices making security more expensive in terms of financial losses, safety and loss of privacy. Noteworthy examples are *Internet of Things* (IoT) architectures, including from traditional models where a central repository, such as a *Cloud* host, processes data collected by sensor to emergent solutions involving *Edge Computing* field where the data processing is distributed in end-devices. In both cases, data is exposed to integrity or confidentiality attacks during processing and the user has no control over it. The solely software-based security is not sufficient to protect those systems as advanced attacks can modify and corrupt them by exploring bugs on user software. Additionally, hardware support is required since the performance overhead from software-based security is non-negligible in some cases.

There are four fundamental concepts of information security to protect the storage and communication information:

- 1. **Confidentially** prevents unauthorized entities to access privileged information. Typically, it is ensured through encryption and decryption process where authorized entities have to use private keys to access the information.

- 2. **Integrity** verifies the completeness of data which can be corrupted when it is stored locally or used in a communication channel. A checksum is usually applied to provide this security.

- 3. Authenticity ensures the identity of the subject that requests or sends information. It relies on integrity in order to avoid any tampering information is undetected. The authenticity can be realized by some known information (e.g. a password), some restricted object (e.g. a smartcard) or some internal

characteristic (e.g. biometrics). Particularly, *Physical Unclonable Function* (PUF) is the latter category of authenticity as it uses physical fingerprint.

4. Availability allows the information is always available to be accessed. Communication channels and information systems are targeted from random faults and common attacks like denial-of-service attacks.

Over the last decade, many researches proposed hardware-assisted security solutions (also known as hardware-enhanced or hardware-enabled security) in order to enable trustworthy computing. HW-assisted security consists of technologies that provide security of higher layers of computer systems as firmware or software by using hardware components. It can enable security in BIOS, operating systems, hypervisors, or any other user-level application. It differs from hardware security, where solutions are restricted to protect physical devices or the hardware layer. Several architectural implementations of HW-assisted security solutions have been released by major vendors, like AMD, ARM, Intel, for a variety of scenarios, such as technologies for accelerated security-related processing, secure random number generation, memory bounds protection, isolated execution, video protection, or trusted computing. An overview of most relevant and promising HW-assisted security solutions are presented in [1].

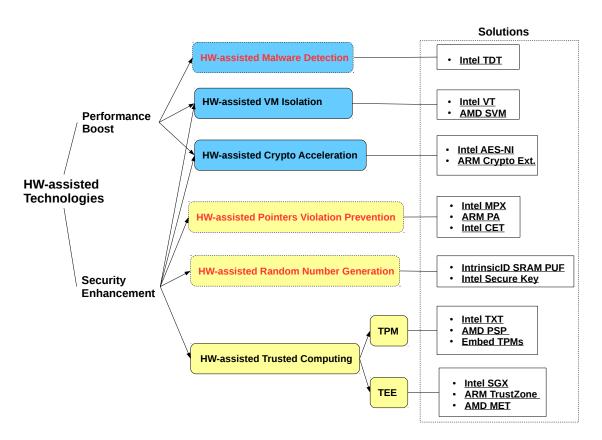

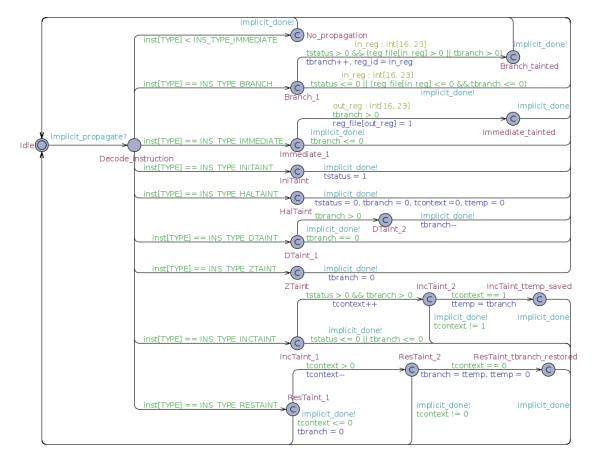

According to  $\square$ , HW-assisted security solutions can be grouped into *Performance Boost* and *Security Enhancement* technologies as depicted in Figure  $\square$ . In the former group, the solutions deploy hardware to improve the performance of security processing or to improve security as a side effect, whose can be categorized as follows:

- i) **Malware Detection** includes techniques for performance enhancement of anomaly detection processing;

- ii) Virtual Machine (VM) Isolation increases the performance in virtualized systems protecting them against attacks as hyperjacking [5], side-channel [6] or DMA attacks [7];

- iii) Cryptographic Acceleration embraces mechanisms to speed up performance of cryptographic processing;

In the latter group, the technologies use hardware to support security, which is categorized as:

i) Pointers Violation Prevention makes the system robust against Code-Reuse Attacks (CRA) such as ROP [5] or JOP [9], control flow hijack or buffer overflow attacks [10];

- ii) Random Number Generation prevents attacks to the cryptographic schemes

[11] that try to predict the randomly pattern of generated numbers used as digital signatures;

- iii) Trusted Computing ensures protection of data-in-use using a physically separated hardware from CPU as Trusted Platform Module (TPM) or extra hardware integrated in the CPU like Trusted Execution Environment (TEE). It protects system against a subset of physical attacks like bus sniffing, or software ones like code-injection [12] or run-time attacks such as Iago [13];

Figure 1.1: Category of HW-assisted security technologies [1]. This thesis contributes with optimization studies of solutions used in technologies classified in redcolored groups.

Cryptography relies on a secret key from storage system to protect the transmitted information. Conventionally, the key is stored in non-volatile memory (NVM) which is exposed by various security vulnerabilities of hardware primitives. There are demonstrations that an attacker with physical access to the storage can set up numerous attacks on it as side-channel attacks such as power measurement, semiinvasive attacks such as fault injection by over-clocking and invasive attacks such as decapsulation analysis to obtain information into storage [14, 15].

PUFs have emerged as appealing approach to protect secret keys and create device unique fingerprint or cryptographic key for confidentially, integrity and authenticity [15–17]. The main property of PUF is unclonability which relies on physically disorder system and impedes even the manufacturer to duplicate or clone the internal disorder circuits. It is possible due to the complex manufacturing fabrication of Integrated Circuits (IC). In theory, PUFs are secure against invasive attacks and distinct from each other.

Once authorized users have access to confidential data, there is no privacy guarantees that data cannot be leaked in subsequent computations. For example, Android users decide to grant personal information access (e.g. location, contacts, photos) to trusted app, but they have no assurance that the permissions will not be used to leak their sensitive information. To deal with this problem, there are some techniques developed to provide secure information flow, through either static analysis, where the source code or binary code is examined without executing it, or dynamic analysis which collects flow information during its execution.

Dynamic Information Flow Tracking (DIFT) have been established as promising platform to combat a wide range of security attacks [18]. The idea of DIFT is to tag (taint) an initial untrusted data and track its propagation during runtime. Data derived from untrusted data are also tagged and if any tagged data is used in unsafe operations, then an alarm is raised to block its execution. Initially, DIFT has been focused on explicit flow propagation which is related to data dependencies expressed by assignments. However, it has been demonstrated that an adversary can insert implicit flows based on control dependencies to execute evasion attacks [19].

Summing up, PUF and DIFT are effective mechanisms of HW-assisted security that improve security in ubiquitous environments which encompass constrained devices in terms of privacy and resources. As categorized in Figure 1.1, PUF belongs to the group of **HW-assisted Random Number Generation** and DIFT can be applied as technology for **HW-assisted Malware Detection** and **HWassisted Pointers Violation Prevention**. Although they have been improved by extensively researches, there are still untreated security flaws and unsolved problems which demand new approaches and techniques to achieve the desired PUF and DIFT systems.

## **1.1** Contribution

This thesis proposes novel techniques related to PUF and DIFT fields in order to harden them as HW-assisted security technologies. As consequence of those research investigations, this work explore *Weightless Neural Network (WNN)* model as feasible HW-assisted security solution and use *Multi-Index Hashing* (MIH) data structure for similarity search problem on ubiquitous environment. The main contributions are listed below:

- Various novel PUF designs based on WNN are proposed with the aim of increasing their resistance against machine learning attacks. It is demonstrated that the architecture of neural networks can also be used to achieve security with low resource overhead.

- Robust and reliable PUF designs are proposed by extending the WNN PUFs. An initial entropy source is employed to create a near-ideal PUF in terms of reliability.

- Online techniques are developed to optimize a high-volume PUF testing solution based on MIH. The methods are proposed to reduce the storage space without negatively impact the performance.

- A new co-processor design to accelerate MIH operations is elaborated. It is evaluated in the similarity search problem on in-situ environment with low-cost FPGA.

- A novel DIFT technique is proposed to support implicit flows propagation, including scenarios with multiple nested branches. A formal verification is provided to prove its hardware design correctness. Moreover, it is practical to extend any DIFT mechanism that only supports explicit flow propagation.

- A restricted rule of implicit taint propagation is analyzed in order to increase the precision of DIFT mechanism. It reduces the number of data that are erroneously tagged during implicit propagation.

- New WiSARD (a simple WNN model) models based on *Approximate Membership Query* (AMQ) data structure are proposed. These models reduce the memory resources while improving the generalization capabilities of the WiS-ARD. Furthermore, AMQ models are robust as even in cases with high false positive cases they achieve good accuracy results. That fact indicates them as interesting solutions to provide high reliability in case of transient faults occurrences.

## 1.2 Thesis outline

The remainder of this thesis is organized as follows: Chapter 2 introduces the relevant concepts related to PUF, DIFT and WNN that are required to understand the other Chapters. Then, Chapter 3 presents many new PUF designs utilizing WNN which are resistant against machine learning attacks and proposes an extension for them to offer 100% of reliability by using a reliable entropy source. Chapter 4 defines

techniques to optimize a design-for-test solution for testing PUF using MIH. Chapter <sup>[5]</sup> proposes a novel low resources DIFT technique to extend explicit DIFT with implicit flow propagation and describes a new implicit taint propagation rule to prevent data from being incorrectly tagged. Chapter <sup>[6]</sup> analyses new WiSARD models based on probabilistic data structures that perform membership query operations. Finally, Chapter <sup>[7]</sup> concludes this thesis and resumes the ideas for future works. Appendix <sup>[A]</sup> identifies the data-intensive MIH operations that can be efficiently implemented on hardware for future PUF testing implementation and evaluates the low-cost co-processor implementation for similarity search on in-situ environment. Appendix <sup>[B]</sup> presents complementary experiments for AMQ WiSARD models using Cuckoo filter and Quotient filter. Appendix <sup>[C]</sup> shows the list of publications submitted and accepted during the development of this thesis.

## Chapter 2

## Background

This chapter provides the relevant background information for better understanding of the addressed subjects in this thesis. The main topics are PUF, Dynamic Information Flow Tracking and Weightless Neural Network, while the remaining subjects are related to the concepts applied in the proposed solutions discussed later in this work.

### 2.1 PUF

Physically Unclonable Functions (PUFs) are circuits introduced by Pappu et al. as one-way functions which map inputs (challenges) to unique outputs (responses) [16]. PUF relies on manufacturing process variations where not even the manufacturer is able to clone or duplicate the physical components from one chip to another. It is possible due to the complexity of the current Integrated Circuits (IC) fabrication. Hence, in theory, PUFs are always distinct and unique between themselves and cannot be reconstructed by invasive attack. Such peculiar unclonability characteristic points out PUFs as a promising technology to protect secret keys.

#### 2.1.1 Classification of PUFs

PUF can be classified into Weak PUF and Strong PUF according to the supported number of *challenge-response pairs* (CRPs). That classification also establishes the applications that each type of PUF is properly used.

#### 2.1.1.1 Weak PUF

PUFs are classified into Weak PUF when the number of CRPs is limited, in some cases only a single challenge. That limitation makes Weak PUF unfeasible for authentication systems, as an adversary can easily collect all its CRPs to replicate it. On the other hand, Weak PUFs are better at generating and storing secret keys than non-volatile memory (NVM), since they offer harder accessibility from any invasive attacks to leakage internal information out. The generated secret keys are not secure against the side channel attacks. Therefore, the use of Weak PUF needs external countermeasures to hide it from applications that use its secret keys.

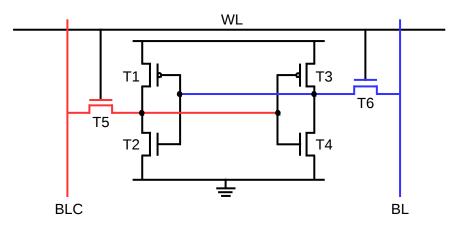

Weak PUF implementations based on SRAM cells have been studied extensively in previous researches [20] [21]. Each SRAM cell is an embedded memory consisting of six transistors as shown in Figure [2.1] two cross coupled inverters (load transistors T1, T2, T3, T4) and two access transistors (T5, T6) connected to the bit-lines (BLC and BL) and word-line signal (WL). When a SRAM cell is started-up, its state will transition to hold either 0 or 1 depending on noise and mismatch in the intrinsic process variations that are not controllable by the manufacturing process. By obtaining the values from the random stable states (0 or 1) of a SRAM array, it is possible to compose a physical fingerprint which in turn is used to create keys and identifiers. On the enrollment phase, the generated key is recorded as the correct key so that it will be matched to the next obtained keys whenever SRAM PUF is powered-up. Due to the intrinsic process variations, the power-up operations are affected by noise leading to the generation of incorrect keys and, consequently, the unreliability of the circuit. Some solutions to improve the reliability of Weak PUFs are discussed in Section [2.1.3]

Figure 2.1: Example of six transistors at SRAM cell.

#### 2.1.1.2 Strong PUF

Unlike Weak PUF, Strong PUFs support an exponential number of CRPs and implement a complex mapping between challenges and responses. Even an adversary has control over PUF, it is practically impossible to store all CRPs and predict the responses from the PUF. That complexity makes Strong PUF resistant to model building attacks and propitious for authentication applications using a Challenge Response protocol. In the authentication, a set of CRPs from each PUF is previously stored into a secure database. When an authenticity is requested, a set of random CRPs from the database is applied to the PUF and the generated responses are compared to the stored responses in order to verify the result of the authentication. Once CRPs are chosen from database, they will never be reused for preventing man-in-the-middle attacks.

Unfortunately, one of the earliest Strong PUF implementations, termed Arbiter PUF [22], did not expose the prominent properties and could be easily cloned [23]. Proposed alterations to increase resistance, like using XOR operations, still failed to offer the promised unclonability [23]. Different from digital PUFs, analog circuits were proposed to harness non-linear behavior of CMOS transistors under certain operating conditions as a solution to increase the attack resistance of Strong PUFs. Current-based [24, [25] and voltage-based techniques [26] have been shown to be successful against Support Vector Machine (SVM) learning algorithm, which was able to break the previous digital PUF implementations. However, Vijayakumar *et al.* reported a new class of machine learning algorithms based on ensemble meta-algorithms that could effectively model even the analog PUFs with great accuracy [27]. Further, side-channel and fault-based attacks have also been explored to raise the modeling accuracy to break PUFs [28-30].

Other studies have been focused in the application of Weak PUF to construct Strong PUFs. Holcomb and Fu proposed a Strong PUF using SRAM cells organized in a column of a memory block which are pre-loaded with values based on an input challenge. To produce the final response, the PUF output is generated by reading multiple cells in a column at once to create a contention at the sense amplifier [31]. Bhargava *et al.* created a Strong PUF where the response is the cipher text generated by the AES block and the challenges are the plain text input which are extracted as a stable secret key from Weak PUFs [32]. Chapter [3] presents a reliable Strong PUF implementation based on neural network by utilizing similar concept of generating stable Weak PUF bits.

#### 2.1.2 Ideal Properties of PUFs

The PUF implementations are built under circuits that harness the manufacturing variations and they differ by their physical implementations associated with the number of CRPs. To guarantee the quality of a PUF chip, it has to exhibit three ideal properties: high *uniqueness*, high *reliability* and high *security*.

#### 2.1.2.1 Security

Security is the most important property of PUF directly related to unclonability and unpredictability requirements. It ensures the PUF are impossible to be physically cloned and built by software models that mimic the circuit. For Weak PUFs, it is implies to prevent the keys generated from PUF are discovered by external systems. In case of Strong PUF, the security depends on the complexity of challenge-response mapping. PUFs with simple mapping are easily predicted by software executing machine learning algorithms that creates a PUF model identical to the original circuit.

#### 2.1.2.2 Uniqueness

As PUFs produce unique CRPs, the uniqueness determines how different the responses across distinct chips are. If PUFs generate similar responses, their challengeresponse mappings are not ideal, straightly impacting the desired unclonability constraint. Therefore, high uniqueness is important to complement the security by defining the distinguishability of challenge-response mappings and discarding similar chips.

#### 2.1.2.3 Reliability

PUFs might produce wrong responses under noise and certain environmental conditions such as supply voltage variations and temperature variations. Reliability is the property that indicates if the responses are stables along any such conditions. In Weak PUFs, reliability is critical since they are used to create secret keys or unique identifiers. To improve reliability, error-correction based solutions are applied to circuit by increasing the cost of design as cited in Section 2.1.3. The reliability issues in Strong PUFs can be mitigated by the fact that they have an exponential number of CRPs available, where a threshold of acceptable responses can be set for practical use in authentication. Increasing the threshold level also increases the number of CRPs needed to authenticate a device in real-world scenarios, resulting in decreasing in PUF reliability and raising in resource costs 33.

### 2.1.3 Weak PUF Realibility

As presented in Section 2.1.1.1, reliability is a crucial property for Weak PUFs enabling them to generate stable secret keys. To ensure Weak PUF reliability, techniques involving *error correcting-codes* (ECC) and *fuzzy extractors* have been extensively explored [34–38]. Nevertheless, such approaches use a large number of initial Weak PUF bits to derive the final stable key and this number increases with

the inherent error rate of the Weak PUF 34. Consequently, the implementation of ECC in hardware and the required number of Weak PUFs bits result in a large resource costs.

Other alternatives to costly ECC have been proposed, such as a simple circuitbased error correction using Temporal Majority Voting (TMV) [39, 40] and TMV improved by Vijayakumar *et al.* using Up-Down counters to correct twice the error rate, that is the correction rate comparable to other TMV implementation [41].

Modifications to SRAM Weak PUF circuit design have been explored to mitigate the error correction required and increase Weak PUF reliability [42]-44]. New devices like Magnetic Tunnel Junction (MTJ) have also been studied to build reliable Weak PUFs [45]. Accelerated aging mechanisms have also been utilized to improve the reliability of Weak PUF [40], [46].

The wealth of techniques available to improve the reliability of Weak PUFs allows to create an efficient implementation that yields the desired number of stable bits for later to be used in neural networks to realize robust Strong PUFs as proposed in Section 3.3

## 2.2 WiSARD

Weightless Neural Networks (WNNs) [47] are abstract neuron models which represent a neuron as Random Access Memory (RAM) node. These models offer an attractive practical solution to pattern recognition and artificial consciousness applications, due to their binary representation which able to implement such networks using existing memory resources in devices.

WiSARD (Wilkie, Stoneham and Aleksander's Recognition Device) is a multidiscriminator WNN model proposed in the early 80's [48] and inspired by the n-tuple classifier [49]. It is the pioneering WNN distributed commercially which provides simple and efficient implementation enabling to deploy learning capabilities into real-time and embedded systems.

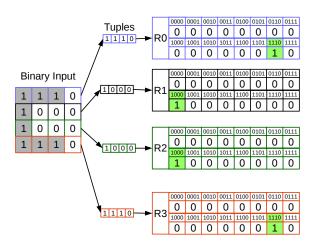

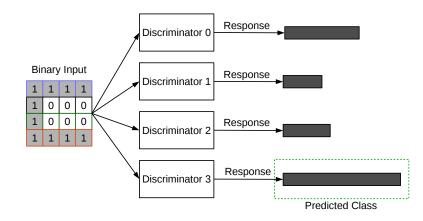

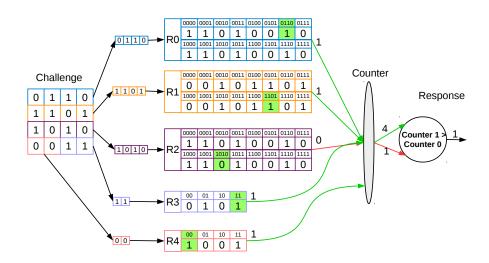

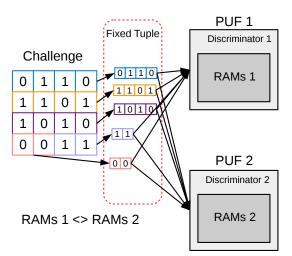

Each class is represented by a structure called *Discriminator*, which comprises of a set of RAMs, composed of one-bit words, to store the relevant knowledge during the *training* phase which will be used during the *classification* phase. Before sending the input data to the discriminators, they need to be converted in a binary format using a transformation which depends on the data type. A binary input of  $N \cdot M$ bits is split in N tuples of M bits. Each tuple  $n, n = 1, \ldots, N$ , is a memory address to an entry of the *n*-th RAM. Each Discriminator consists of multiple RAM blocks (= N), each containing  $2^M$  locations. A pseudo-random mapping connects the tuples to the binary input and each Discriminator has its own pseudo-random mapping. A WiSARD system can have any number of such Discriminators and, hence, any number of desired classes.

Figure 2.2: Example of training in WiSARD.

Figure 2.3: Example of testing operation in one WiSARD discriminator.

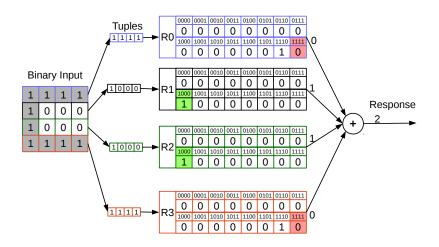

During the training phase, all RAMs of the Discriminators are initialized to zero (0). The training input is sent to the related Discriminator, where the accessed RAM positions are set to one (1) as illustrated in Figure 2.2. During classification, an input is sent to all Discriminators generating responses per discriminators by summing all accessed RAM values as shown in Figure 2.3. The Discriminator with the highest response is selected as representative class of the input as depicted in Figure 2.4. In both phases, the pseudo-random mapping from input to the tuples is the same for each discriminator.

The structure of WiSARD can be readily implemented in hardware using standard SRAM memory and address decoding to provide high generalization capabilities and real-time performance.

Figure 2.4: Example of testing operation to WiSARD select predicted class.

## 2.3 Dynamic Information Flow Tracking

Dynamic Information Flow Tracking (DIFT), also known as Dynamic Taint Analysis (DTA), is a security enhancement technique applied to prevent sensitive information leakage and to protect binary codes against malicious attacks such as buffer overflows **50**, **51** and SQL Injection **52**, **53** at runtime. DIFT associates a tag termed *taint* to each memory word (or byte) and register, allowing to track information flow through taint propagation and taint checks using certain rules. Generally, the initial step is to tag the data coming from untrusted sources. During instruction execution, the taint will propagate from source operands to the destination operand according to the data dependency characterizing an *explicit information flow*. Checking the tainted data ensures safe execution and when the check fails a security alarm is raised to invoke the taint analysis. Depending on the type of analysis, program validation can be performed either directly by the DIFT system, or can be inferred from its behavior. In this way, security attacks are detected and sensitive information is kept safe by identifying unsafe activities and stopping the process execution.

### 2.3.1 Under-tainting and over-tainting problems

The *under-tainting* problem occurs when a data is not marked as tainted in cases that should be marked. For example, *implicit flow propagation* can be used to skip the taint propagation in control dependencies. Implicit DIFT mechanisms avoid this problem by tracking correctly such implicit flows.

In contrast to *under-tainting*, the *over-tainting* problem is the case that data is erroneously marked as tainted. Various implicit flow tracking approaches have limitations regarding nested branches and loops which intensify the taint propagation originated from control-dependency flow.

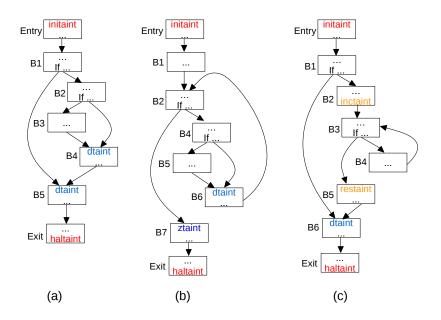

### 2.3.2 DIFT Designs

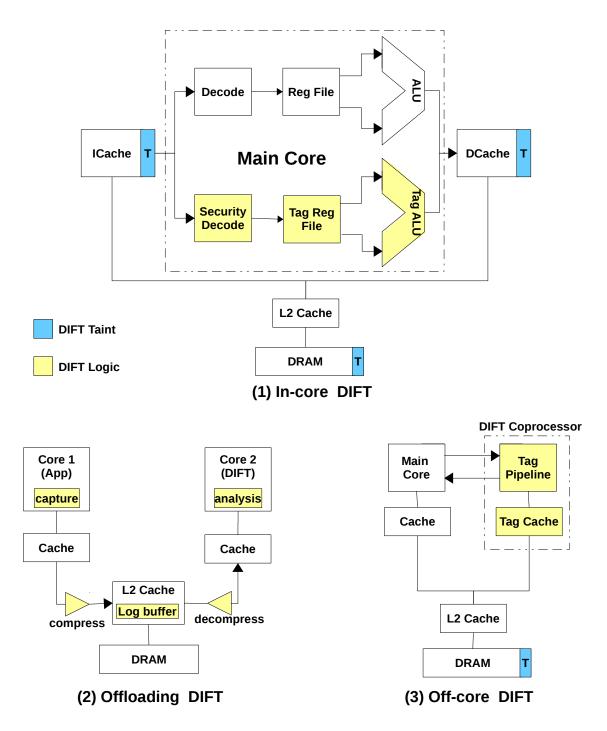

Figure 2.5: The three DIFT designs.

DIFT has been implemented in software [54-63] by using a binary instrumentation technique, that intercepts the program execution to insert extra instructions for tracking the tainted data at runtime, and hardware [51], [52], [64-71] by building a specialized circuit in order to reduce the performance overhead.

Figure 2.5 presents three hardware designs for supporting DIFT:

1. In-core design: DIFT logic is integrated in a general-purpose core by either

extending register file and memory resources, or adding specialized register file and cache to store the tags for data, respectively in the register and memory. Taint propagation and checking are performed in the processor pipeline which is extended to run in parallel with normal instruction execution. The performance impact is minimal in terms of clock cycles, but the required changes to the processor core may have a considerable negative impact on design and verification time. Most of the DIFT implementations are based on this approach [51], [52], [64].

- 2. Offloading design: DIFT functionality is performed by one core in a multicore chip while the application runs on another core. Although taint propagation and taint check policies are not implemented directly in hardware, the cores must still be modified to implement the synchronization scheme via system call between the application core and the DIFT core. The application core creates a compressed trace of executed instructions to communicate through a shared cache with the DIFT core, that decompresses the received trace in hardware before each tag execution. This design has been presented in [65] [66].

- 3. Off-core design: DIFT is implemented as a co-processor which has separated resources to manage the tags without any changes in the main core design. Synchronization between the main core and DIFT is needed to keep the correct tracking execution. Recent works have implemented DIFT as a co-processor [67+70].

### 2.3.3 Related Works